Semiconductor structure and forming method thereof

A semiconductor and morphology technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., can solve problems such as chip or device performance degradation, failure, substrate fragmentation, etc., and achieve feature size reduction , The thickness is uniform and dense, and the effect of avoiding substrate fragmentation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0039] As mentioned in the background art, when the TSV structure is formed in the prior art, it is easy to cause the substrate to break, or cause the performance of the chip or device to degrade, or even fail.

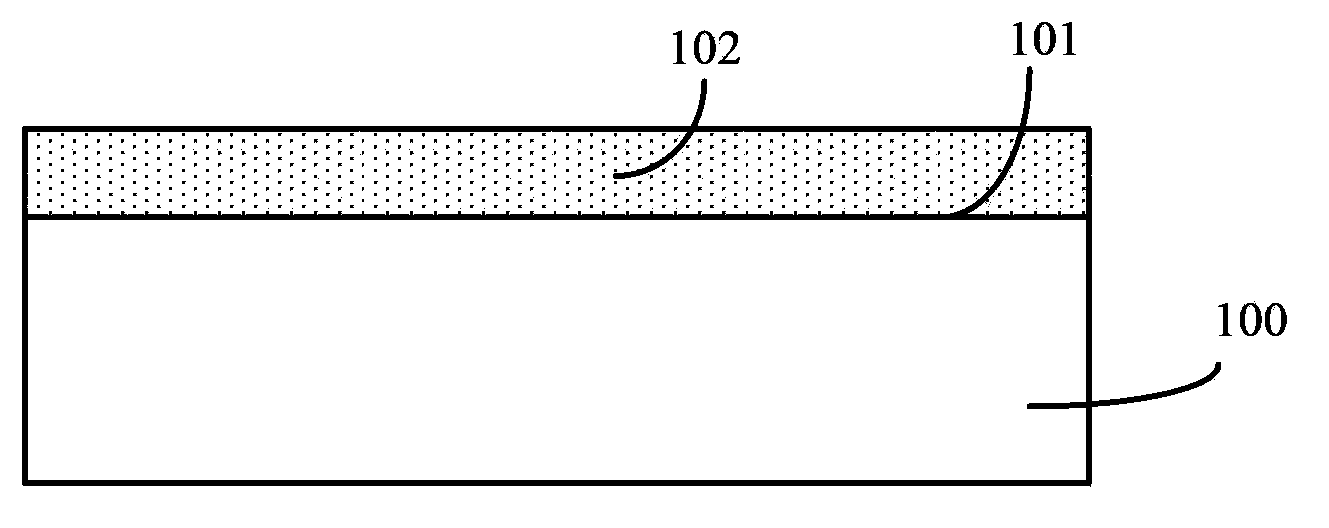

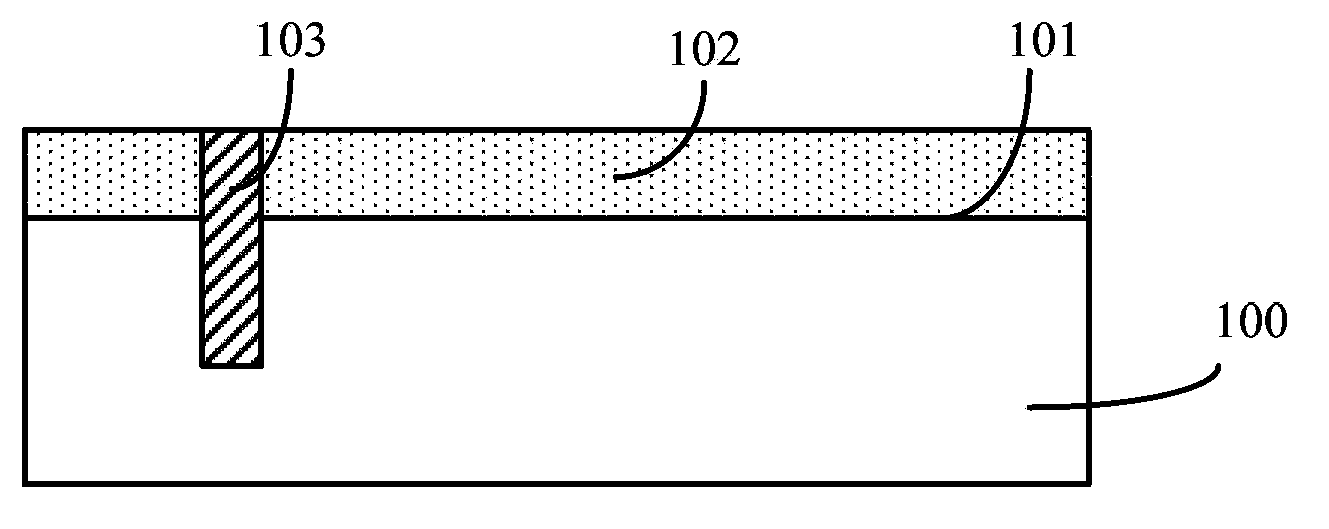

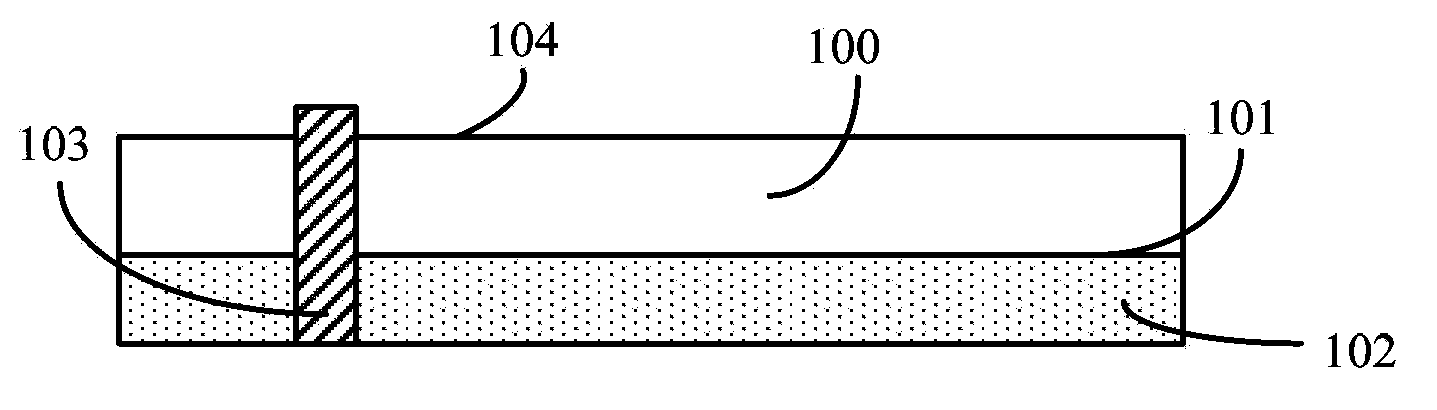

[0040] After research by the inventor of the present invention, please continue to refer to Figure 1 to Figure 3 , the conductive plug 103 is often made of copper; in addition, in order to electrically isolate the conductive plug 103 from the semiconductor substrate 100, an insulating layer is also formed between the conductive plug 103 and the semiconductor substrate 100, The material of the insulating layer is usually silicon dioxide. The thermal expansion coefficient of copper is 18ppm, the thermal expansion coefficient of silicon dioxide is 0.5ppm, and the thermal expansion coefficient of silicon substrate is 2.5ppm. Due to the difference in thermal expansion coefficient between copper, silicon dioxide and silicon substrate, and the thermal expansion coefficient o...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More