Patents

Literature

78results about How to "Difficult to penetrate" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Nano modified paint used for inner and outer wall

The main structure of said invented internal and external wall coating material respectively includes film-forming substance, dispersion medium, pigment filler and adjuvant, and its raw material formula is formed from (wt%) 35-55% of acrylic resin emulsion, 0.1-0.3% of dispersion moistening agent, 4-8% of titanium white powder, 4-8% of lithopone, 2-6% of talcum powder, 1.5-4.5% of nano SiO2, 1.5-4.5% of nano Tio2, 0.1-0.3% of pH regulating agent and 20-30% of water. The above-mentioned materials are stirred, ground and filtered so as to obtain the invented coating material with improved water-proofing property, contamination resistance, ageing resistance, UV ray resistance and bacteria-resisting property. Said coating material can be washed for above 11000 times, and its service life can be up to above 10 years.

Owner:刘尚文 +1

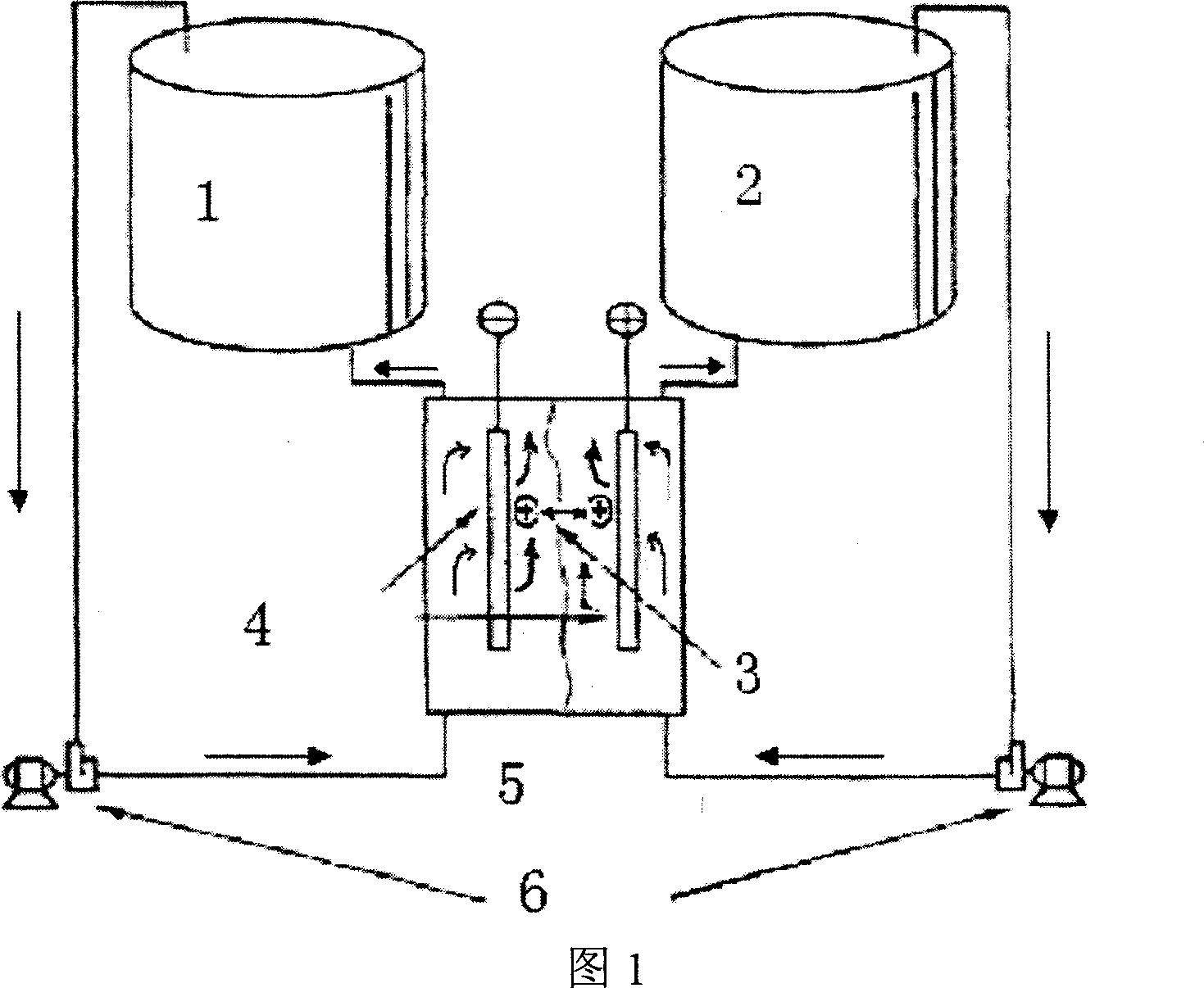

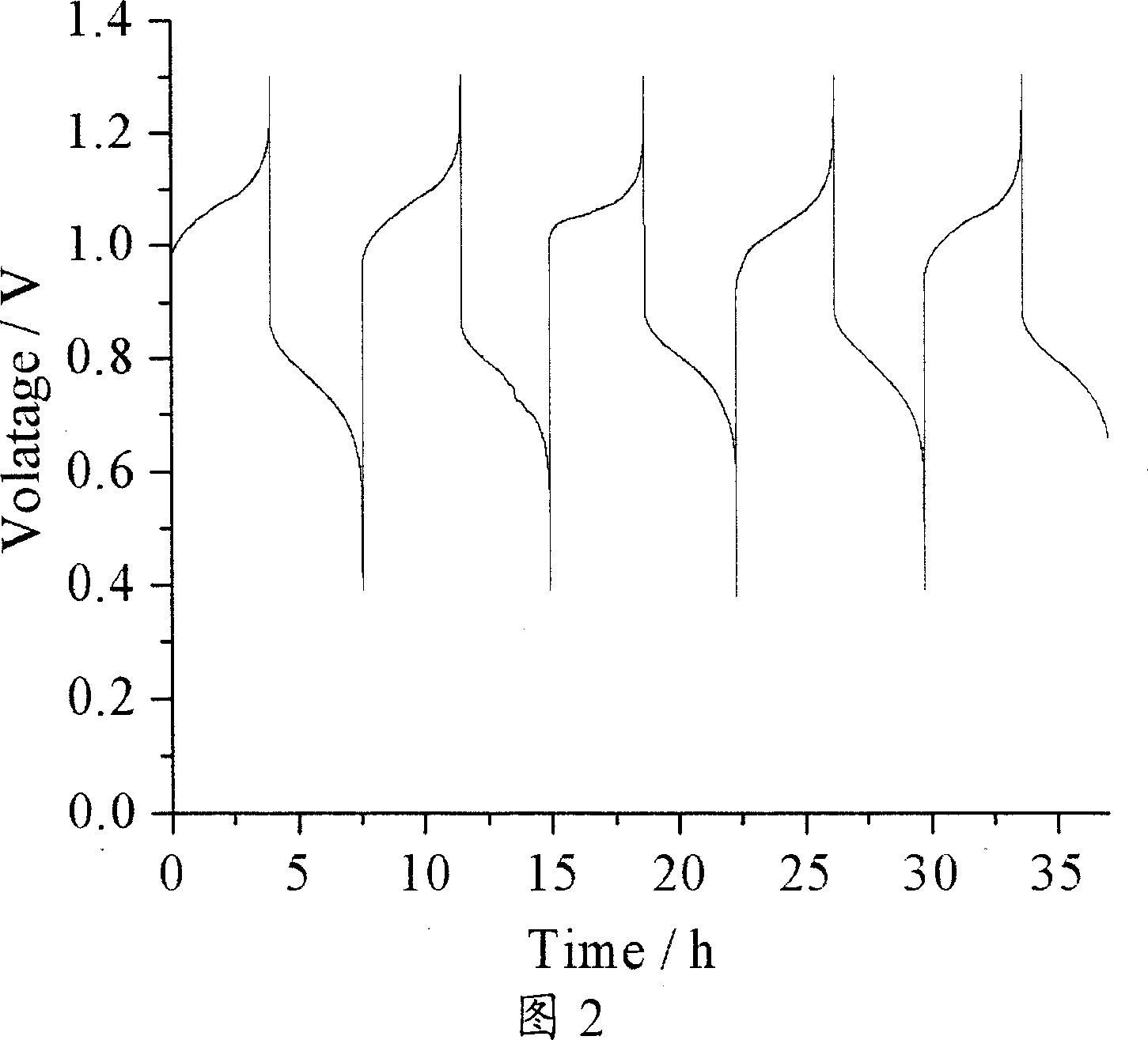

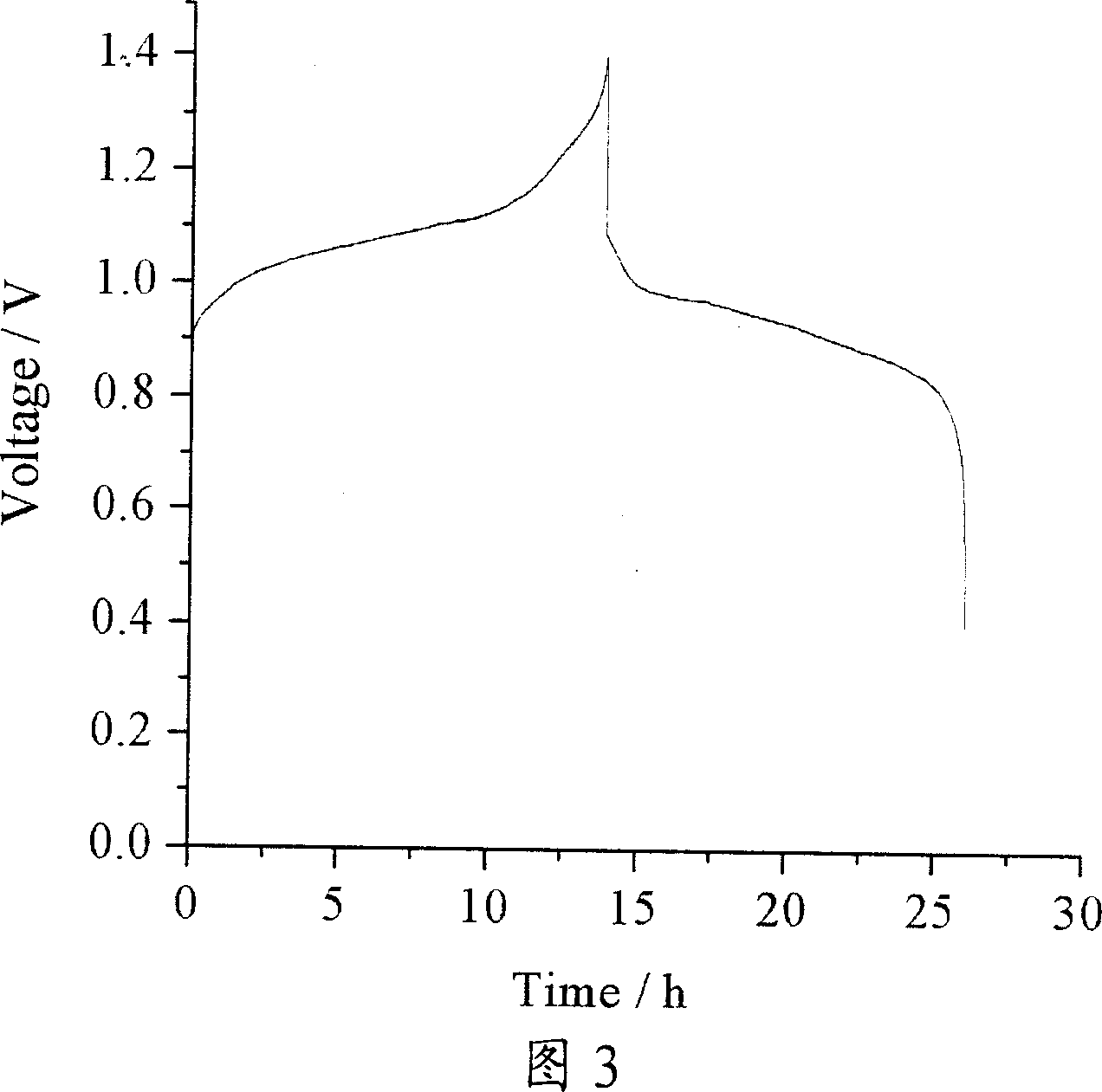

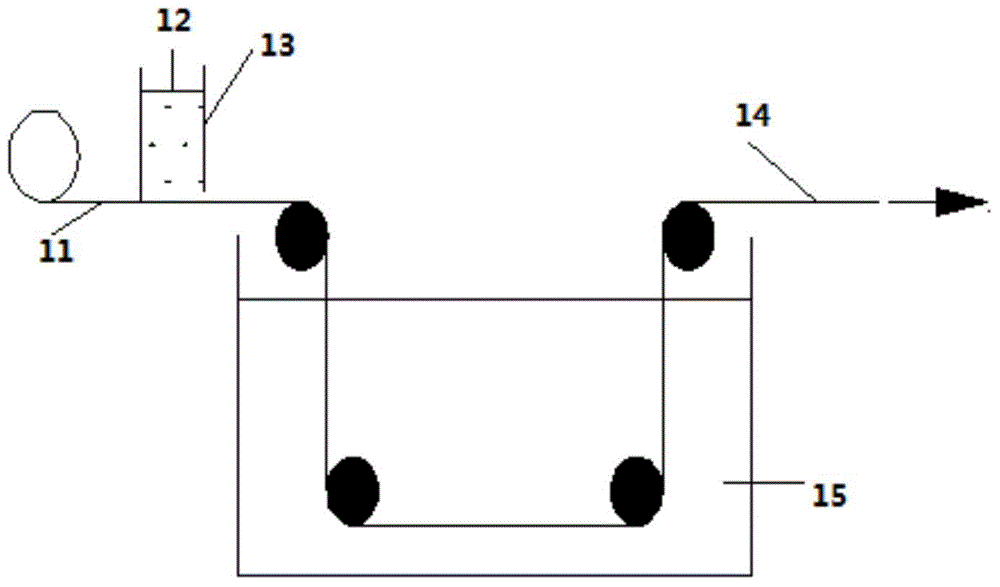

Iron composite/halogen electrochemical system for flow electric storage

InactiveCN101047261AReduce capacityImprove energy conversion efficiencyElectrolyte moving arrangementsCell electrodesElectricityHalogen

A Fe-matched matter-halogen electrochemical system used on liquid flow energy storage is prepared as separating positive / negative electrode electrolyte by positive ion exchange film and storing said electrolyte in external container, generating charge / discharge process by making oxidation / reduction reaction on inert carbon felt electrode through pump stream via battery, applying soluble Fe(III) / Fe(II) -matched matter oxidation / reduction electric pair as negative electrode and applying halogen oxidation / reduction electric pair as positive electrode.

Owner:DALIAN RONGKE POWER

Nano carrier for tumor photo-dynamics therapy (PDT) and preparation method thereof

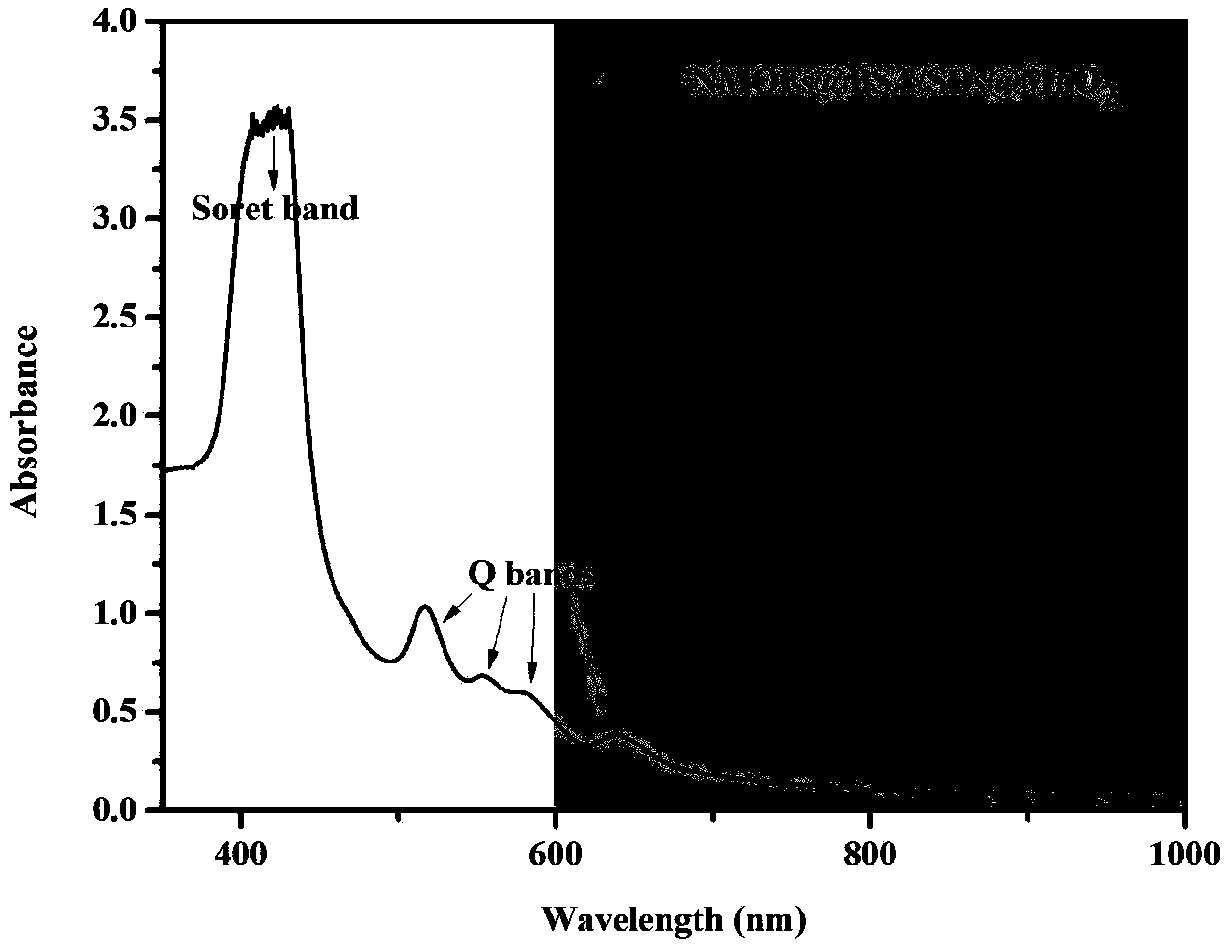

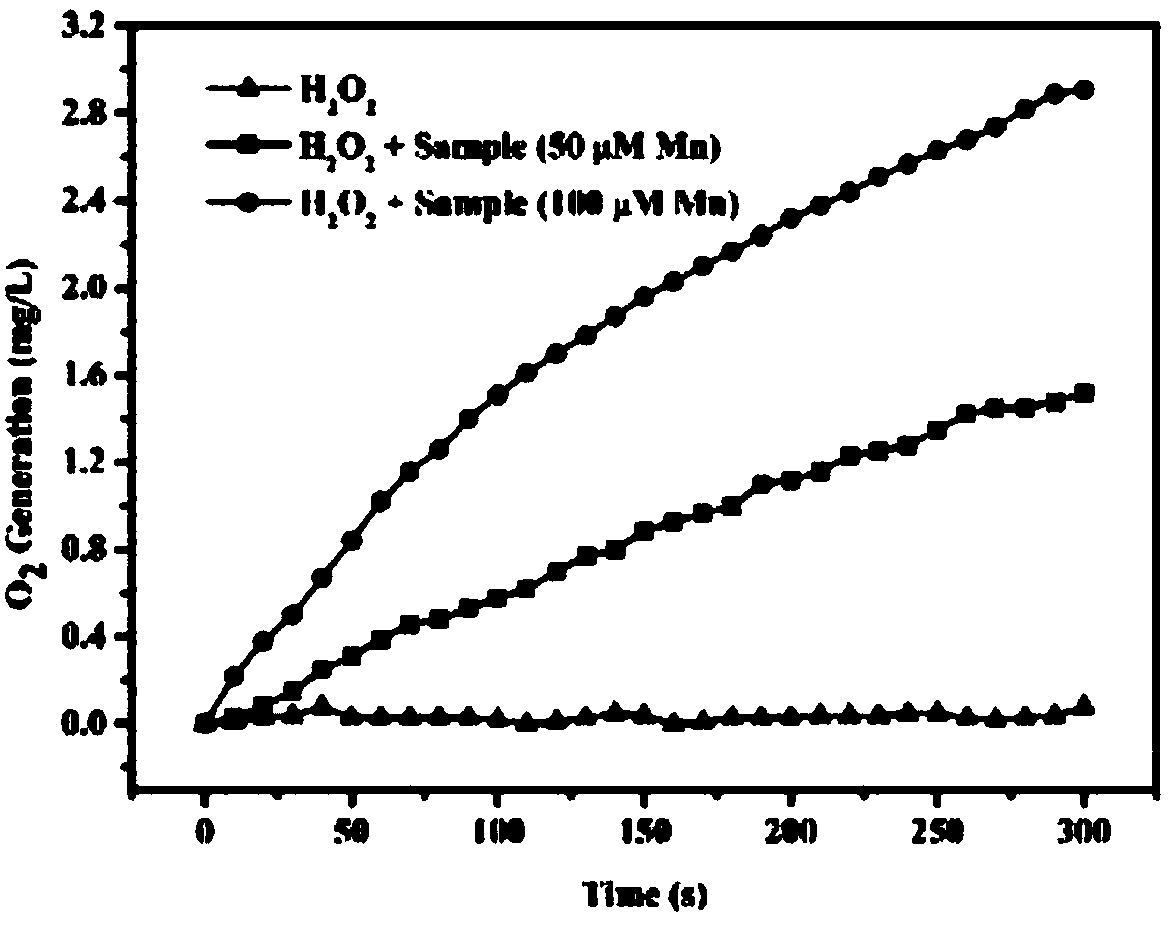

InactiveCN108939072AGood biocompatibilityIncrease oxygen contentOrganic active ingredientsPhotodynamic therapyAbnormal tissue growthDecomposition

The invention provides a preparation method of a nano carrier for tumor photo-dynamics therapy (PDT). According to the preparation method, Fe<3+> salts are dissolved in DMF, then a photo-sensitizer (TCPP) is added to obtain particles (NMOFs); then the particles are dispersed in water under the assistance of ultrasonic waves; crosslinking agents (EDC and NHS) are added; after the reactions betweenBSA and sulfadiazine (SDs) finish completely, dialysis is performed to obtain particles (NMOFs@BSA / SDs); then the particles are dispersed in distilled water, then Mn<2+> salts are added, the pH is adjusted, and finally dialysis is performed to obtain a carrier (NMOFs@BSA / SDs@MnO2). Nano metal organic framework particles are taken as the basis and coated by protein (BSA) and sulfadiazine (SDs); finally the particles are in-situ mineralized to obtain required particles; SDs can specifically recognize carbonic anhydrase of tumors and is capable of actively targeting the oxygen-deficient parts oftumors; MnO2 generated in mineralization can catalyze the H2O2 decomposition to increase the oxygen content of tumors; and the PDT efficiency is improved.

Owner:HUBEI UNIV +1

Application of water-soluble silicon quantum dots as drug carriers

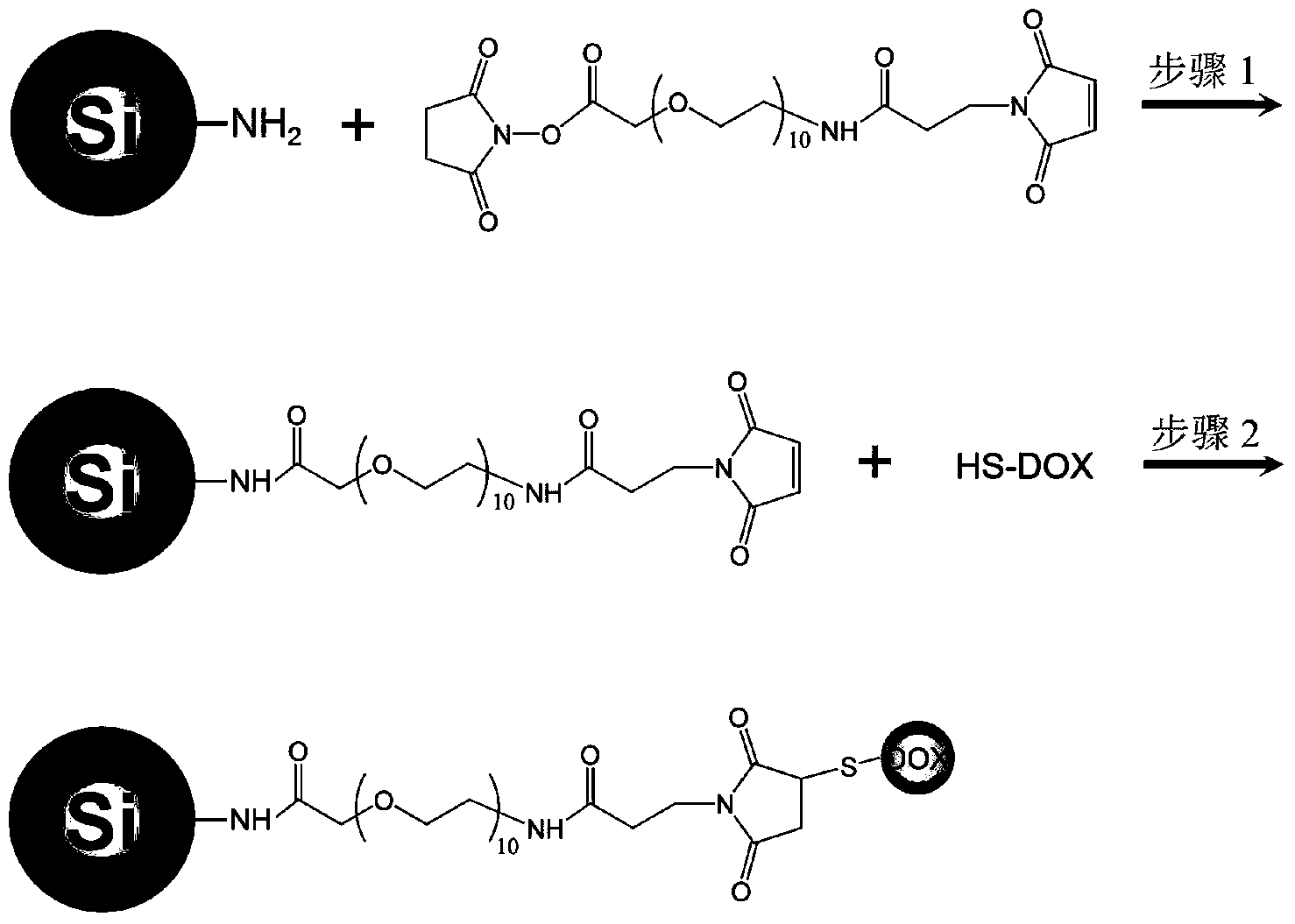

InactiveCN104306984AGood water solubilityImprove purityOrganic active ingredientsPharmaceutical non-active ingredientsSolubilityPolyethylene glycol

The invention provides application of water-soluble silicon quantum dots as drug carriers. A preparation method of a silicon quantum dot-drug molecule composition comprises the following concrete steps: preparing aminated silicon quantum dots, performing maleimide treatment on the surfaces of the aminated silicon quantum dots, and preparing the silicon quantum dot-drug molecule composition. According to the method, the silicon quantum dots are connected with drug molecules through short-chain polyethylene glycol molecules, and the prepared silicon quantum dot-drug molecule composition has the advantages of high purity, good water solubility, protein adsorption resistance, no additional fluorescent mark, capability of achieving passive targeting in the body, capability of entering urine through the blood-brain barrier and the glomerular vascular wall to be discharged from the body, a certain drug slow-release effect and the like.

Owner:SOUTHEAST UNIV

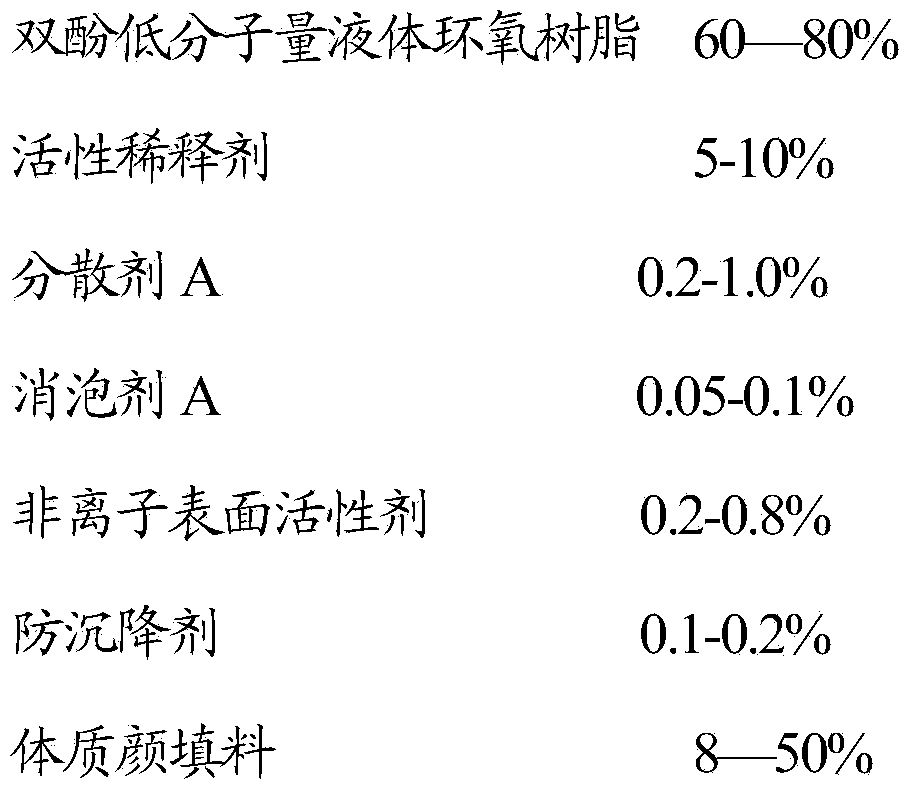

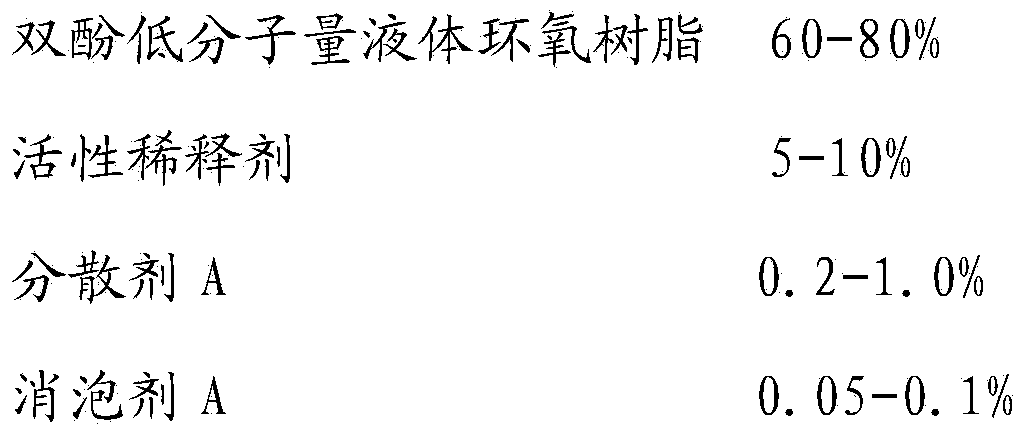

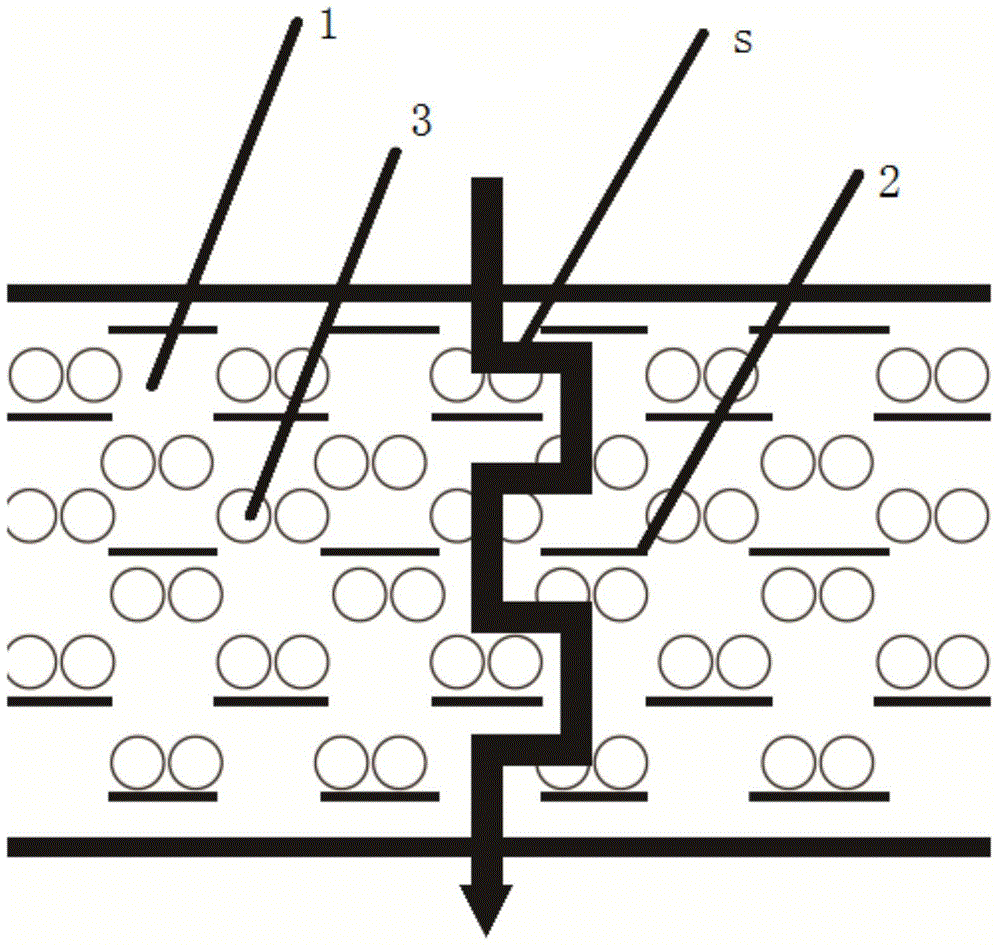

Inorganic flake water-based epoxy resin coating

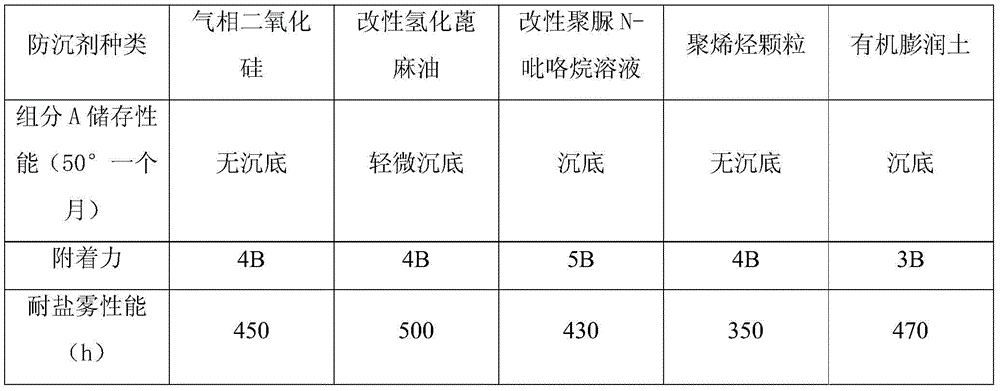

The invention discloses an inorganic flake water-based epoxy resin coating, which is composed of a component A and a component B, wherein the component A is an epoxy resin dispersion and comprises the following components by weight percent: 60-80% of bisphenol low-molecular-weight liquid epoxy resin, 5-10% of active thinner, 0.2-1.0% of dispersing agent A, 0.05-0.1% of deforming agent A, 0.2-0.8% of non-ionic surface active agent, 0.1-0.2% of anti-settling agent, 8-40% of physical filler, and 5-20% of inorganic flake material; and the component B is a hydrophilic water-based curing agent dispersion and comprises the following components by weight percent: 43-65% of modified water-based amine curing agent, 35-50% of water, 0.2-0.4% of dispersing agent B, 0.2-0.5% of deforming agent B, and 0.2-0.8% of flatting agent. The inorganic flake water-based epoxy resin coating disclosed by the invention has good water-resistance performance and is applied to buildings, therefore, the surface of a concrete or mortar substrate layer can be closed after being coated; various penetrated water vapour is thoroughly isolated; and surface decorative layers of building envelopes, such as coatings, wallpapers, wood floors and the like, are prevented from being affected with damp.

Owner:HAINAN SEQUOIA CREATION

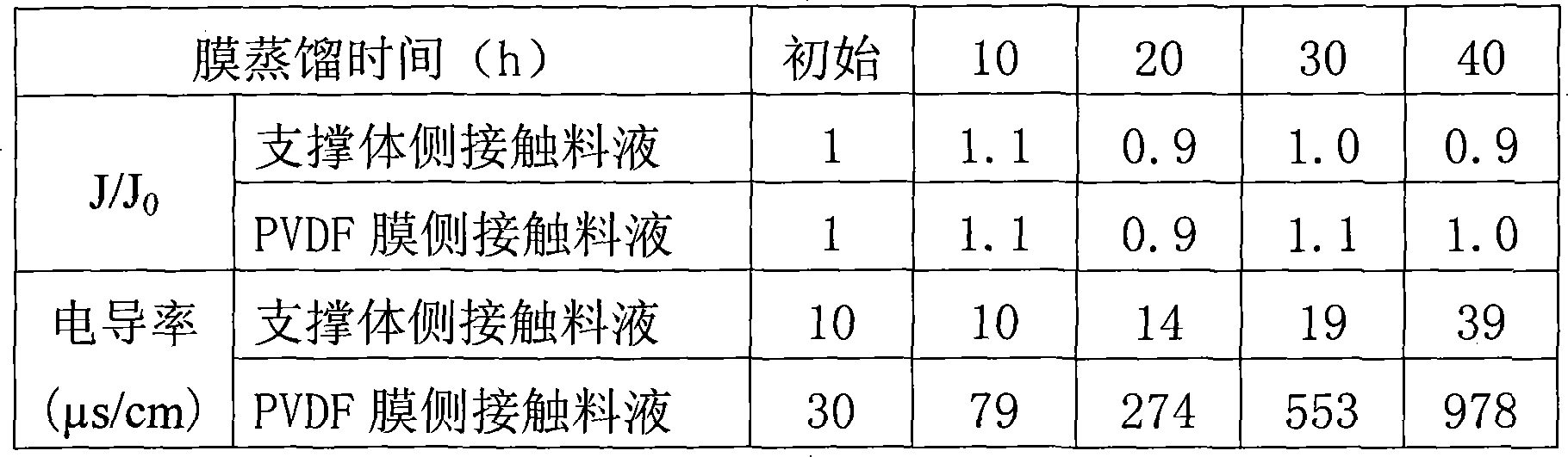

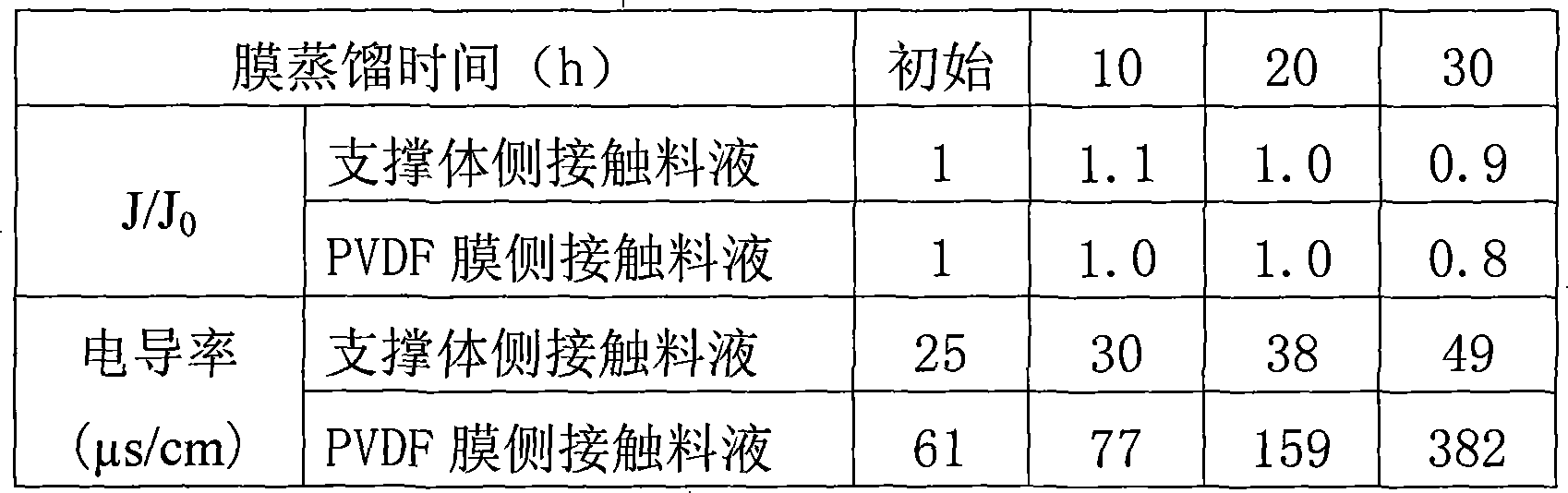

Composite distillation film and preparation method and application thereof

The invention relates to a composite distillation membrane, as well as the method and the application thereof. The composite distillation membrane is characterized in that the composite distillation membrane is a flat membrane, and is in double-layer structure; one layer is a functional finished textile support body; and the other layer is a composite hydrophobic polymer microporous film coated on the textile support body which is 5 to 100 Mu m thick; the textile support body is made of one of filament woven fabrics of fiber such as Dacron, nylon, polypropylene fiber or mucilage and so on, or non-woven fabrics with the weight ranging from 30g / m<2> to 250g / m<2>; the function finish is at least one of water repellent finish, three-proofing finish, chitosan finish, pva and citric acid finish; the fracture strength of the composite distillation membrane ranges from 400N / 5cm to 800N / 5cm; the peel strength of the composite distillation membrane ranges from 15cN / cm to 30cN / cm; and the vapour transfer rate ranges from 6kg / m<2>*24h to 9kg / m<2>*24h. During the distillation of the membrane, the textile support body of the composite distillation membrane touches feed liquid. The composite distillation membrane can resist pollution well and is applicable for various membrane distillation processes.

Owner:TIANJIN POLYTECHNIC UNIV

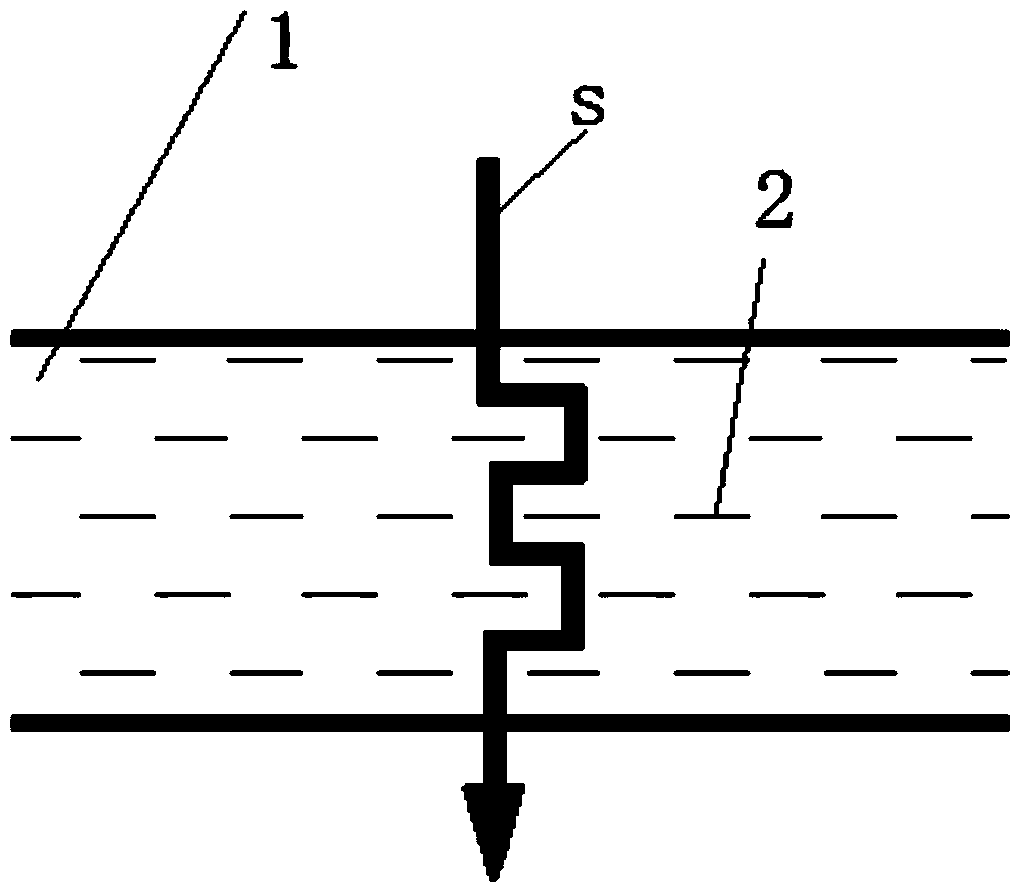

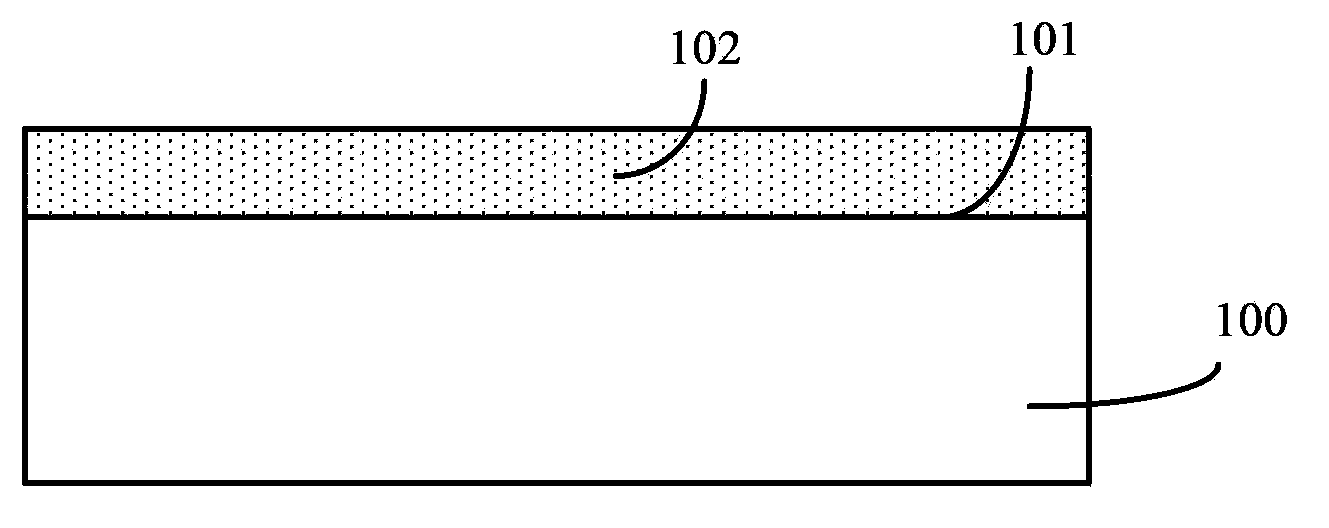

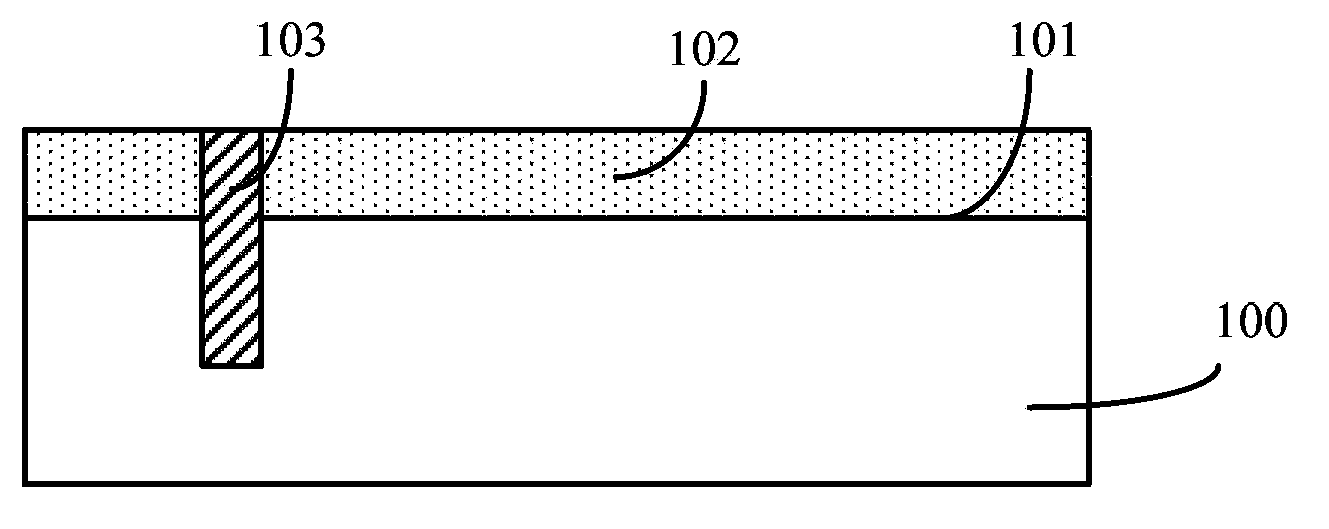

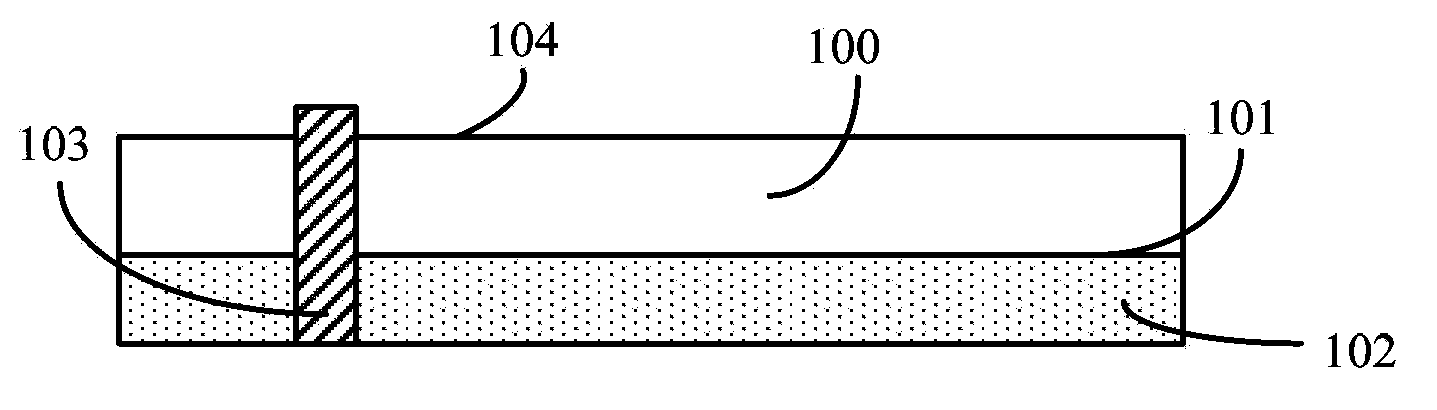

Semiconductor structure and forming method thereof

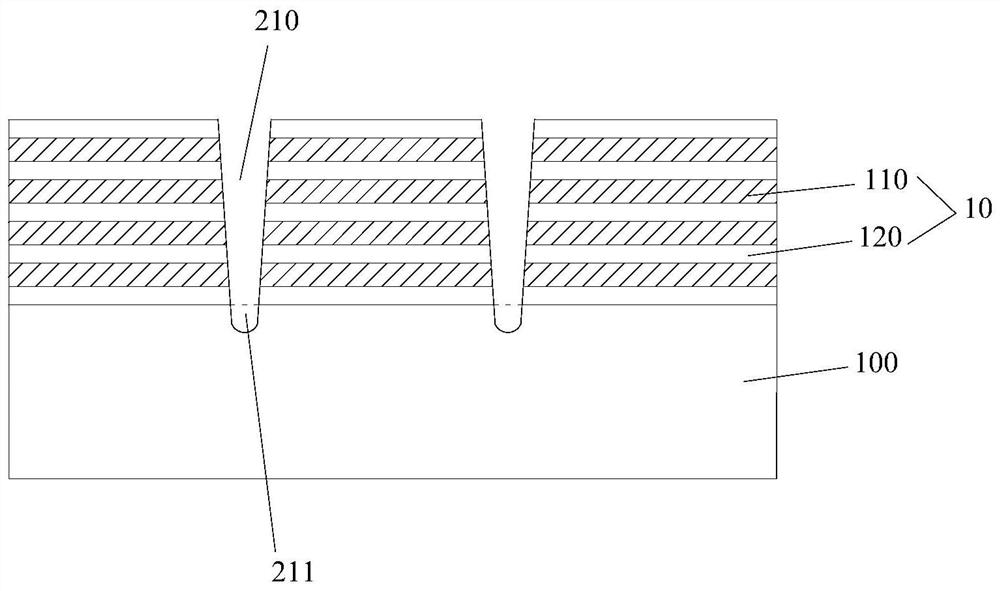

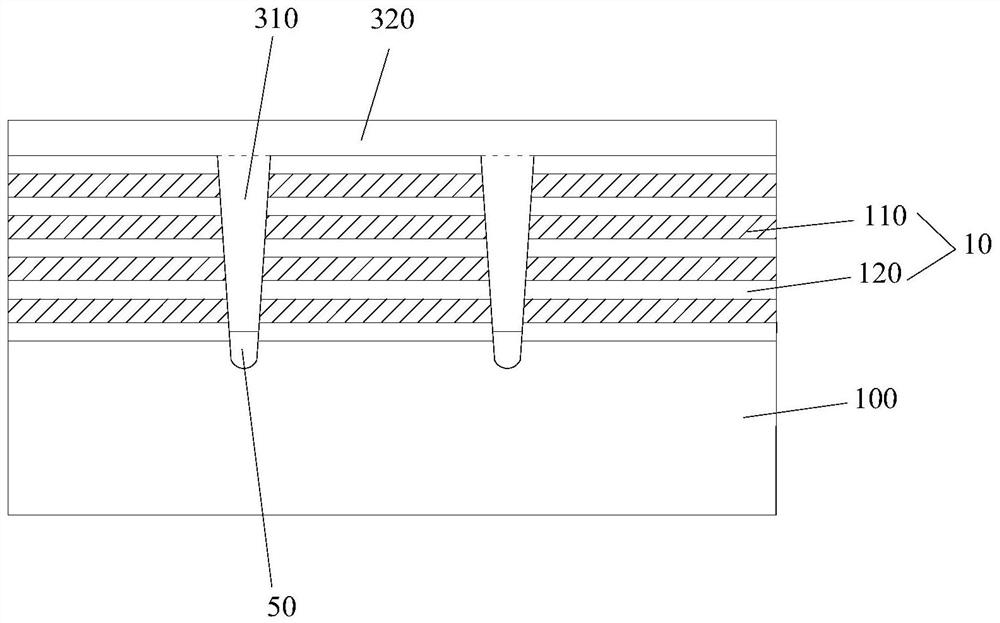

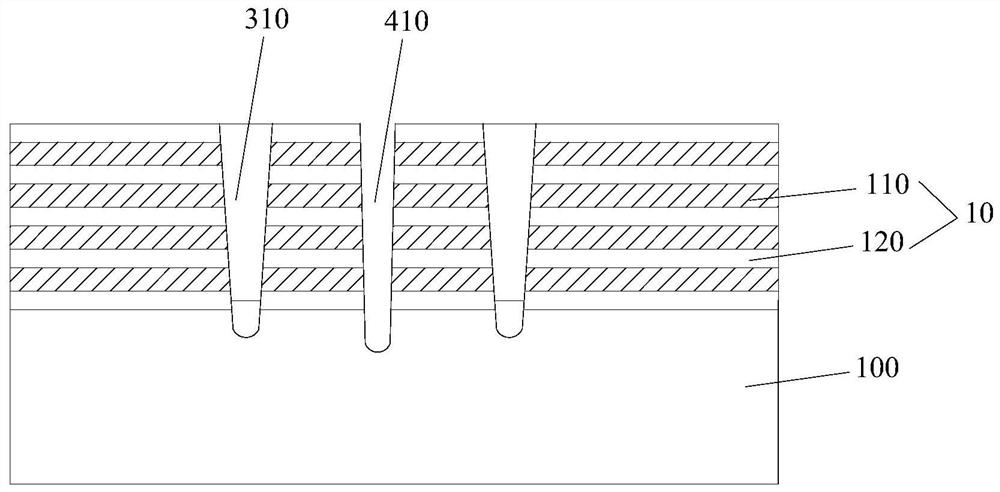

ActiveCN104253082AShape-retainingDifficult to penetrateSemiconductor/solid-state device detailsSolid-state devicesSemiconductor structureDielectric layer

The invention discloses a semiconductor structure and a forming method thereof. The forming method of the semiconductor structure comprises the steps of providing a substrate which is provided with a plugging area, forming an opening in the substrate, forming a first dielectric layer on the surface of a side wall of the opening by a conformal technology, forming a second dielectric layer at the top of the opening, and forming a conductive plug in the plugging area of the substrate, wherein the opening surrounds the plugging area of the substrate; the pattern of the surface of the first dielectric layer is identical with that of the surface of the side wall of the opening; the second dielectric layer seals the opening; a gap is formed in the opening; and the conductive plug is contacted with the first dielectric layer. The dimension of the semiconductor structure is reduced; the substrate can be prevented from breaking; and reduction of the performance of a chip or a device can be avoided.

Owner:SEMICON MFG INT (SHANGHAI) CORP

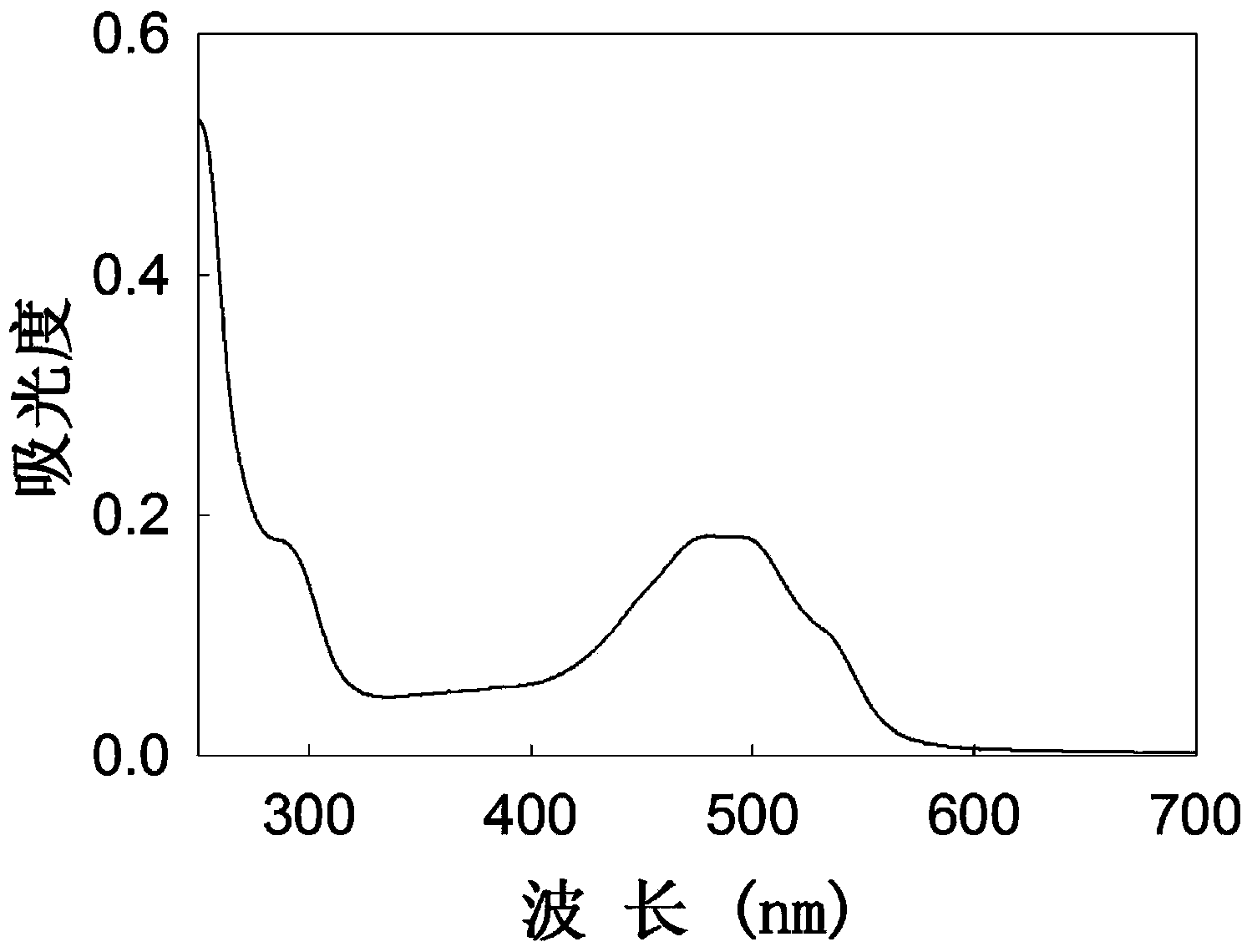

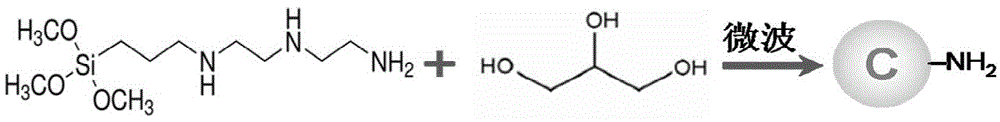

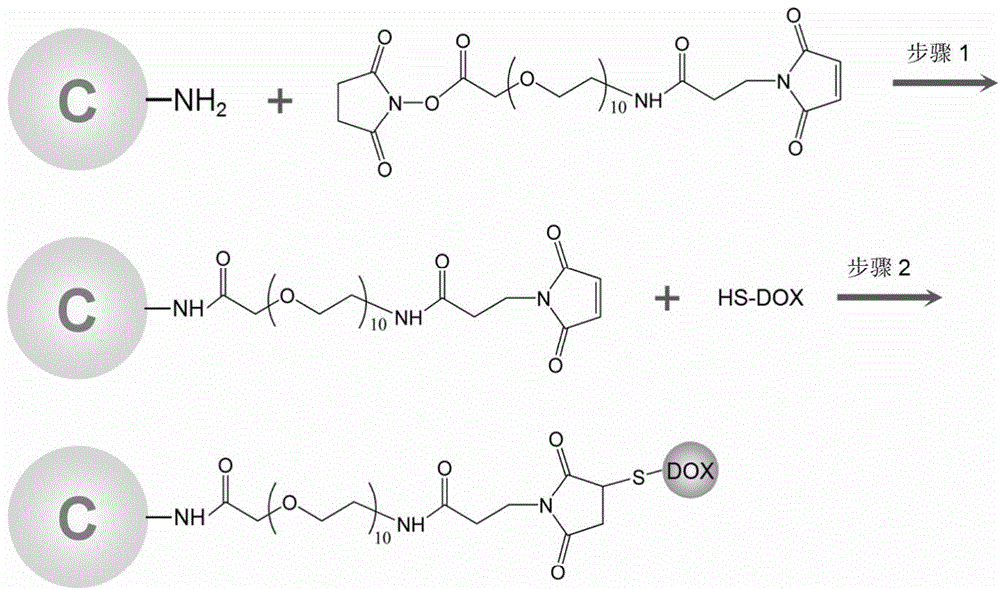

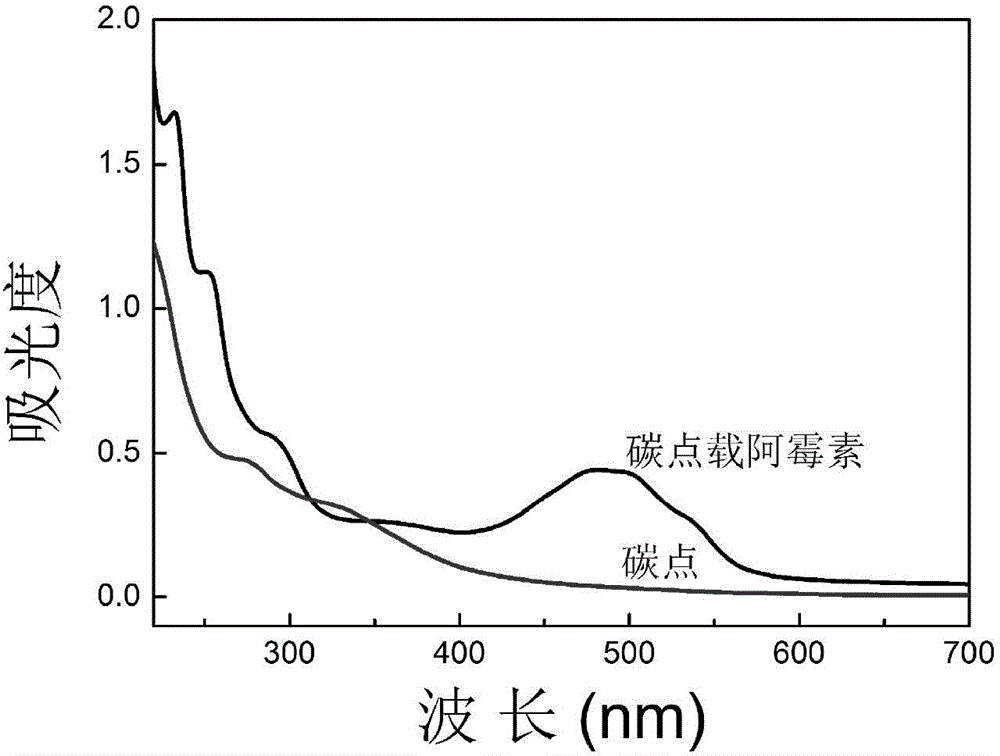

Application of carbon dot as anti-tumor medicine carrier

ActiveCN104474556AHigh yieldGood water solubilityOrganic active ingredientsPharmaceutical non-active ingredientsSolubilityQuantum yield

The invention provides an application of a carbon dot as an anti-tumor medicine carrier. The application comprises the following steps: preparing an aminated carbon dot: by taking a silane reagent containing amino groups and glycerin as raw materials, preparing the aminated carbon dot by adopting a microwave synthesis process; performing maleimide treatment on the surface of the carbon dot: reacting the aminated carbon dot with a short-chain polyethylene glycol molecule NHS-EGn-MAL of which one end has N-hydroxysuccinimide ester and the other end has maleimide to obtain the carbon dot subjected to maleimide treatment; and preparing a carbon dot-medicine molecule complex: reacting the carbon dot subjected to maleimide treatment with a medicine with sulfhydryl groups to obtain the carbon dot-medicine molecule complex. The aminated carbon dot prepared by using a method provided by the invention is high in fluorescence quantum yield, good in water solubility and low in cytotoxicity, has a great number of modifiable genes on the surface, cannot cause coagulation after modifying a short-chain polyethylene glycol chain segment, and is a very ideal medicine carrier.

Owner:SOUTHEAST UNIV

Human epidermal growth factor nanoliposome and its preparation method

InactiveCN102247300AHigh molecular weightHigh affinityCosmetic preparationsToilet preparationsCholesterolCuticle

The invention discloses a human epidermal growth factor nanoliposome, which contains liposome microcapsules and human epidermal growth factor wrapped in the liposome microcapsules, wherein the mass ratio of the human epidermal growth factor to the liposome microcapsules ranges from 1: 50 to 1: 200. The invention also discloses a method for preparing the human epidermal growth factor nanoliposome. Phosphatide and cholesterol are adopted as the main membrane materials, whose biomembrane-like structures are similar to the skin structure and have good transdermal permeability, and are easier to prepare a lipid carrier with a uniform particles size and high entrapment rate by a preparation technology. According to the invention, human epidermal growth factor (hEGF) is prepared into the nanoliposome. As a raw material, the nanoliposome supplemented by other biologically-active substances such as hyaluronic acid is prepared by a corresponding preparation technology into aqua, cream and emulsion skin care products, so as to rapidly repair damaged skin, repair and remove wrinkles, nurse after sunscreen and radiation examination, nurse sensitive skin, and remove and repair various scars.

Owner:TIANJIN TIANSHI BIOLOGICAL DEV +2

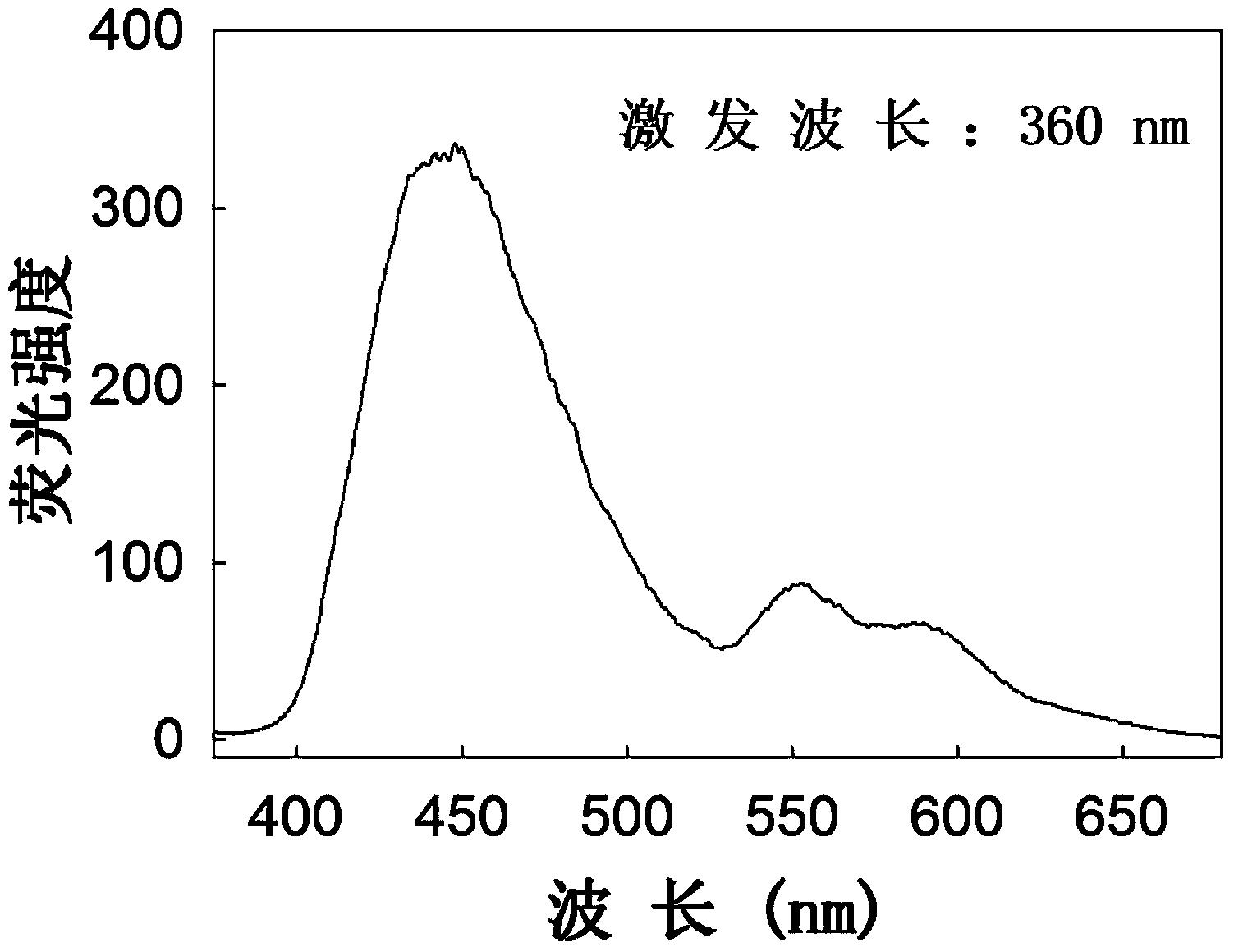

Method for observing embryo sac of paddy rice by using stone peculiar fluorescent dye, and transparent technique of whole ovary

InactiveCN1916609ADifficult to penetrateNot easy to dyePreparing sample for investigationFluorescence/phosphorescenceFluorescenceEmbryo

A method of utilizing nuclear specific fluorescent staining and ovary being made to be completely transparent technique to observe blastocyst of rice includes using certain concentration of sodium hydroxide solution to carry out softening treatment on blastocyst of rice before staining then utilizing specific combination of nucleus fluorescent staining DAPI with nucleus to observe structure of cell and nucleus in blastocyst, enabling to use laser scan confocal microscope to observe internal structure of cell clearly.

Owner:代西梅

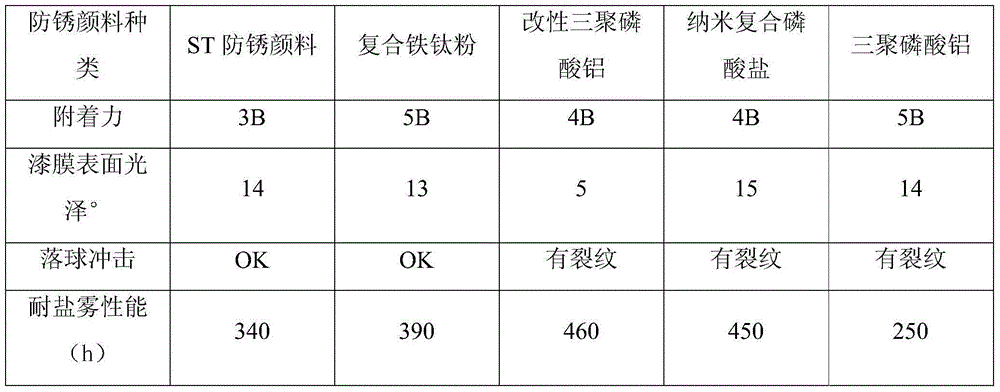

Railway transit aqueous epoxy double-component coating and preparation method thereof

ActiveCN104817929ASmall particle sizeImprove salt spray resistanceAnti-corrosive paintsEpoxy resin coatingsEpoxyZinc phosphate

The invention belongs to the field of coating preparation and especially relates to a railway transit aqueous epoxy double-component coating and a preparation method thereof. The coating includes a component A and a component B, wherein the component A comprises 3-6 parts of a coalescing agent 2,2,4-Trimethyl-1,3-pentanediol monoisobutyrate, 0.5-1 part of an aqueous epoxy dispersing agent, 0.5-1 part of a chelating-type aqueous coupling agent, 15-20 parts of iron oxide red, 15-20 parts of talcum powder, 4-6 parts of high-molecular-modified zinc phosphate, 3-4 parts of modified aluminium triphosphate, 20-25 parts of high-molecular epoxy resin, 2 parts of an emulsifier containing epoxy groups, 0.1-0.5 parts of an aqueous wetting agent, 0.1-0.5 parts of an aqueous defoaming agent, 1 part of an anti-settling agent, 1 part of an anti-flash-rust agent, 0.3 parts of an aqueous anti-sag agent and 20-30 parts of deionized water; and the component B comprises 80 parts of an aqueous polyamide epoxy curing agent and 20 parts of deionized water.

Owner:常州勤邦新材料科技有限公司

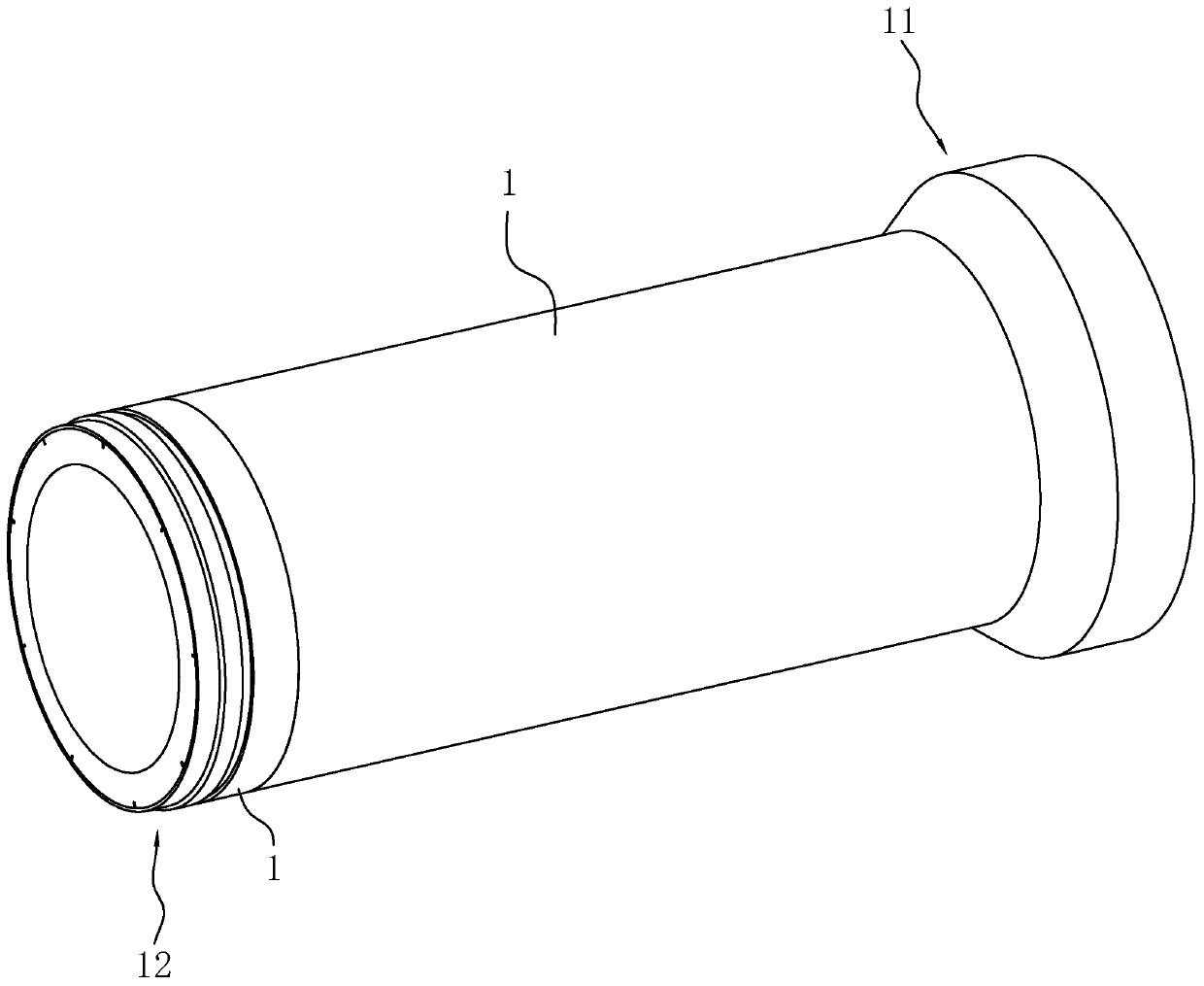

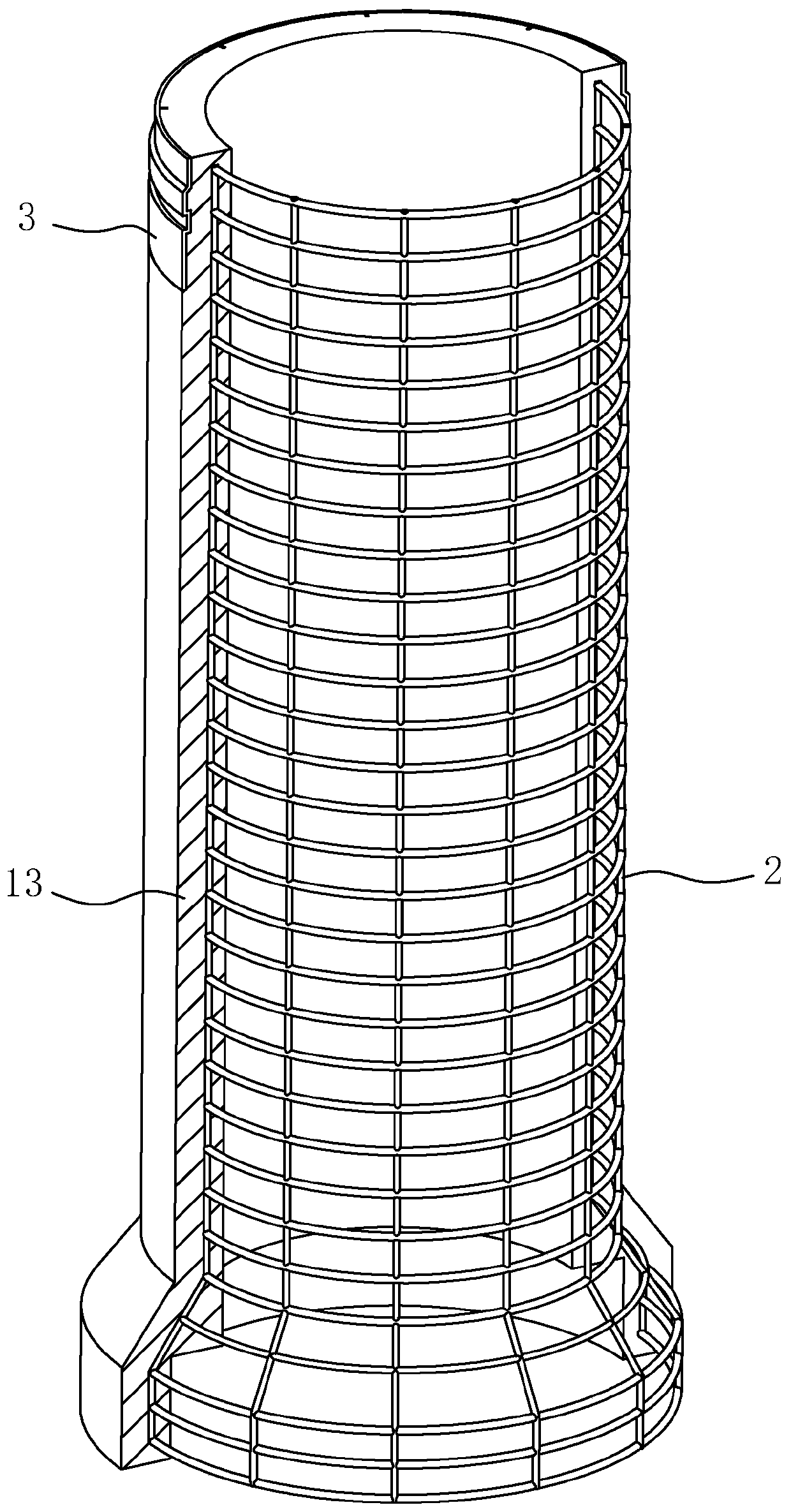

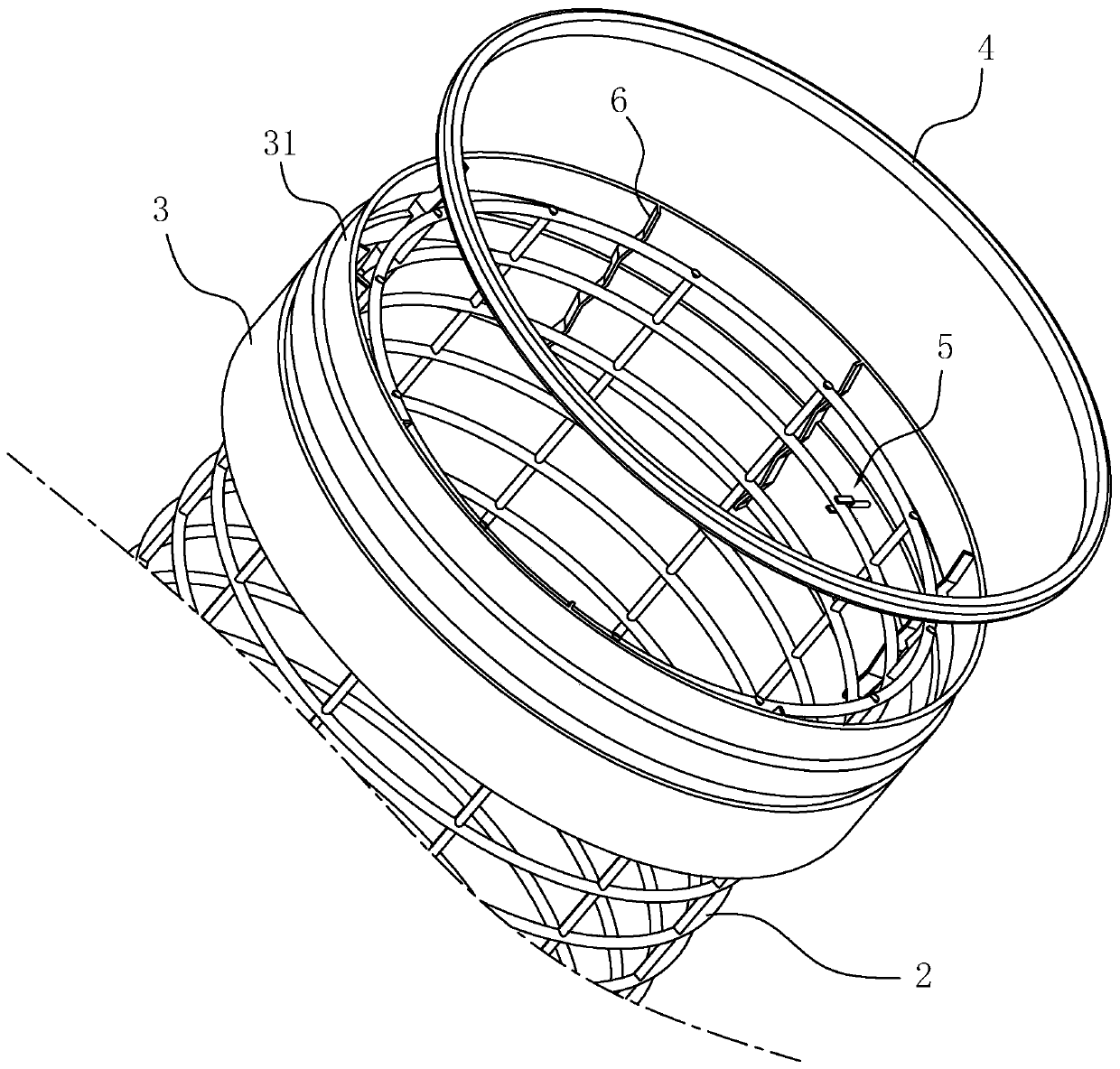

Concrete pipe and manufacturing process thereof

InactiveCN110671545AHigh success rate of preparationHigh strengthShaping reinforcementsRigid pipesManufacturing technologyConstruction engineering

The invention discloses a concrete pipe and a manufacturing process thereof. According to the technical scheme, the concrete pipe comprises a pipe body, and a socket end and a spigot end are arrangedon the pipe body. The pipe body is composed of a reinforcing steel bar keel and a concrete layer covering the reinforcing steel bar keel. The peripheral face of the spigot end of the pipe body is fixedly connected with a water stopping pipe. The concrete pipe and the manufacturing process thereof have the advantage of improving the waterproof performance of an inserting opening of the concrete pipe.

Owner:北京密云水泥制品有限责任公司

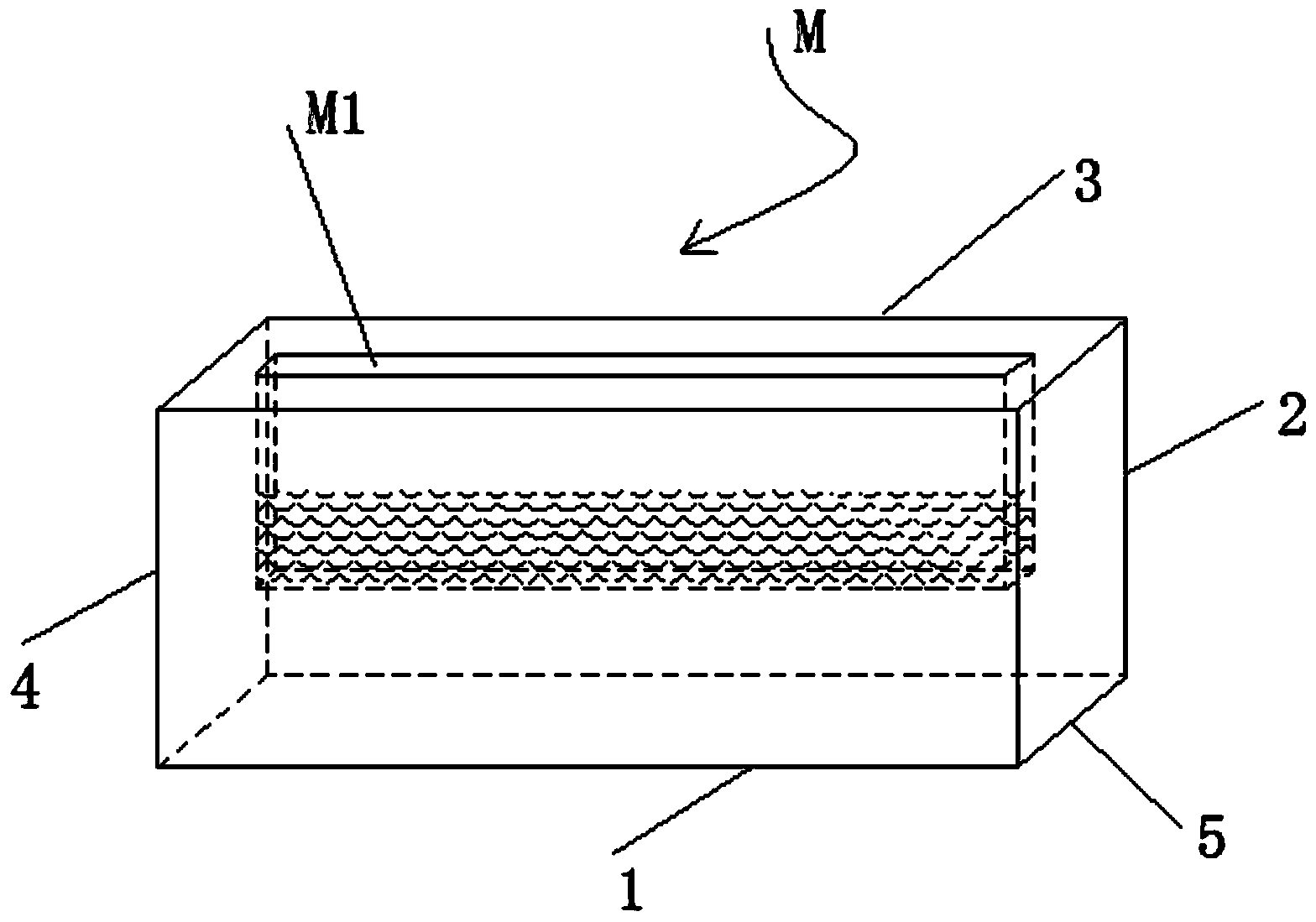

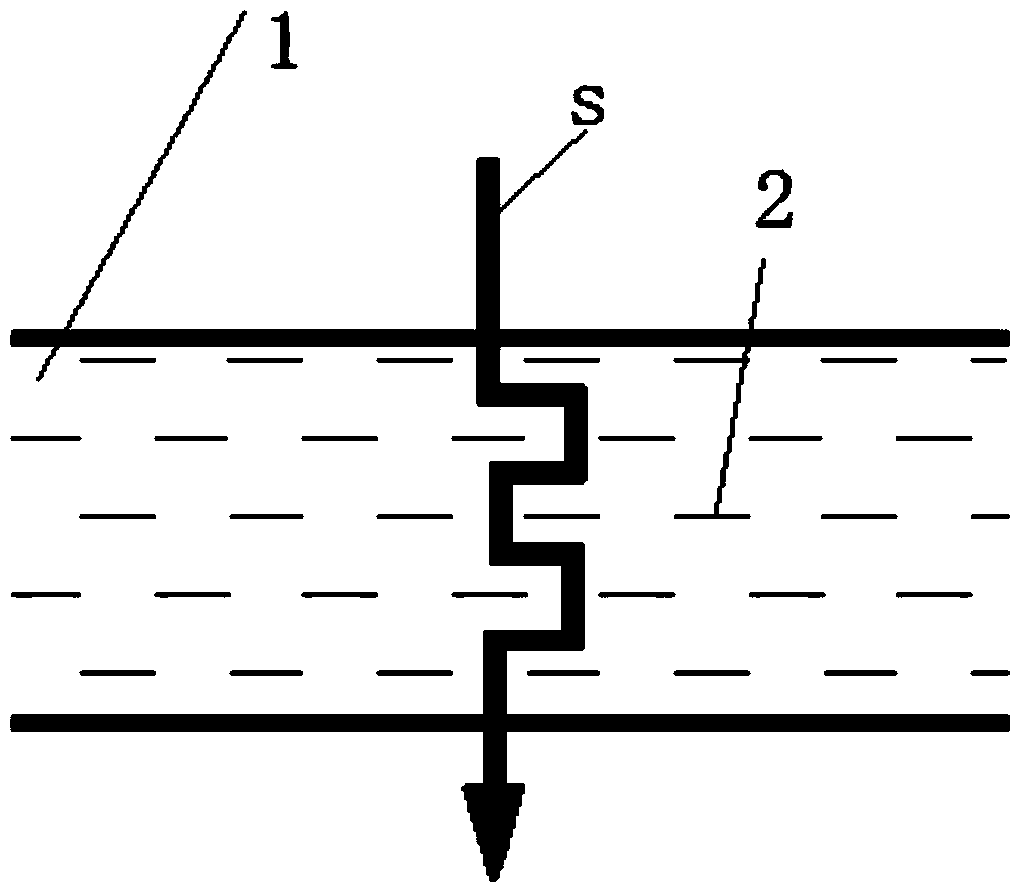

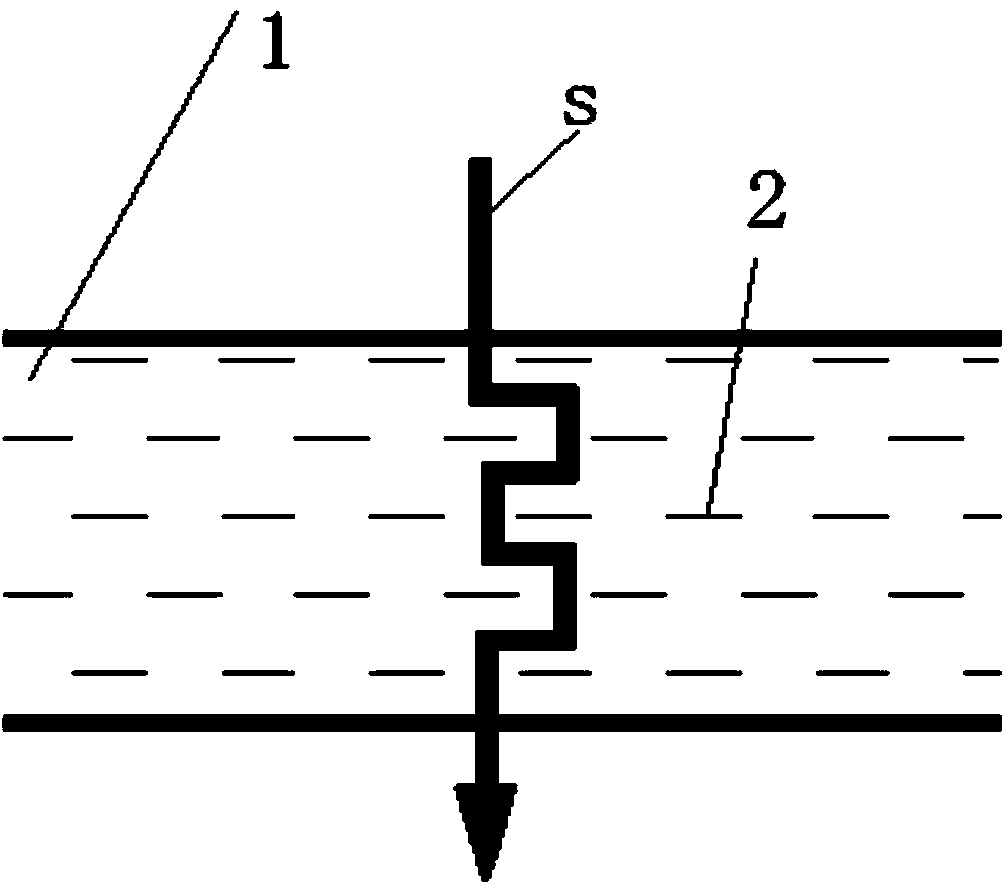

Back side dampproof and impervious structure of indoor wall of building

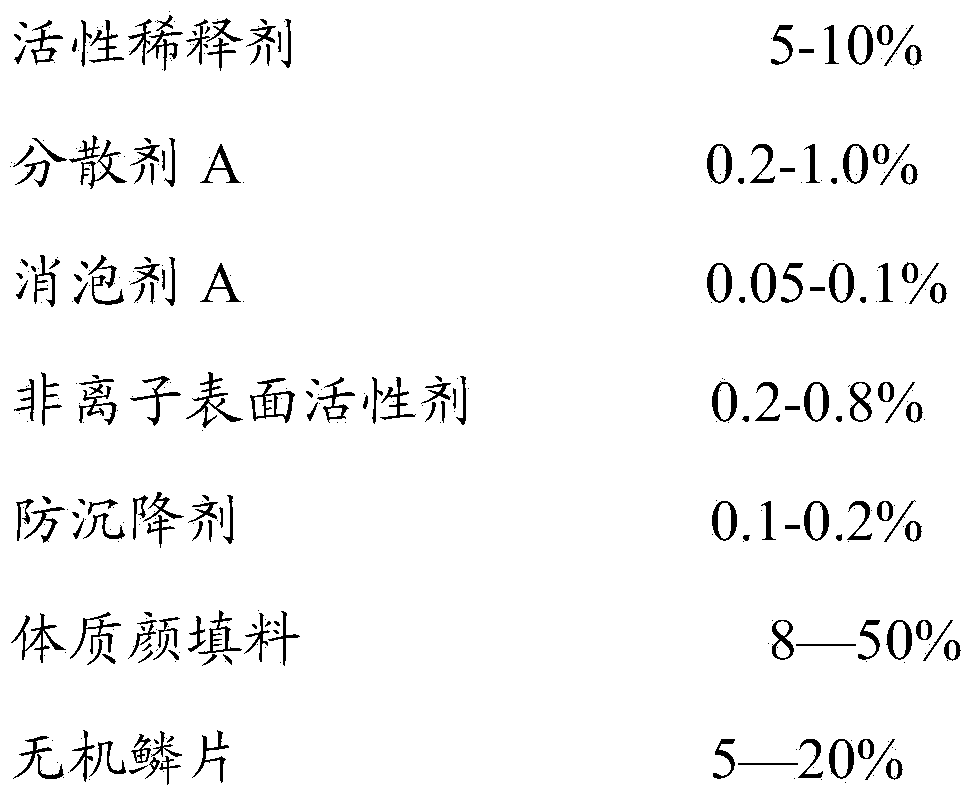

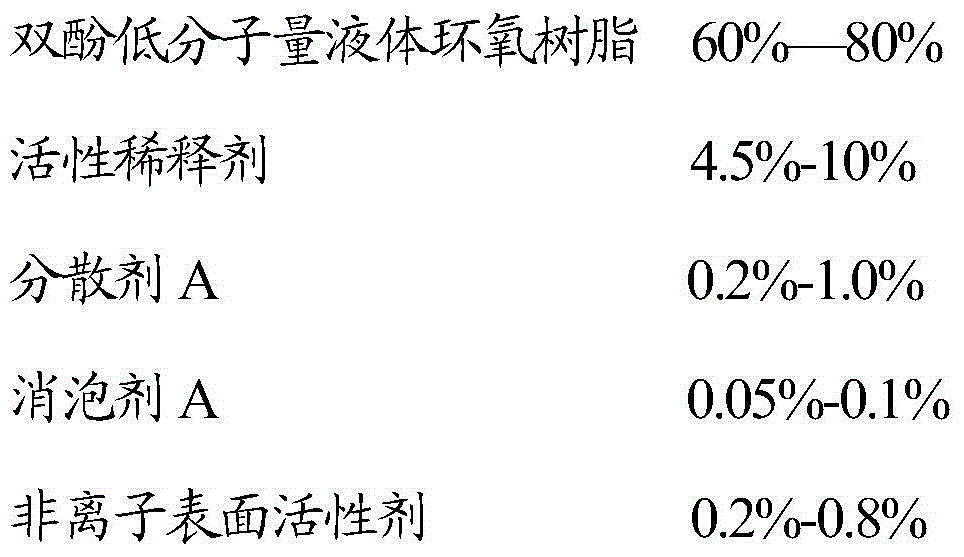

ActiveCN104005478AIncrease crosslink densityNo pollutionBuilding insulationsEpoxy resin coatingsSurface layerReactive diluent

The invention discloses a back side dampproof and impervious structure of an indoor wall of a building. The structure is composed of a base material layer, a dampproof surface layer and a decoration surface layer. The base material layer is a concrete base face or a cement mortar screeding layer. The decoration surface layer is coatings or wallpaper or wall cloth or a decoration panel or tile stone and the like. The dampproof surface layer is made of one or more layers of inorganic scale water-borne epoxy resin coatings. The inorganic scale water-borne epoxy resin coatings are composed of first components and second components, and the first components are epoxy resin dispersoid and comprise, by weight, 60 percent to 80 percent of bisphenol low molecular weight liquid epoxy resin, five percent to ten percent of reactive diluents, 0.2 percent to 1.0 percent of dispersing agents A, 0.05 percent to 0.1 percent of antifoaming agents A, 0.2 percent to 0.8 percent of non-ionic surface active agents, 0.1 percent to 0.2 percent of sinking preventing agents, eight percent to 40 percent of physical face packing and five percent to 20 percent of inorganic scale materials. The second components are hydrophilic waterborne curing agent dispersoid and comprise, by weight, 43 percent to 65 percent of modified aqueous amine curing agents, 34 percent to 60 percent of water, 0.2 percent to 0.4 percent of dispersing agents B, 0.2 percent to 0.5 percent of antifoaming agents B and 0.2 percent to 0.8 percent of flatting agents.

Owner:HAINAN SEQUOIA CREATION

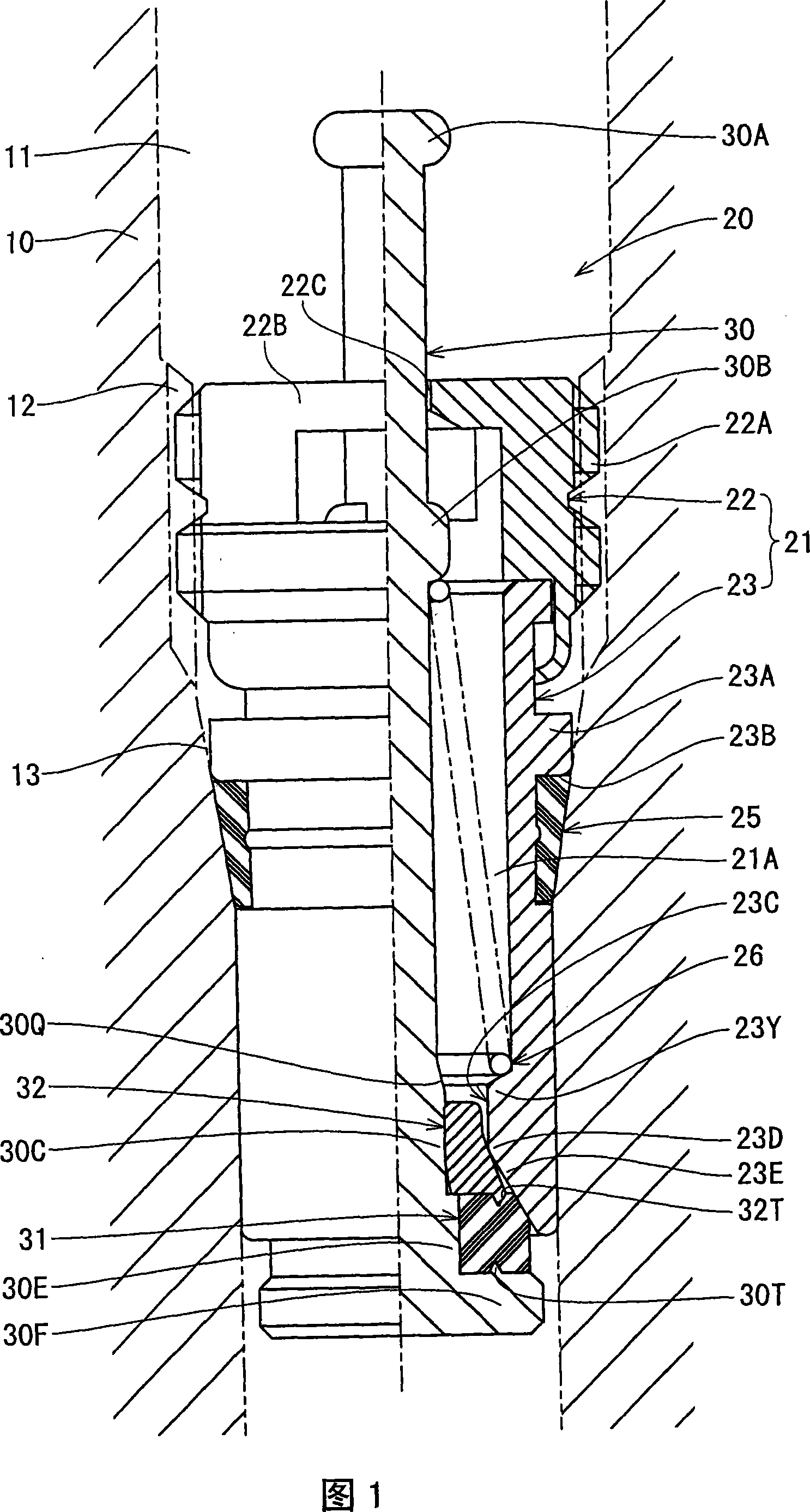

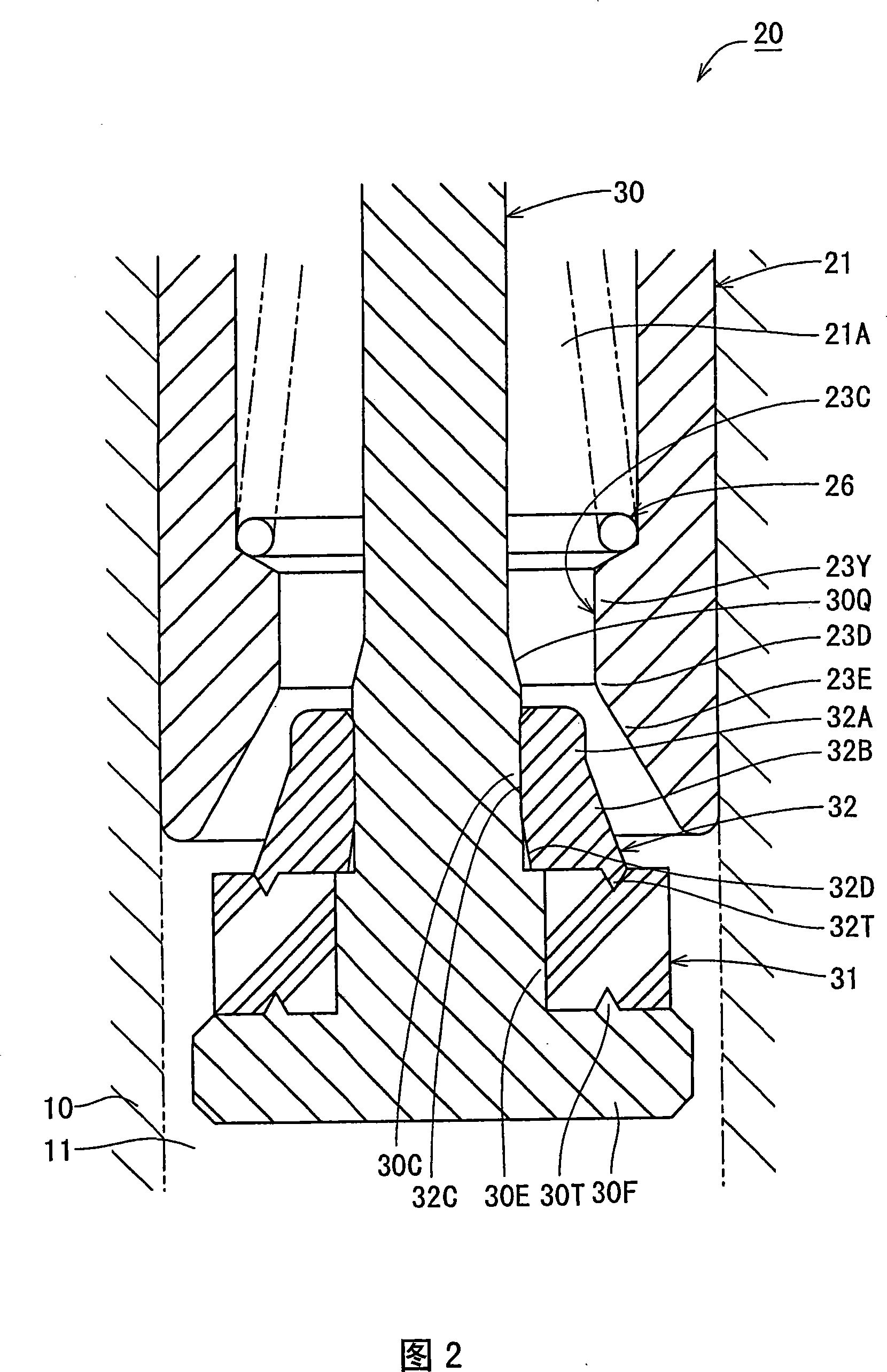

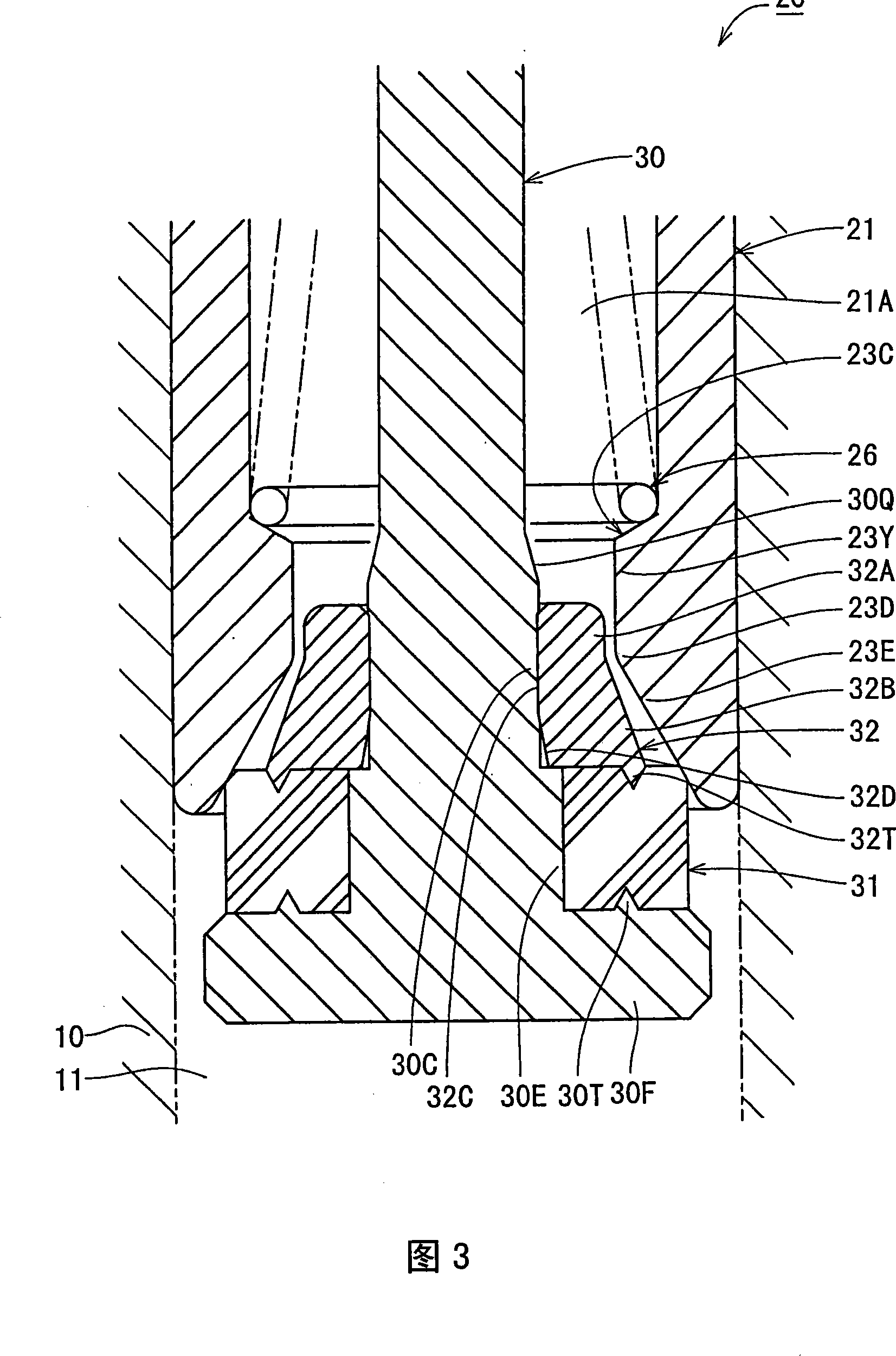

Valve core

ActiveCN101059173ADifficult to penetrateReduce leakageCheck valvesLift valveEngineeringMechanical engineering

A valve core includes a cylindrical core base fixed in a mounting hole having an inner circumferential surface, a movable shaft extending through the core base so as to be movable, the movable shaft having a distal end, a first sealing member made from rubber and located on the distal end of the movable shaft so as to adhere closely to a distal end of the core base or the inner circumferential surface of the core mounting hole, thereby closing the core mounting hole, and a second sealing member made of a metal glass and located on the distal end of either one of the movable shaft and the core base so as to adhere to the distal end of the other, thereby closing the core mounting hole.

Owner:PACIFIC INDUSTRIAL CO LTD

Method carrying out water resistance and seepage resistance maintenance on wall from architectural interior

ActiveCN104018690ANo pollutionDifficult to penetrateBuilding repairsEpoxy resin coatingsResin coatingReactive diluent

The invention discloses a method carrying out water resistance and seepage resistance maintenance on a wall from the architectural interior. The method comprises the steps that a damp-proof surface course is arranged after the portion, with seepage, of the wall is cleaned and reinforced, and then an ornament layer on the surface of the wall is recovered. The damp-proof surface course is made of one or more layers of inorganic flake water-borne epoxy resin coatings composed of first components and second components. The first components are epoxy resin dispersoid comprising, by weight, 60-80% of bisphenol low molecular weight liquid epoxy resin, 5-10% of reactive diluents, 0.2-1.0% of dispersing agents A, 0.05-0.1% of defoaming agents A, 0.2-0.8% of non-ionic surface active agents, 0.1-0.2% of anti-settling agents, 8-40% of extender pigment filler and 5-20% of inorganic flake materials. The second components are hydrophilic aqueous curing agent dispersoid comprising, by weight, 43-65% of modified aqueous amine curing agents, 35-50% of water, 0.2-0.4% of dispersing agents B, 0.2-0.5% of defoaming agents B and 0.2-0.8% of flatting agents.

Owner:HAINAN SEQUOIA CREATION

Wall surface wooden furniture moisture-resistant and termite-resistant structure

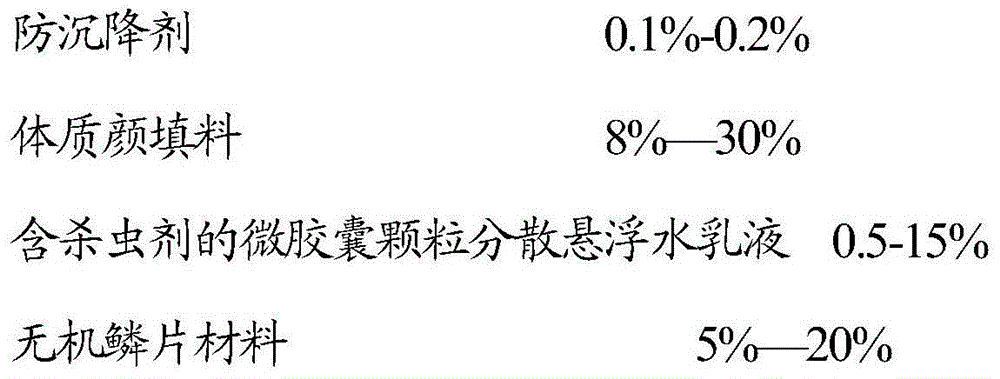

ActiveCN104151994APrevent decayAvoid destructionAntifouling/underwater paintsPaints with biocidesEmulsionResin coating

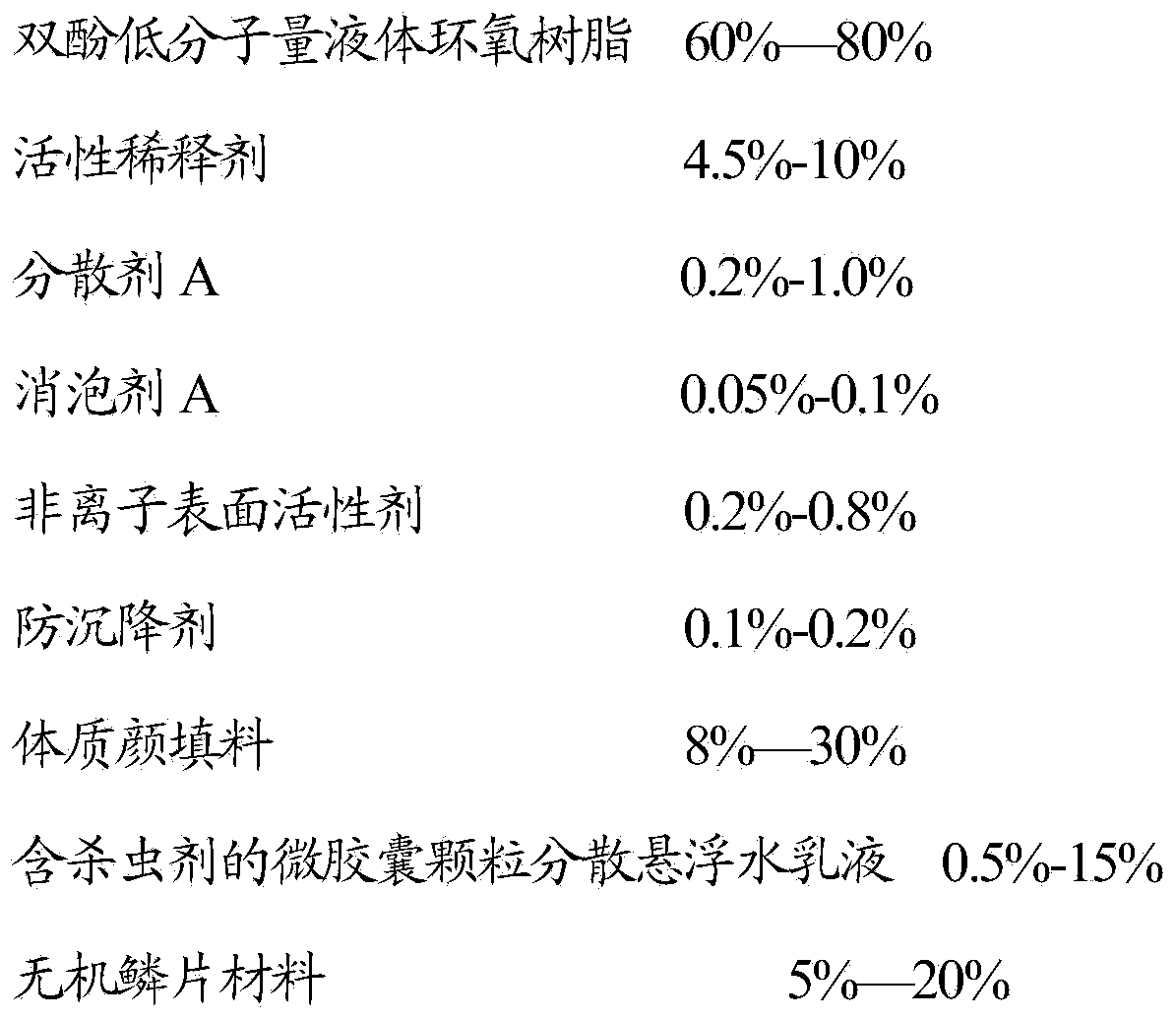

The present invention discloses a wall surface wooden furniture moisture-resistant and termite-resistant structure, which comprises a substrate layer, a wooden furniture attachment wall surface, and a moisture-resistant and termite-resistant coating positioned between the substrate layer and the wooden furniture attachment wall surface, wherein the substrate layer is a concrete or cement mortar floor, and the moisture-resistant and termite-resistant coating is prepared by adopting one or plural layers of termite-resistant inorganic flake aqueous epoxy resin coating materials, wherein the termite-resistant inorganic flake aqueous epoxy resin coating material comprises a component A and a component B, wherein the component A comprises, by weight, 60-80% of a bisphenol low molecular weight liquid epoxy resin, 4.5-10% of an active diluent, 0.2-1.0% of a dispersant, 0.05-0.1% of an antifoaming agent, 0.2-0.8% of a non-ionic surfactant, 0.1-0.2% of an anti-settling agent, 8-30% of an extender pigment filler, 0.5-15% of an insecticide-containing microcapsule particle dispersing suspension aqueous emulsion, and 5-20% of an inorganic flake material, and the component B comprises, by weight, 39-65% of a modified aqueous amine curing agent, 34-60% of water, 0.2-0.4% of a dispersing agent, 0.2-0.5% of an antifoaming agent, and 0.2-0.8% of a leveling agent.

Owner:HAINAN SEQUOIA CREATION

Diethylenetriamine derivatives, and preparation method and application thereof

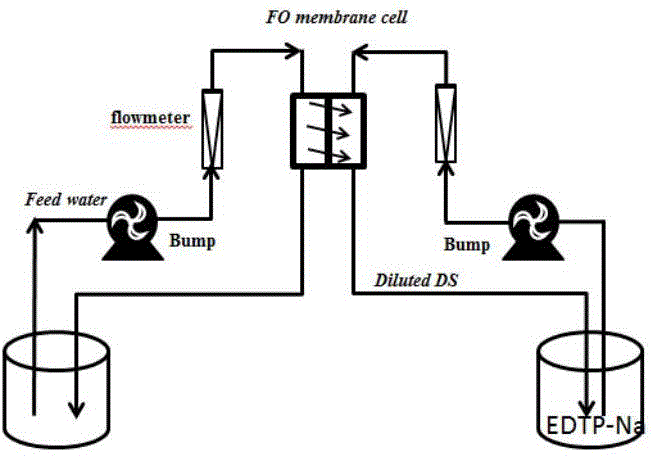

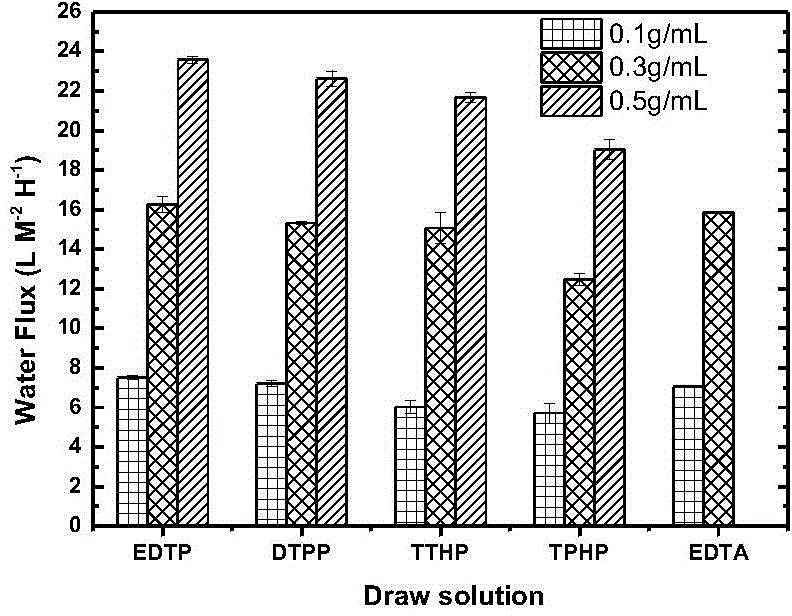

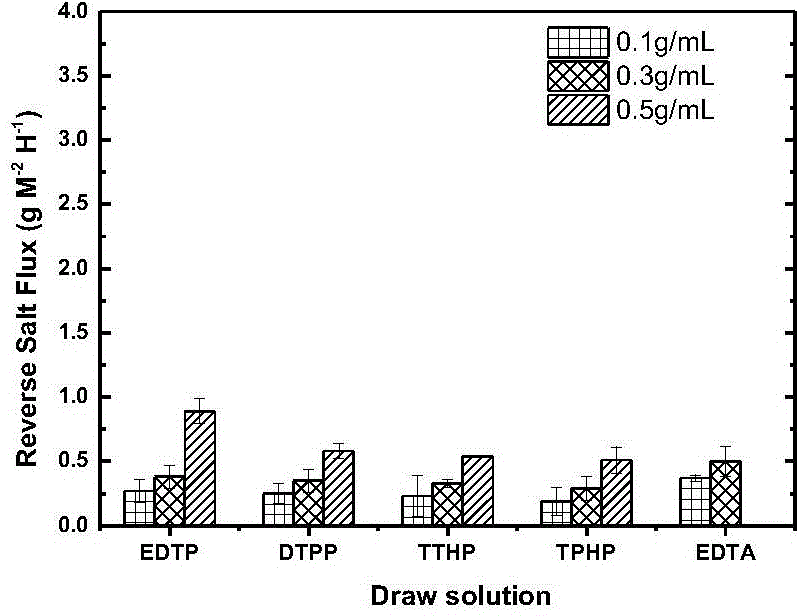

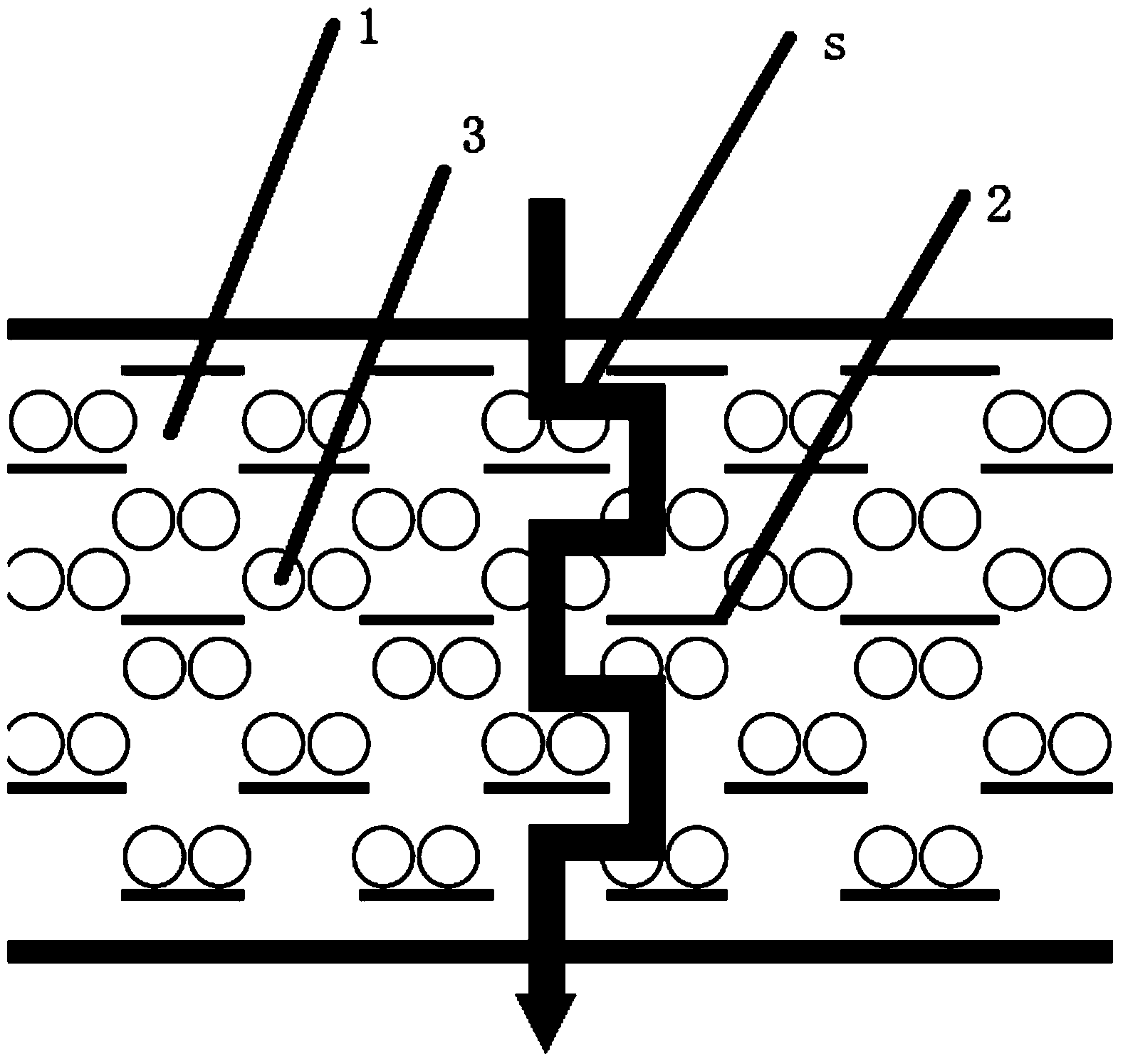

InactiveCN104370764ADifficult to penetrateIncrease water fluxOrganic compound preparationWater/sewage treatment bu osmosis/dialysisDiethylenetriamineMethyl acrylate

The invention discloses diethylenetriamine derivatives, and a preparation method and application thereof. The diethylenetriamine derivatives are acids or soluble salts disclosed as chemical formula (I), wherein n is 0, 1, 2 or 3. The preparation method is implemented by carrying out Michael addition reaction on framework molecule and methyl acrylate. The diethylenetriamine derivatives disclosed by the invention are used for preparing a forward osmosis drawing solution, have the advantages of high safety, no toxicity, high water flux and low salt flowage, and greatly lower the energy consumption cost.

Owner:HUAZHONG UNIV OF SCI & TECH

Anti-termite inorganic flake waterborne epoxy resin coating

ActiveCN104231867AHighly corrosiveInsulationAntifouling/underwater paintsPaints with biocidesEmulsionResin coating

The invention discloses an anti-termite inorganic flake waterborne epoxy resin coating. The waterborne epoxy resin coating comprises a component A and a component B, wherein the component A comprises the following components in percentage by weight: 60%-80% of bisphenol low-molecular-weight liquid epoxy resin, 4.5%-10% of active diluent, 0.2%-1.0% of dispersing agent, 0.05%-0.1% of defoaming agent, 0.2%-0.8% of non-ionic surfactant, 0.1%-0.2% of anti-settling agent, 8%-30% of extender pigment / filler, 0.5-15% of microcapsule particle dispersion suspension aqueous emulsion containing an insecticide and 5%-20% of inorganic flake material; and the component B comprises the following components in percentage by weight: 39%-65% of modified waterborne amine curing agent, 34%-60% of water, 0.2%-0.4% of dispersing agent, 0.2%-0.5% of defoaming agent and 0.2%-0.8% of flatting agent. The waterborne epoxy resin coating disclosed by the invention has the advantages of very good waterproof and moisture-proof property and anti-termite property.

Owner:HAINAN SEQUOIA CREATION

Process for manufacturing waterproof, flame-retardant and breathable fabric

InactiveCN105483905ARaise the gradeQuality improvementSolvent-treatmentWoven fabricsYarnPolymer science

The invention discloses a process for manufacturing a waterproof, flame-retardant and breathable fabric. The process comprises the processes of fiber preparation, spinning and weaving. According to fiber preparation, natural plant materials are prepared into natural plant fibers, then flame-retardant treatment is carried out, and flame-retardant fibers are obtained. According to spinning, the flame-retardant fibers and composite fibers are blended and prepared into yarn, and the fineness of the yarn is 400 dtex. According to weaving, the blended yarn is spun, and the fabric with the warp density being 200 pieces / 10 cm and the weft density being 250 pieces / 10 cm is obtained. According to the process, the natural plant fibers are subjected to flame-retardant treatment, and compounded with fibers with flame-retardant performance and fibers with waterproofness performance, so that the fibers achieve flame-retardant performance, and meanwhile the manufactured fibers are smoother, elastic, good in breathability and convenient to manufacture.

Owner:HUIAN HUACHEN TRADE CO LTD

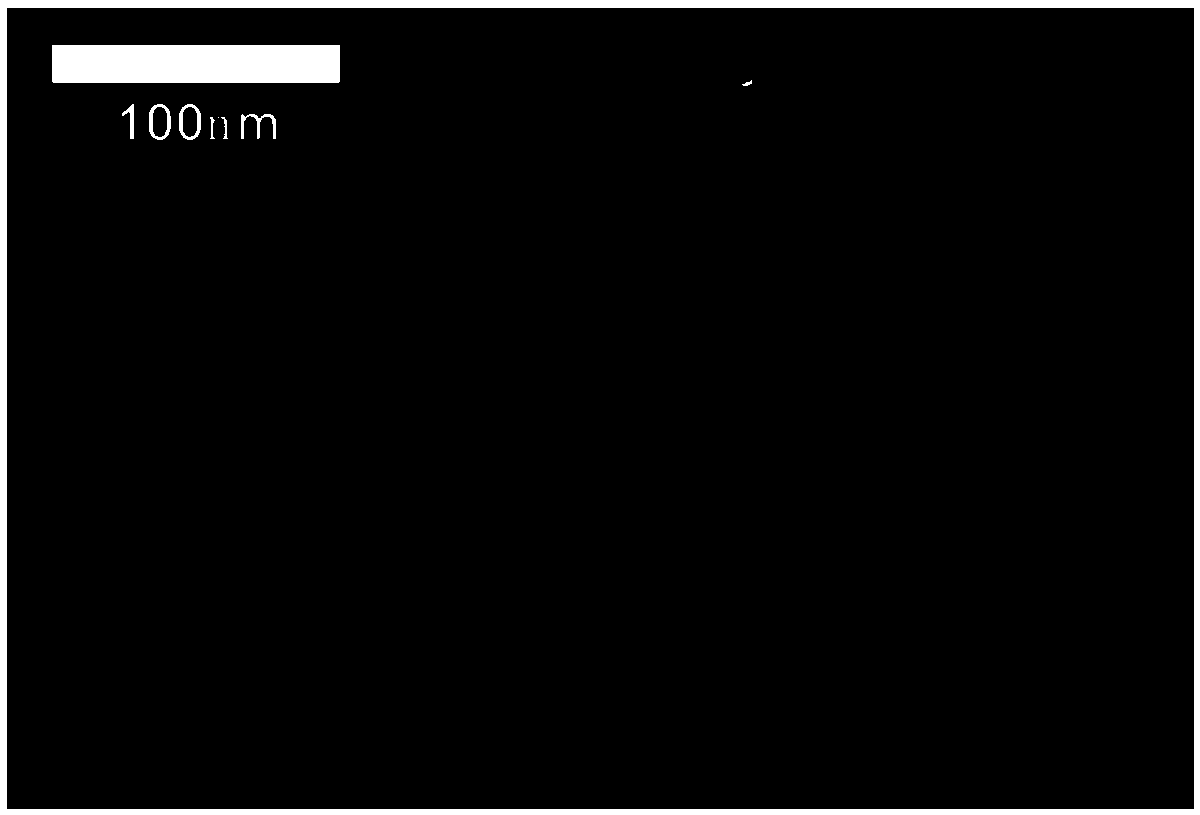

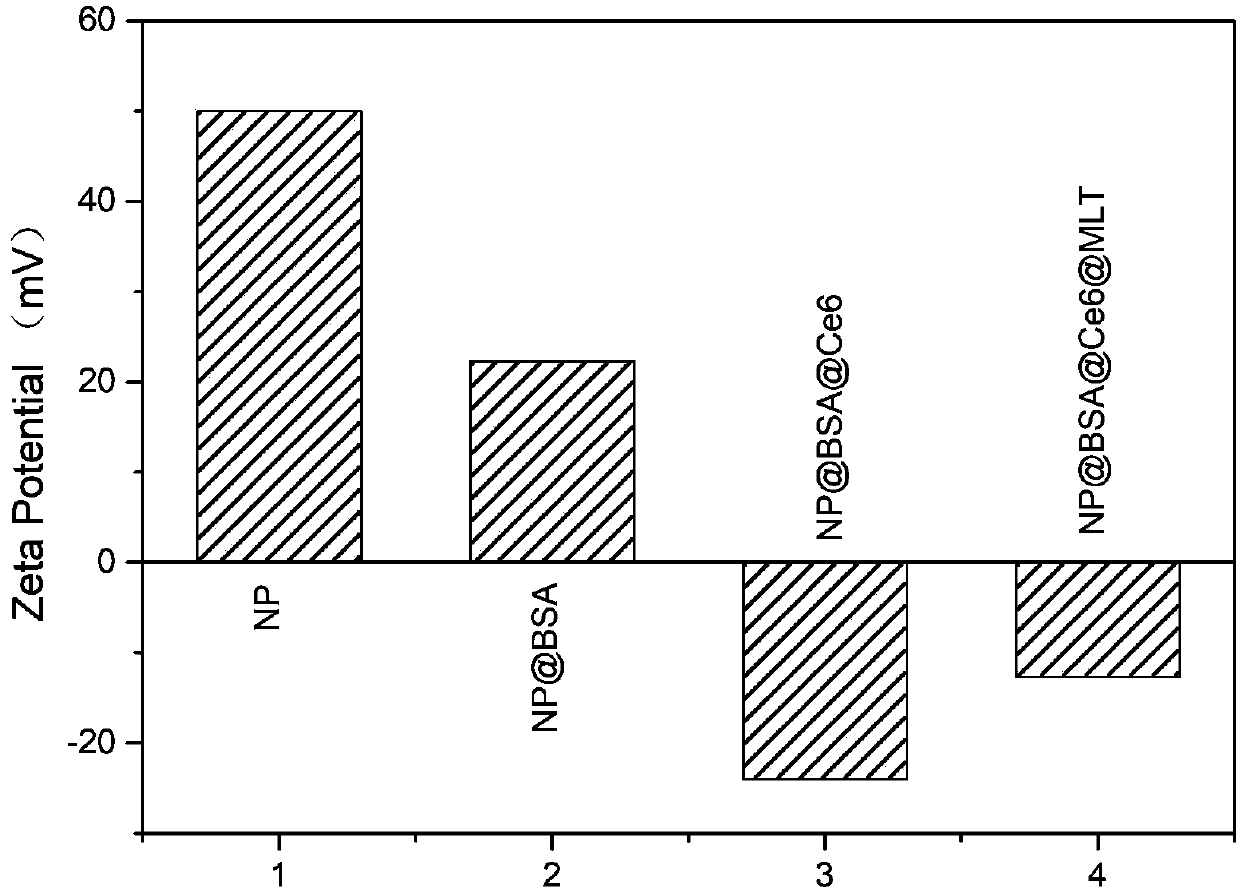

Preparation method and application of photosensitive nanocarrier for carrying melittin

InactiveCN109513000AGood biocompatibilityHigh encapsulation efficiencyPowder deliveryPeptide/protein ingredientsNanocarriersPhotosensitizer

The invention provides a preparation method of a photosensitive nanocarrier for carrying melittin. The preparation method comprises the following steps that (1) nano-alumina particles are prepared; (2) biocompatible nano-metal particles are prepared; (3) the nanocarrier for carrying the melittin is prepared; and (4) a photosensitizer is added to obtain photosensitive nanoparticles, namely Al2O3@BSA@Melittin@Ce6, for carrying the melittin. The photosensitive nanocarrier, namely Al2O3@BSA@Melittin@Ce6, for carrying the melittin is applied to preparation of anticancer drugs. According to the preparation method of the photosensitive nanocarrier for carrying the melittin, the preparation problem of the photosensitive nanocarriers for carrying the melittin can be solved, and meanwhile, the technical problem that normal cells take in nanoparticles insufficiently is solved.

Owner:XIEHE HOSPITAL ATTACHED TO TONGJI MEDICAL COLLEGE HUAZHONG SCI & TECH UNIV

Method for preparing distillation film with support body

The invention provides a method for preparing a distillation film with a support body. The method comprises the following steps: conducting vacuum drying on PVDF powder; mixing the dried PVDF powder with an additive; stirring for dissolving, so as obtain a transparent uniform casting solution; allowing the casting solution to stand still or putting the casting solution in a vacuum drying box for bubble removing; pouring the non-bubble casting solution on a clean glass plate attached with a polyester screen mesh; fast distributing the non-bubble casting solution to be uniform with a scraper; allowing a nascent film to stand still in the air; immersing the nascent film together with the glass plate into deionized water of which the temperature is constant for 10 min; removing the glass plate; putting the immersed film into a great amount of deionized water; replacing the deionized water frequently; carrying out preservation for at least 3 days. The film prepared according to the method is high in mechanical strength, flux and interception rate, and low in cost.

Owner:HARBIN ENG UNIV

Formula and production process of epoxy resin adhesive as well as application of epoxy resin adhesive in copper-clad plate for light-emitting diode (LED)

InactiveCN107815280AImprove insulation performanceNot easy to damageNon-macromolecular adhesive additivesLaminationEpoxyCopper

The invention discloses a formula and a production process of epoxy resin adhesive as well as application of the epoxy resin adhesive in a copper-clad plate for a light-emitting diode (LED), aiming atsolving the problems that the insulation performance of the copper-clad plate affects the quality of an LED screen, so thatand the LED screen is easily damaged if the insulation performance of the copper-clad plate is poor. The epoxy resin adhesive is characterized by being prepared from the following materials in parts by weight: 260-275 parts of epoxy resin, 2-3 parts of a curing agent, 25-35 parts of a solvent, 45-55 parts of magnesium hydroxide, 100-115 parts of silica powder, 0.1-1.5 parts of a coupling agent and 0.05-0.20 part of a curing agent accelerator, wherein the coupling agent isprepared from a silane coupling agent,sothat and;after the epoxy resin adhesive is used, the aim of enabling the insulation performance of the copper-clad plate to be better is achieved.

Owner:浙江元集新材料有限公司

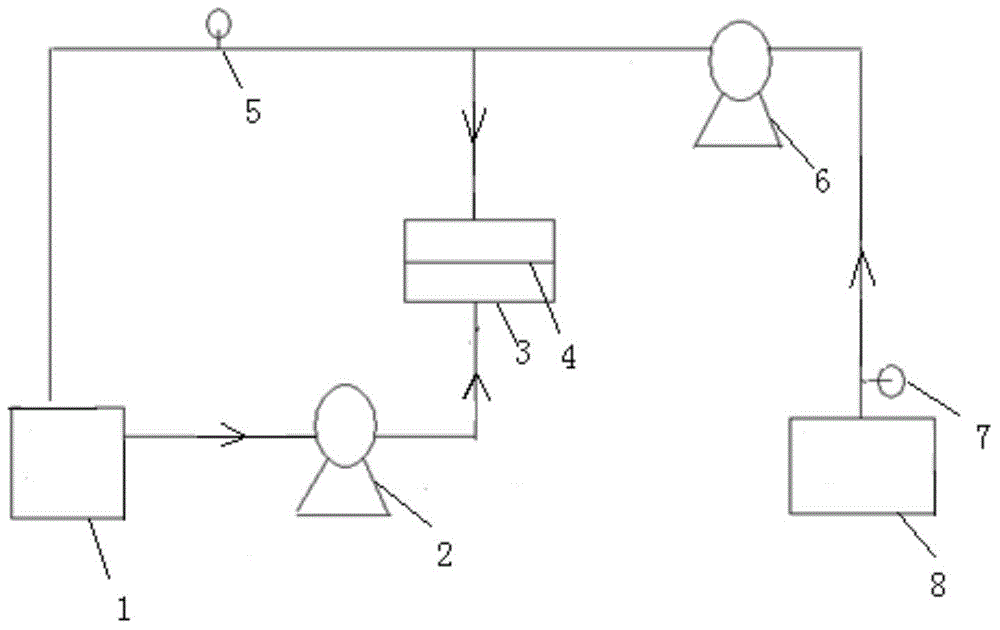

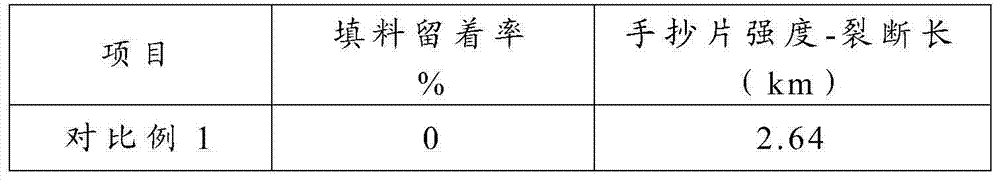

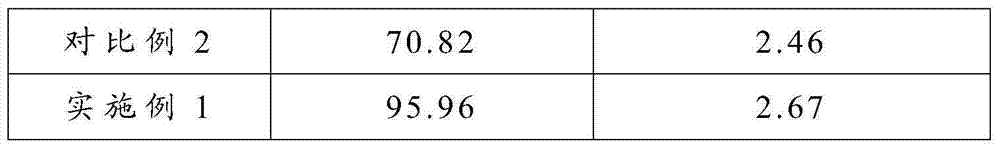

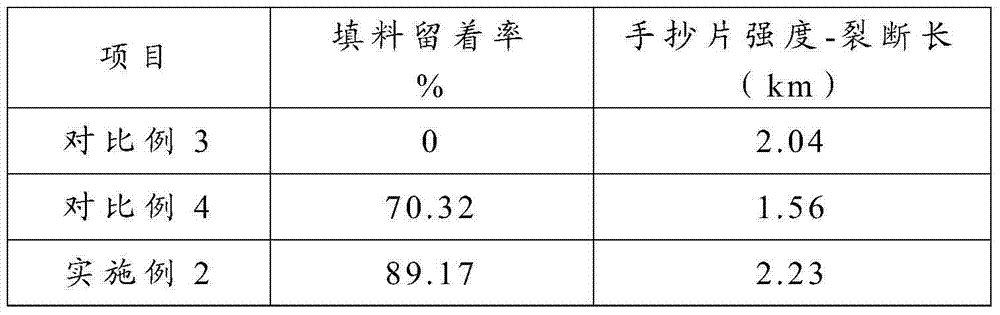

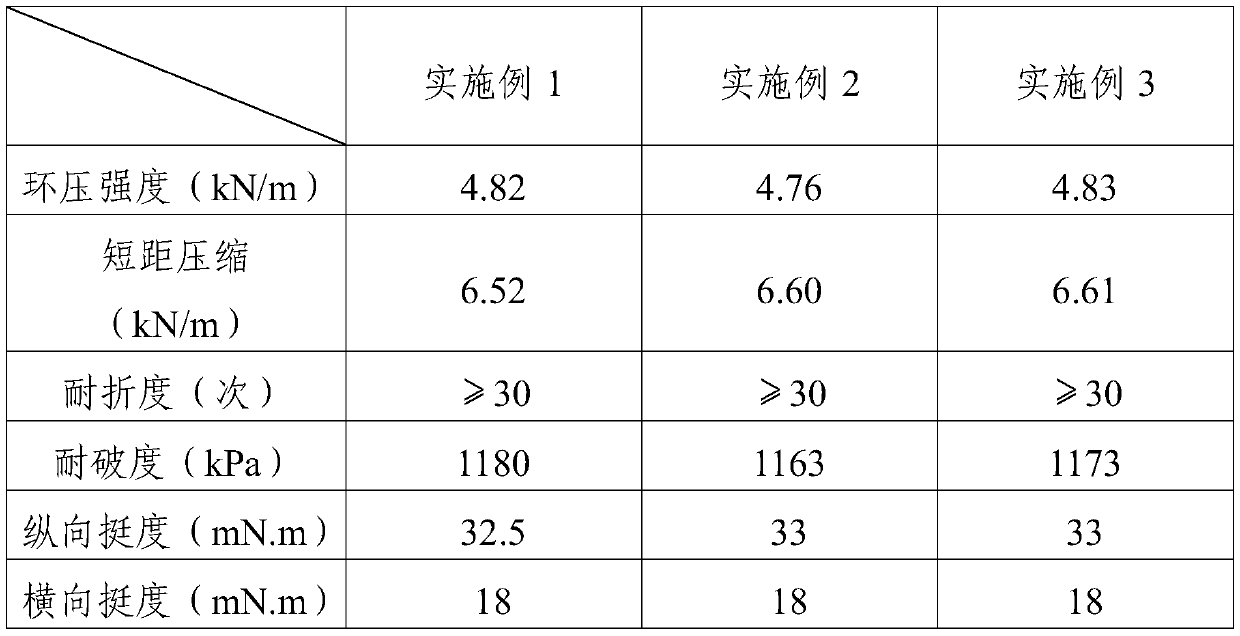

Papermaking technology and paper

InactiveCN103590278AImprove retentionLarge particle sizeNon-fibrous pulp additionPaper/cardboardFiberHydrogen

The invention discloses a papermaking technology which comprises the following steps: preparing a starch-filler composite system: respectively preparing starch water suspension and papermaking filler water suspension, mixing the starch water suspension, the papermaking filler water suspension and a crosslinking agent to obtain a mixture system, wherein the absolute ratio of starch to filler is (1: 210)-(1: 1,000); gelatinizing and crosslnking the starch in the mixture system to form the starch-filler composite system; supplying paper pulp, mixing the starch-filler composite system and the paper pulp, and making paper through the paper pulp. The invention also provides paper manufactured by the technology. Compared with the starch-filler composite system with non-modified filler, the starch-filler composite system with the modified filler has a large particle size, the filler particles have low probability of penetrating a forming net and can be retained; furthermore, the crosslinked starch of the composite system can generate hydrogen bonding reaction with pulp fibers to enable the filler to be stuck to the fibers, so that the retention rate of the filler on the paper can be greatly improved.

Owner:GOLD HONG YE PAPER

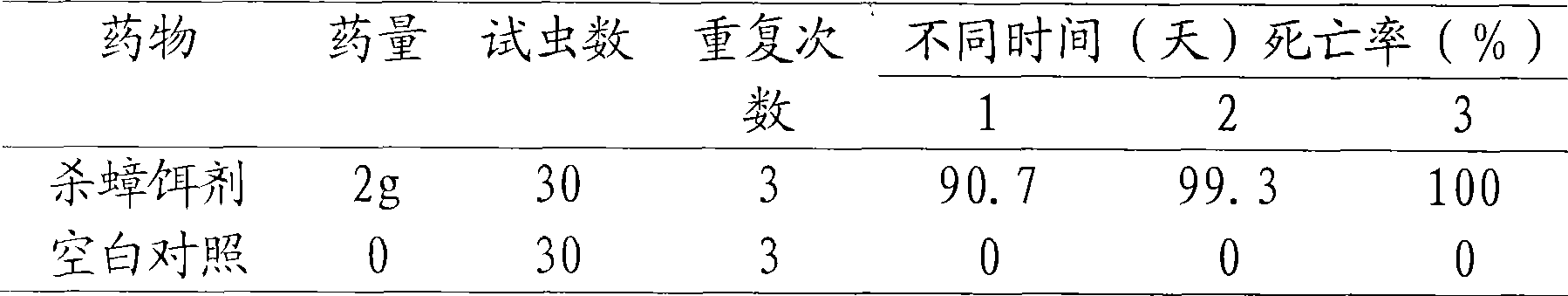

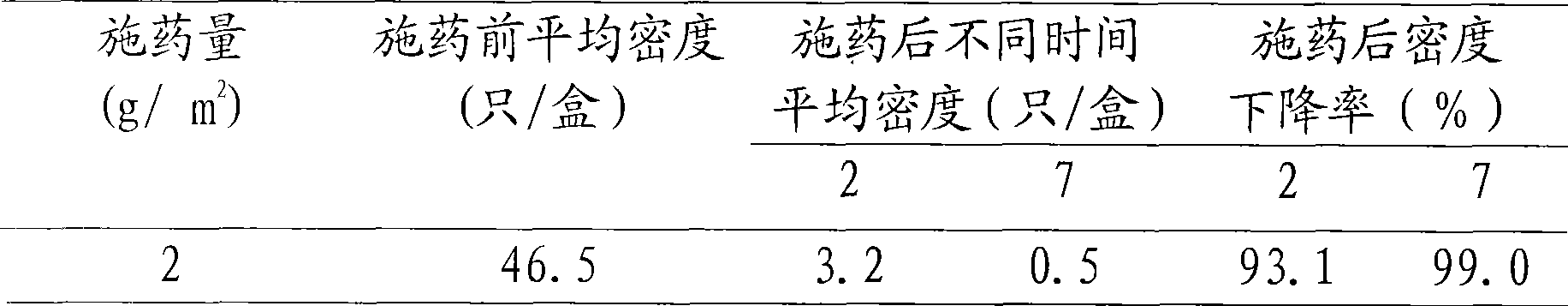

Cockroach killing bait

The invention relates to a roach bait, and belongs to the technical field of pesticides. The roach bait consists of the following raw materials in percentage by weight: 0.2 to 0.6 percent of ivermectin, 79 to 85 percent of gelatinized flour, 14 to 20 percent of sugar, 0.2 to 0.5 percent of gelatinized sesame powder, 0.2 to 0.5 percent of milk powder and 0.02 to 0.2 percent of fumaric acid. The ivermectin in the roach bait is taken as an effective pesticidal composition, and mainly has the function of increasing the release of inhibitory neurotransmitter gamma aminobutyric acid (GABA) of polypide so as to prevent the transmission of neural signals, make muscle cells lose contractility and make the polypide dead. However, the peripheral neurotransmitter of mammals is acetylcholine and cannot be influenced by the ivermectin, and the ivermectin is difficult to permeate through hemato encephalic barrier, so that the ivermectin has high safety coefficient. The gelatinized four, the sugar, the gelatinized sesame powder and the milk powder form a phagostimulant; and the fumaric acid is taken as an antiseptic so as to improve the effective period of products. The roach bait has the advantages of good palatability, strong attractive effect, high efficiency and low toxicity, convenient application, low dosage, environmental protection, and the like.

Owner:林燕如

Anti-ferroelectric-paraelectric material coupled capacitor dielectric and preparation method therefor

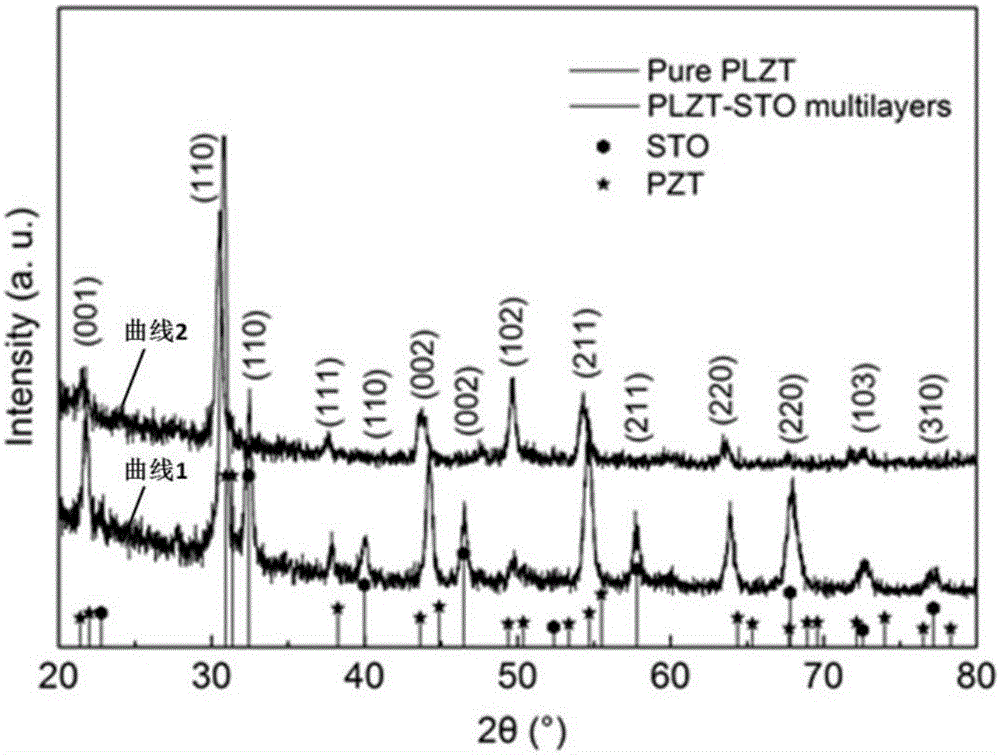

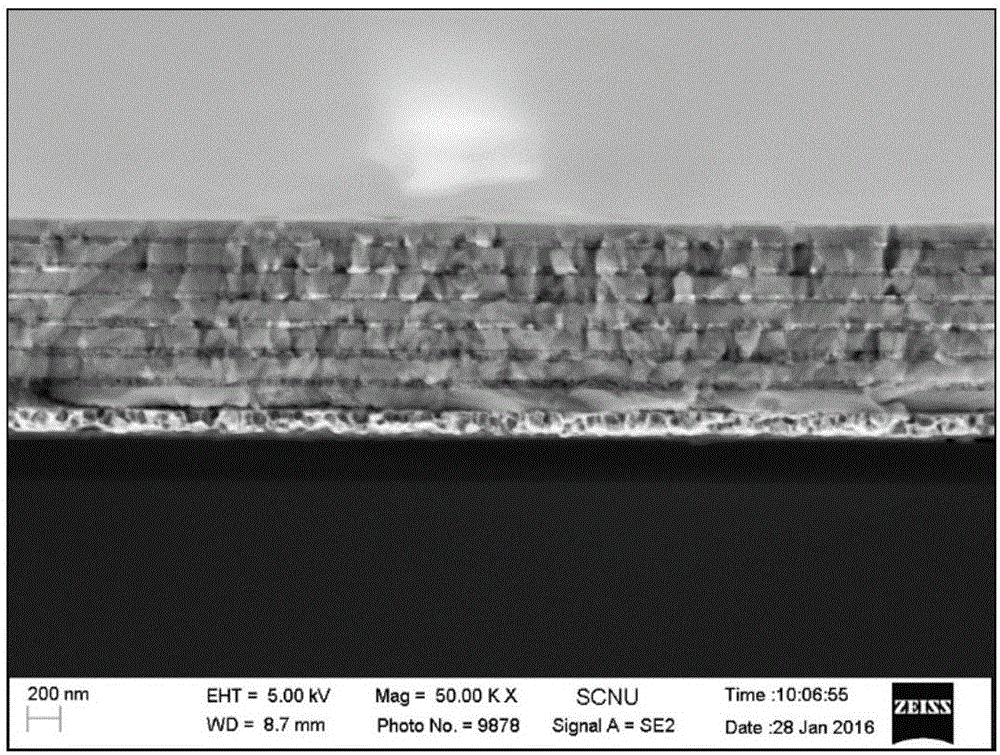

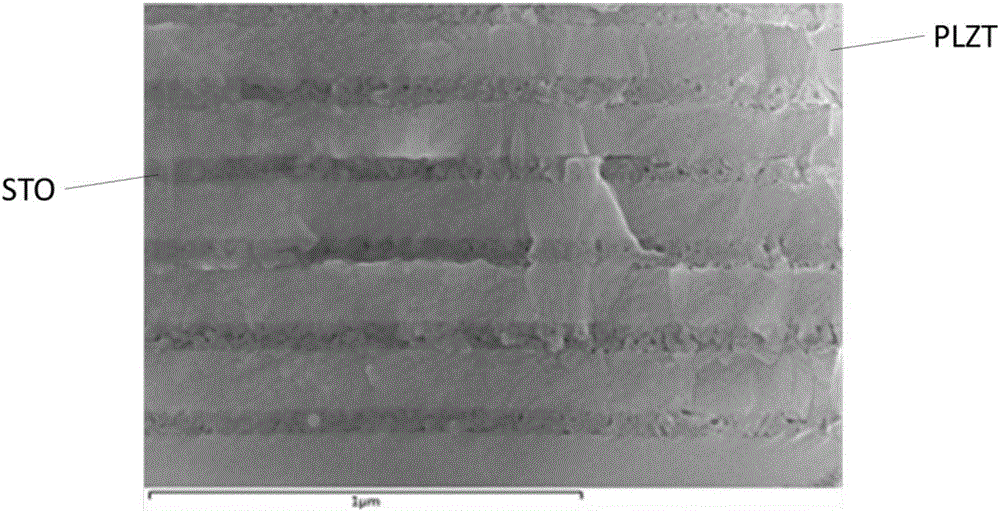

InactiveCN106531442AEnergy storage densityPlay the role of isolating chargeFixed capacitor dielectricSecondary layerEnergy storage efficiency

The invention discloses an anti-ferroelectric-paraelectric material coupled capacitor dielectric and a preparation method therefor. The anti-ferroelectric-paraelectric material coupled capacitor dielectric is formed by anti-ferroelectric PLZT and paraelectric STO which are distributed at intervals; the preparation method comprises the following steps of preparing PLZT sol and STO sol; uniformly performing spin coating on a Pt / Si substrate with the PLZT sol or the STO sol by a spin coater to obtain a first coating film layer; performing drying and annealing to obtain a first coating layer; performing spin coating on the first coating layer with the STO sol or the PLZT sol by the spin coater to obtain a second coating film layer; performing drying and annealing to obtain a second coating layer; and alternately performing the spin coating and annealing processes of the PLZT sol and the STO sol to obtain the anti-ferroelectric-paraelectric material coupled capacitor dielectric which is formed by anti-ferroelectric PLZT and paraelectric STO that are distributed at intervals. By virtue of the anti-ferroelectric PLZT-paraelectric STO coupling structure, the shortcoming of the poor voltage resistance of the pure anti-ferroelectric PLZT is effectively overcome, and the energy storage density and the energy storage efficiency of the capacitor dielectric are improved.

Owner:SOUTH CHINA NORMAL UNIVERSITY

Preparation method of low-cost paper environment-friendly take-out meal box

InactiveCN111150198AImprove mechanical propertiesImprove heat resistanceOther accessoriesNon-woven fabricsProcess engineeringSodium hydroxide

The invention provides a preparation method of a low-cost paper environment-friendly take-out meal box, and relates to the field of meal box materials, and the preparation method comprises the following steps: preparing wheat straw fibers; preparing ramie fibers; preparing hard cloth; adding waste corrugated paper into a crusher; crushing for 30-50 minutes at the speed of 2,000-2,500 r / min to obtain corrugated paper powder; soaking the corrugated paper powder in water for 25-30 hours; adding rice straw powder, calcium carbonate and starch; mechanically stirring at 1200-1500r / min for 2-5h, andadjusting the pH value of the system to 10 by using a sodium hydroxide solution to obtain thick slurry; heating and raising the temperature to 40 to 50 DEG C; soaking the hard cloth for 5 to 10min andthen fishing out the hard cloth; drying at the temperature of 70-80 DEG C to obtain sheets, taking a plurality of sheets for hot press molding to obtain a meal box body, adhering a layer of high-temperature-resistant film to the inner surface of the meal box body, and heating and curing at the temperature of 50-60 DEG C. According to the paper environment-friendly take-out meal box, the excellent mechanical property, heat resistance and water resistance of the meal box can be guaranteed while the low cost is guaranteed.

Owner:安徽硕通网络科技有限公司

Manufacturing method of semiconductor device

PendingCN112563286AGuaranteed electrical performanceAvoid the phenomenon that the size is enlargedSolid-state devicesSemiconductor devicesEtchingDevice material

The invention provides a manufacturing method of a semiconductor device. The manufacturing method comprises the following steps: providing a substrate with a first stacking structure on a surface, forming a plurality of first channel through holes penetrating through the first stacking structure to a substrate, and forming a first filling layer in each first channel through hole; forming a first gate isolation groove penetrating through the first stack structure to the substrate, enabling the first gate isolation groove to be located between the adjacent first channel through holes, and forming a second filling layer in the first gate isolation groove; forming a second stacking structure on the first stacking structure, forming a second channel through hole penetrating through the second stacking structure to the first filling layer, and removing the first filling layer to enable the second channel through hole to be connected with the first channel through hole; and forming a second gate isolation groove penetrating through the second stack structure to the second filling layer, and removing the second filling layer to enable the second gate isolation groove to be connected with the first gate isolation groove. The step-by-step etching of the gate isolation groove can better control an etching key size, and the electrical performance of the device is ensured.

Owner:YANGTZE MEMORY TECH CO LTD

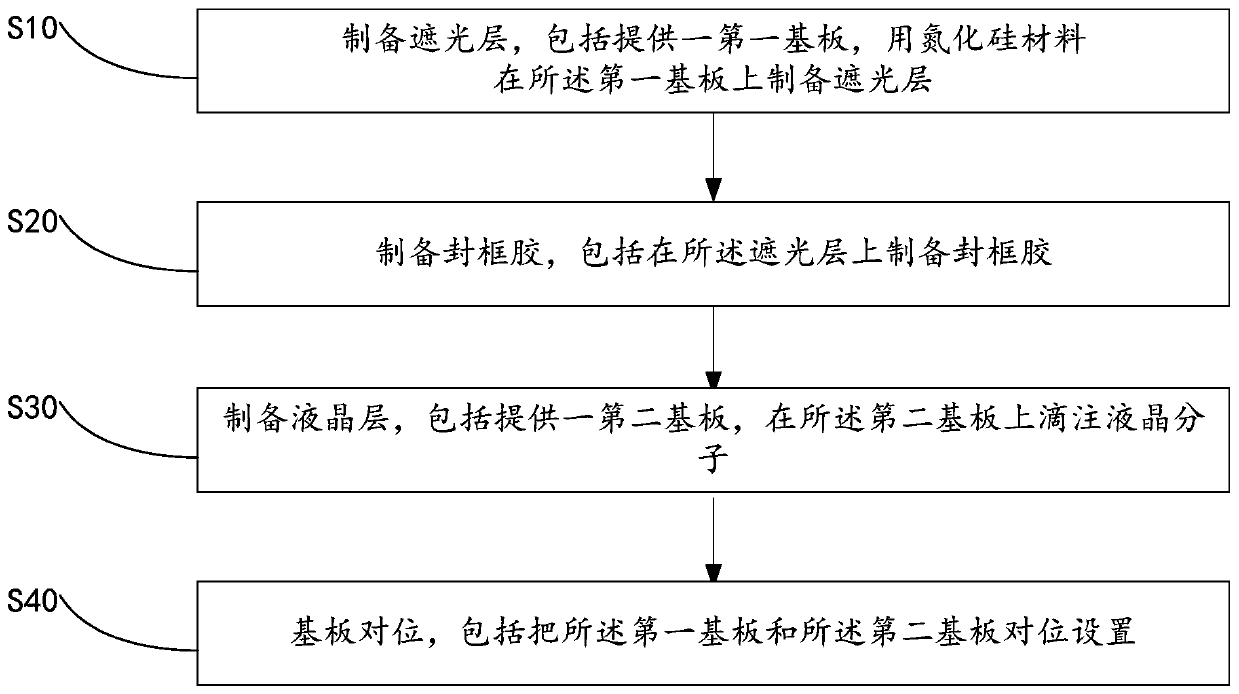

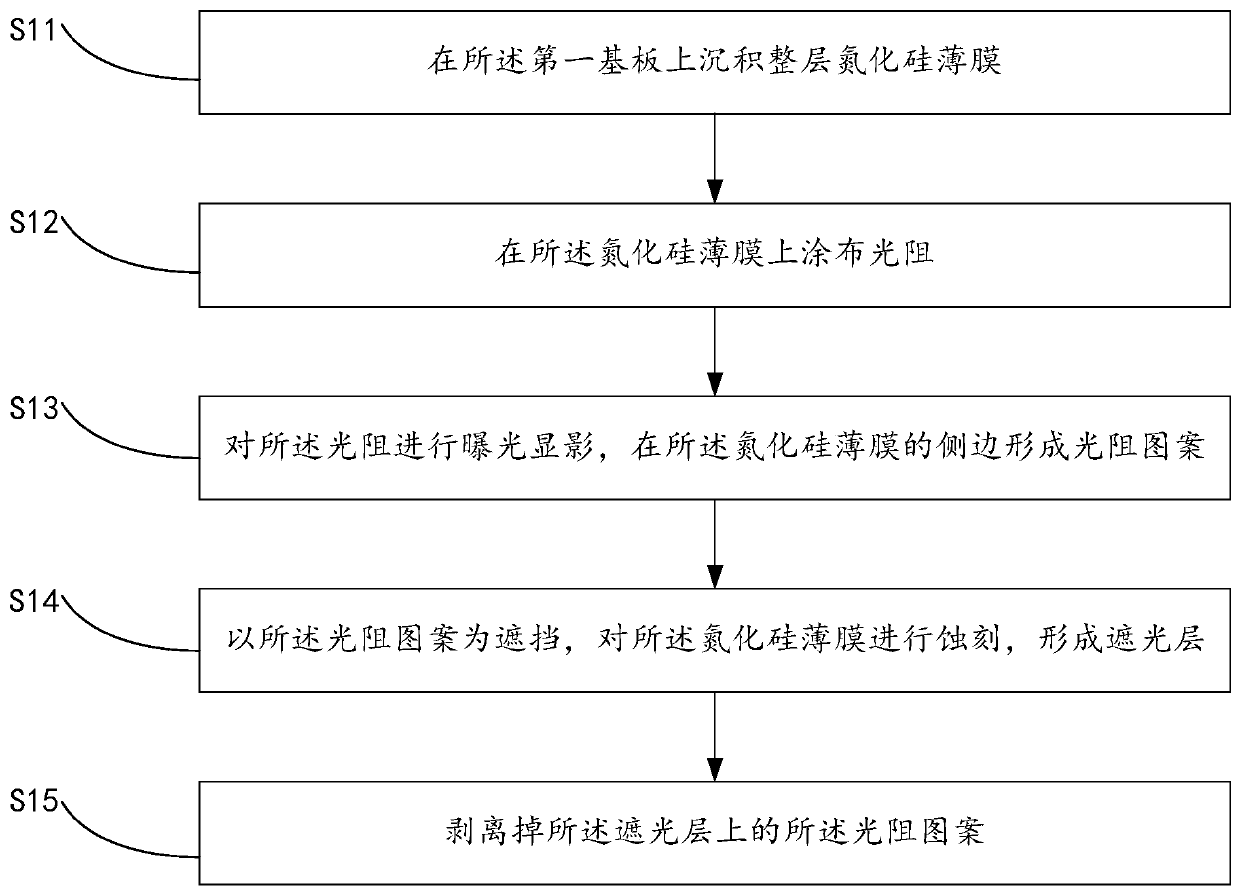

Liquid crystal display panel and preparation method thereof

InactiveCN111290161AImprove display qualityGood shading effectNon-linear opticsCrystallographyPhysical chemistry

The invention provides a liquid crystal display panel and a preparation method thereof. The preparation method of the liquid crystal display panel comprises the steps: a first substrate is provided, asilicon nitride film is prepared on the first substrate, a shading layer is formed on the side edge of the first substrate through a yellow light process, and frame sealing glue is prepared on the shading layer; a second substrate is provided, and liquid crystal molecules are instilled on the second substrate; and then the first substrate and the second substrate are arranged in an aligned mode.The shading layer is prepared by replacing a black matrix with silicon nitride, so that the shading effect of the shading layer of the liquid crystal display panel is improved.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS TECH CO LTD

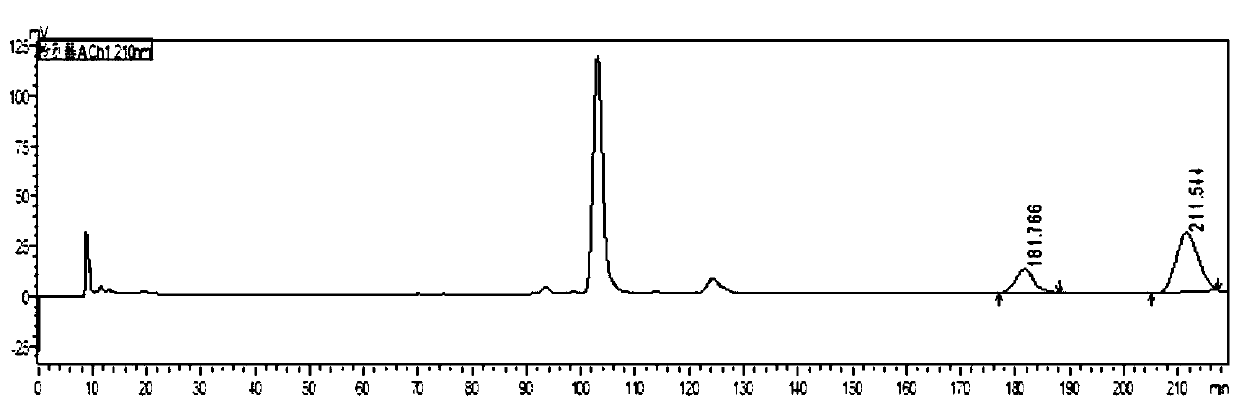

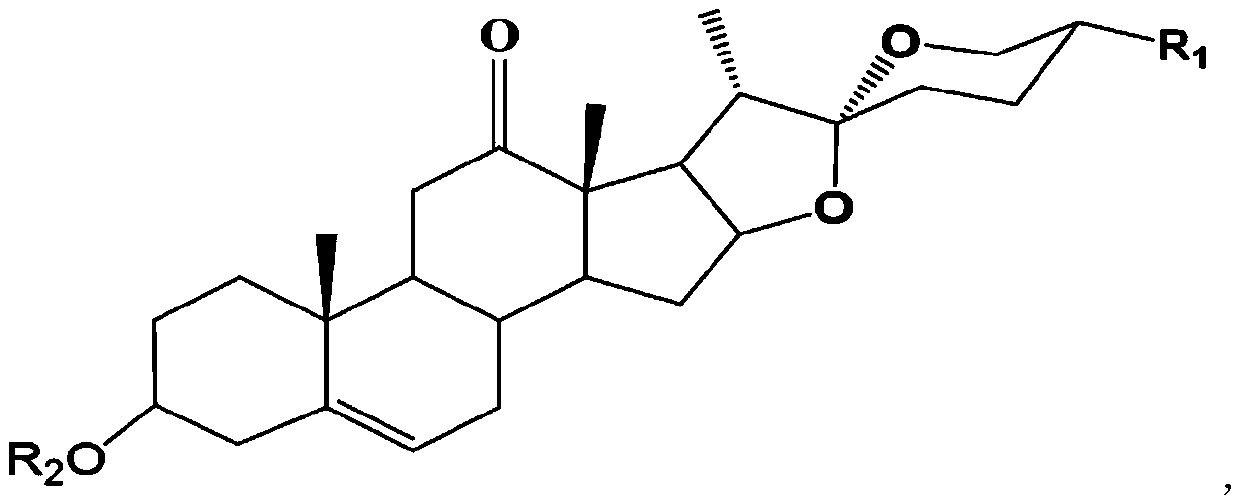

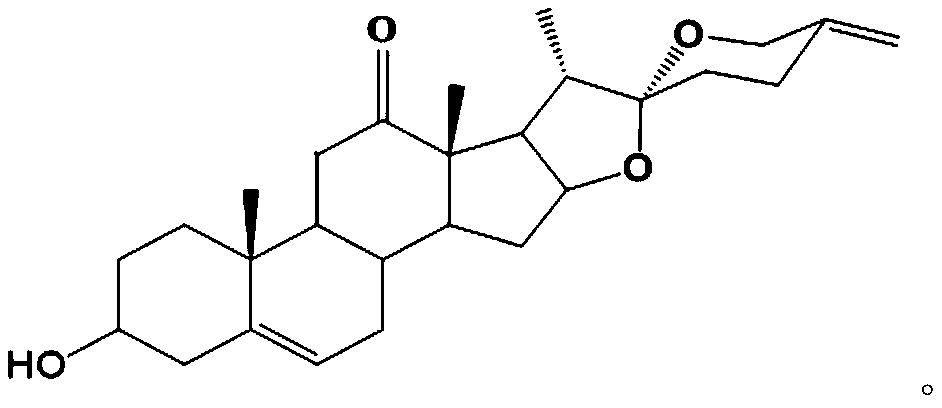

Polygonatum sibiricum steroid sapogenin and preparation method and application thereof

PendingCN110507662AToxic and side effectsDifficult to penetrateOrganic active ingredientsNervous disorderResearch resultOligosaccharide

The invention discloses application of polygonatum sibiricum steroid saponin and polygonatum sibiricum steroid sapogenin in preparation of a drug for treating or preventing Alzheimer's disease. The polygonatum sibiricum steroid saponin and polygonatum sibiricum steroid sapogenin have the structure as shown in the specification, wherein R1 represents C1-C6 alkyl or alkenyl, and R2 represents H or monosaccharide or oligosaccharide. Pharmacological activity research results show that the polygonatum sibiricum steroid saponin and the polygonatum sibiricum steroid sapogenin have good effects of preventing and treating senile dementia.

Owner:江西省药品检验检测研究院 +1

Dye absorption laundry bag

InactiveCN107476034ALow costStop sheddingIroning apparatusTextiles and paperDye absorptionEngineering

The invention discloses a dye absorption laundry bag which comprises a laundry bag body formed by dye absorption non-woven fabric. A draw string or a zipper is arranged at an opening of the laundry bag body. The dye absorption non-woven fabric comprises a non-woven fabric layer, a dye absorption layer and a color protection layer, wherein the dye absorption layer is coated on the non-woven fabric layer, the color protection layer is coated on the dye absorption layer, and the non-woven fabric layer is the outmost layer of the laundry bag body. The dye absorption laundry bag can be effectively prevent decoloring, color crossing and full deformation in clothes washing and is convenient and easy to use.

Owner:诺圆环保科技(苏州)有限公司