Time sequence determining method and device of integrated circuit chip

A technology of integrated circuits and chips, applied in the field of timing determination of integrated circuit chips, can solve the problem of inability to take into account the speed and accuracy of timing analysis, and achieve the effect of achieving speed and accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

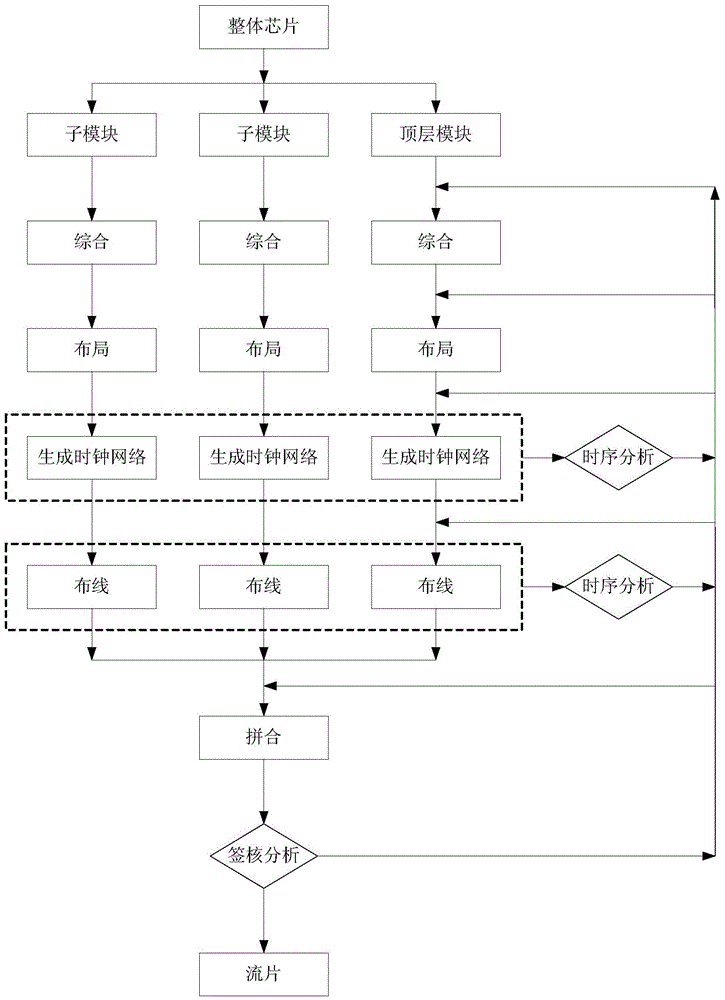

[0035] The technical solution of the present invention will be described in further detail below through specific embodiments and accompanying drawings.

[0036] Figure 4 A schematic flowchart of an embodiment of a method for determining timing of an integrated circuit chip provided by the present invention. Such as Figure 4 As shown, the method may include:

[0037] S401, determine the top-level module included in the integrated circuit chip to be designed and the gate unit included in at least two sub-modules and the position of the gate unit on the integrated circuit chip, and determine the logical connection relationship between the gate units, the gate unit includes a logic unit and sequential units;

[0038]Specifically, when the scale of the integrated circuit is large, the automatic design tool is limited by the scale of the problem that its own algorithm can handle, and cannot handle the physical design problem of a large-scale chip at one time. Therefore, it is ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More