Error correcting code decoder

A decoder and error-correcting code technology, applied in the field of modern digital communication systems, can solve problems such as poor configurability, limited operating speed, and inability to process in parallel, achieving low resource utilization, strong error-correcting capabilities, and reduced decoding The effect of delay

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] The preferred embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings, so that the advantages and features of the present invention can be more easily understood by those skilled in the art, so as to define the protection scope of the present invention more clearly.

[0020] see figure 1 and figure 2 , the embodiment of the present invention includes:

[0021] An error correction code decoder, comprising:

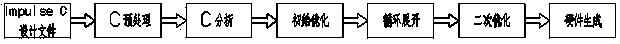

[0022] 1) The generation process from Impulse C software to FPGA hardware:

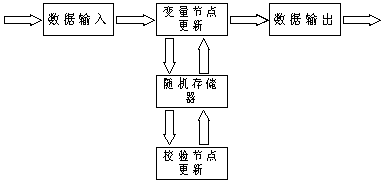

[0023] Impulse C design files are preprocessed by C, and then analyzed in C language; in the stage of C language analysis, the compiler determines the hardware and software processes in the application; next, the initial optimization process is performed, and in the loop unrolling stage, the compiler will correspondingly The loop is converted into an equivalent parallel statement; after secondary optimization, a simulatable...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More