Method and apparatus for an active negative-capacitor circuit

A capacitor and negative capacitance technology, which is used in the field of active negative capacitor circuits and devices, can solve problems such as increased rebound and increased power loss

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] The invention described in this specification can be used in any wired or wireless system or any low supply voltage design. These techniques can be used for any amplifier design, ADC design, or PGA and ADC interface design. These techniques can be extended to other circuit designs where increased bandwidth between two interfaces, reduced clock bounce, or matched transistors within the circuit are desired.

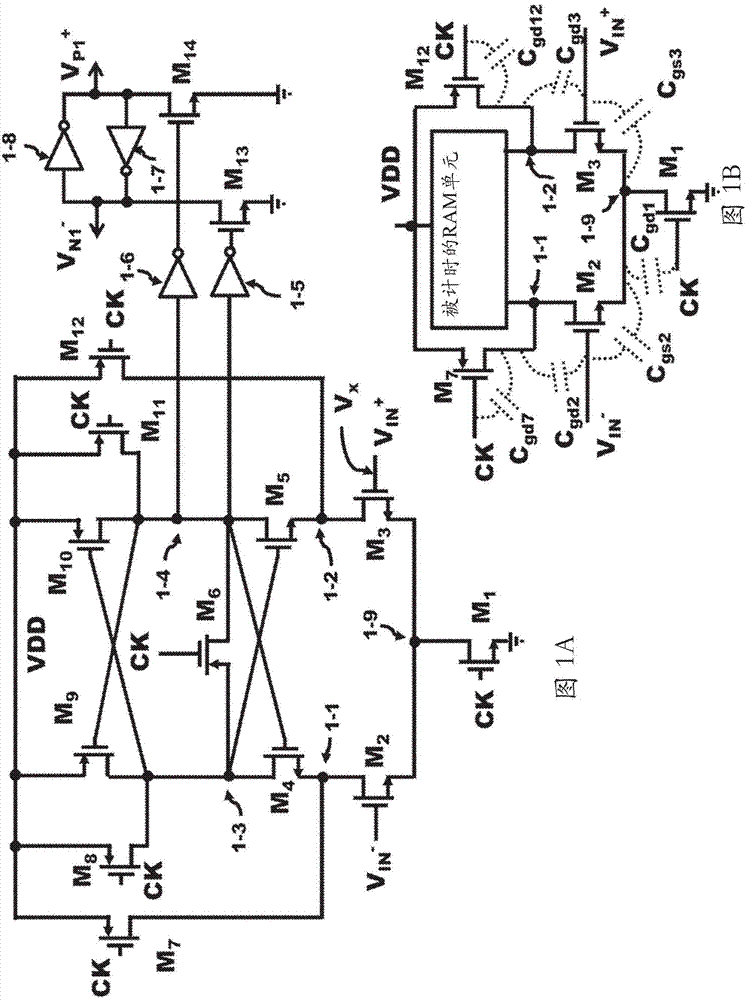

[0041] Figure 1A The comparator clocked in the first preamplifier stage is shown in . The basic construction of a clocked preamplifier stage includes a ground switch M 1 , the ground switch has a gate coupled to a clock CK. m 1 The drains 1-9 are coupled to two N-channel transistors M 2 and M 3 source. m 2 by V IN - driven while M 3 by another differential input signal V IN+ driven by. m 2 The drain of is coupled to 1-1 and is also coupled to a P-channel transistor M controlled by the same clock CK 7 the drain. m 3 The drains 1-2 of are coupled to a ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More