Semiconductor device and forming method thereof

A semiconductor and device technology, applied in the field of semiconductor devices and their formation, can solve the problems of small metal gate height and other problems

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

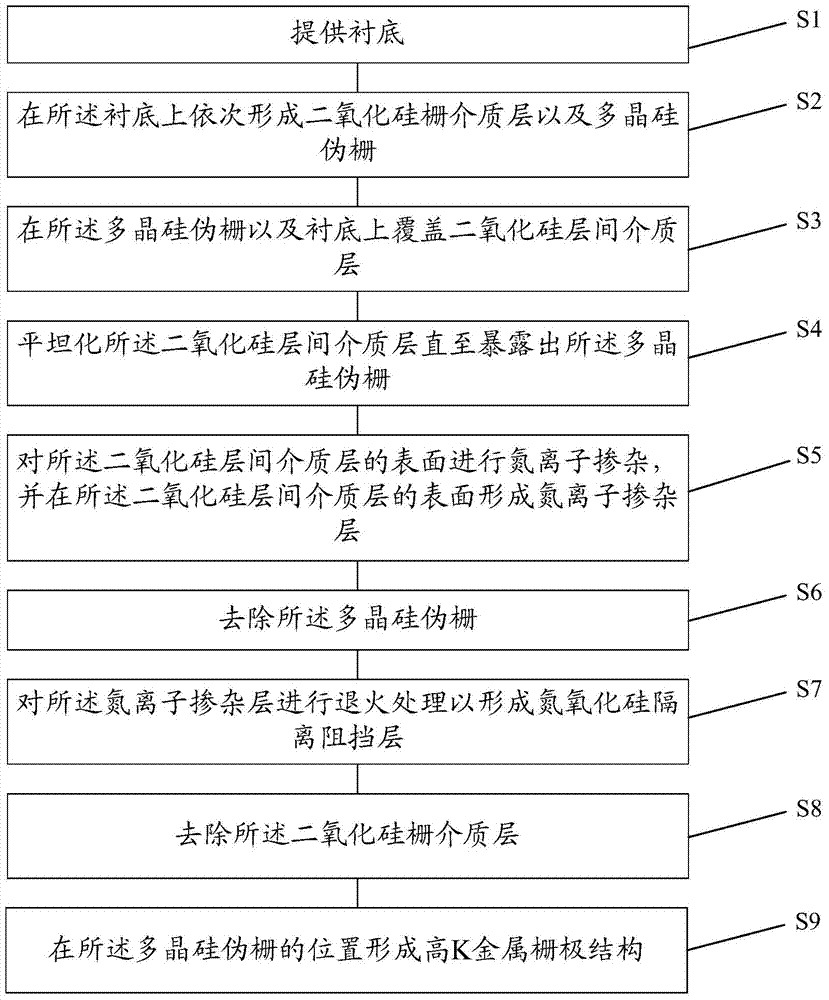

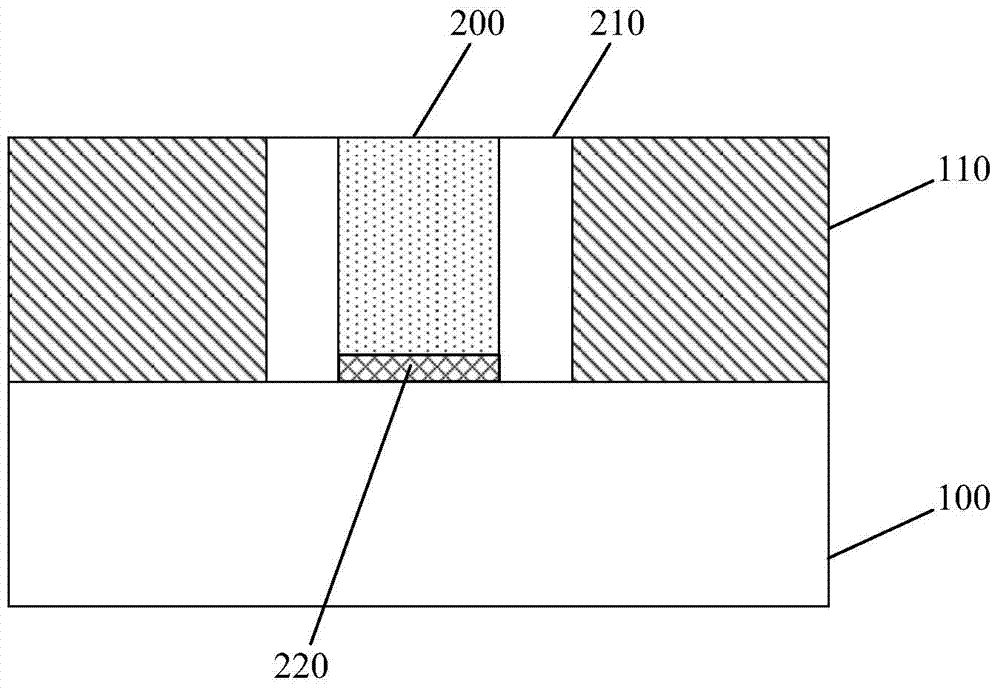

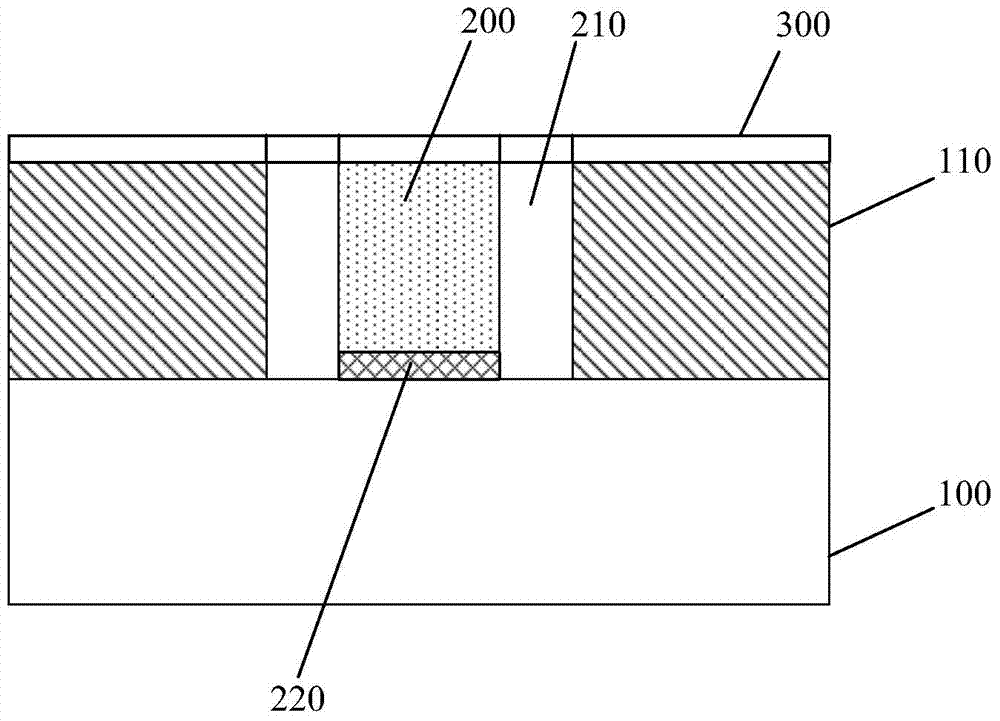

[0047] In the existing gate-last process, it is easy to affect the interlayer dielectric layer during the process of removing the dummy gate. The reason is that a relatively dense gate dielectric layer is formed at the bottom of the dummy gate, and when the dummy gate is removed, the gate dielectric layer also needs to be removed. In the process of removing the gate dielectric layer, the surface of the interlayer dielectric layer is easily consumed (loss) to a certain extent, so that the height of the interlayer dielectric layer becomes lower. The reduction in the height of the interlayer dielectric layer results in a corresponding reduction in the height of the subsequently formed gate.

[0048] In order to solve the technical problem, the present invention provides a method for forming a semiconductor device, performing ion doping on the surface of the interlayer dielectric layer to form a doped layer on the surface of the interlayer dielectric layer, the doping The layer c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More