Forming method of fin type field effect transistor

A fin field effect and transistor technology, applied in semiconductor devices, semiconductor/solid state device manufacturing, electrical components, etc., can solve problems such as poor performance of fin field effect transistors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

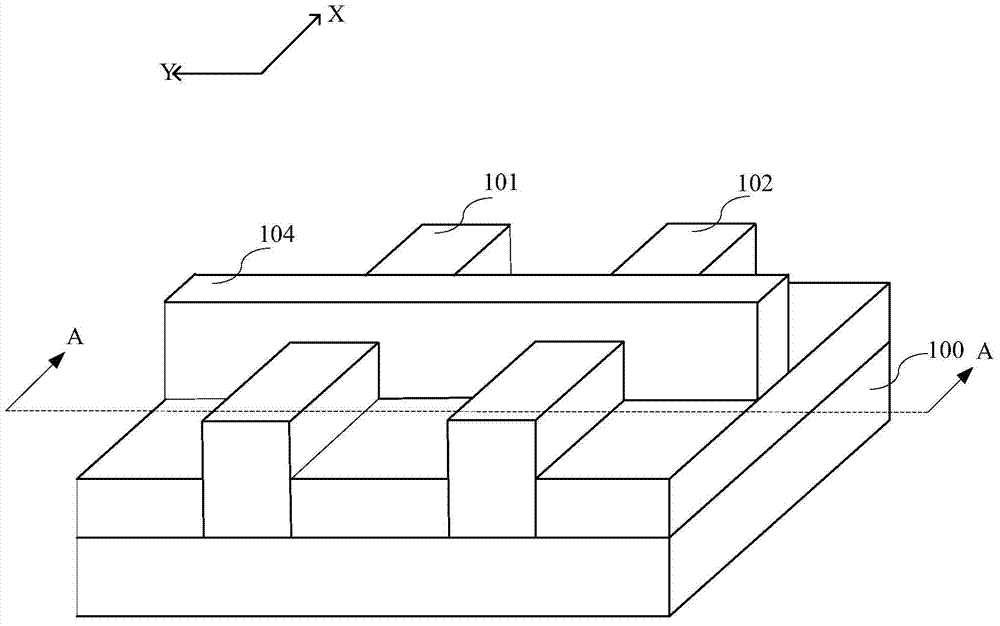

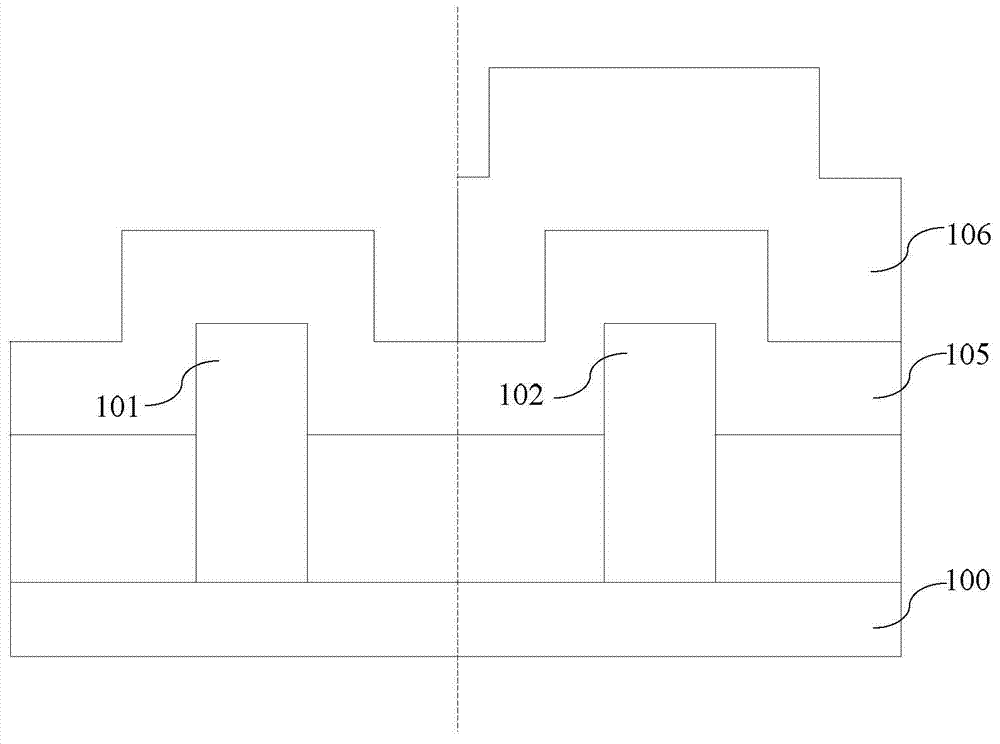

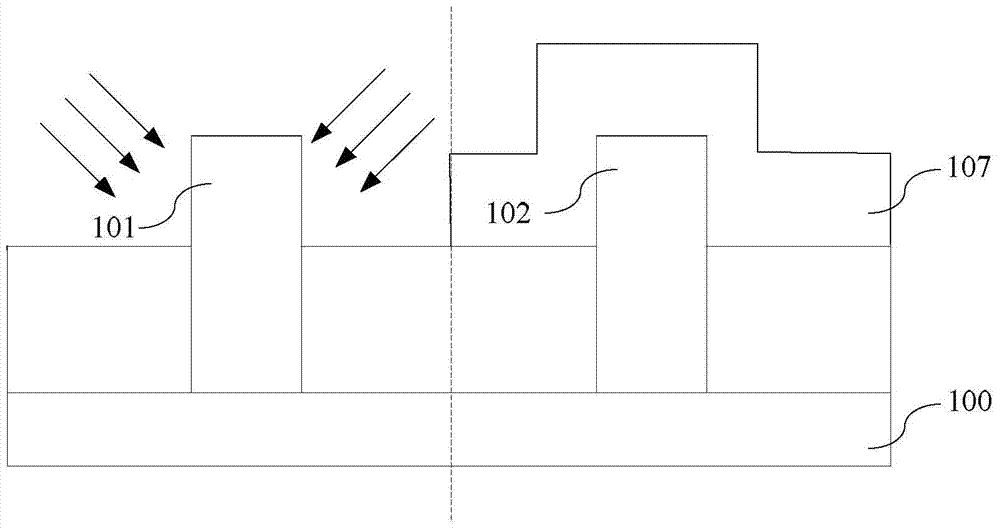

[0044] refer to figure 1 If ion implantation is directly performed on the first fins 101 on both sides of the gate 104, the ion implantation process will make most of the single crystal silicon in the first fins 101 be converted into amorphous silicon. Compared with single crystal silicon, the grain size of amorphous silicon is not uniform, and the arrangement is disorderly. Therefore, the resistance value of the first fin portion 101 composed of amorphous silicon is relatively large. In addition, it is difficult to determine the resistance or other physical properties of the first fin portion 101 composed of amorphous silicon, so that it is difficult to control the overall physical properties of the subsequently formed FinFET.

[0045]In the process of forming the first fin field effect transistor, a patterned amorphous carbon layer is formed on the substrate, exposing the first fin portion 101 and the gate thereon. Next, the substrate is heated, and high-temperature ion imp...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More