Semiconductor device and method for forming same, method for improving wafer dicing yield

A semiconductor and yield technology, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., can solve the problem of chip performance and service life decline, chips are easily damaged, and wafer cutting yield is low, etc. problems, to achieve the effect of improving wafer cutting yield and good interconnection performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

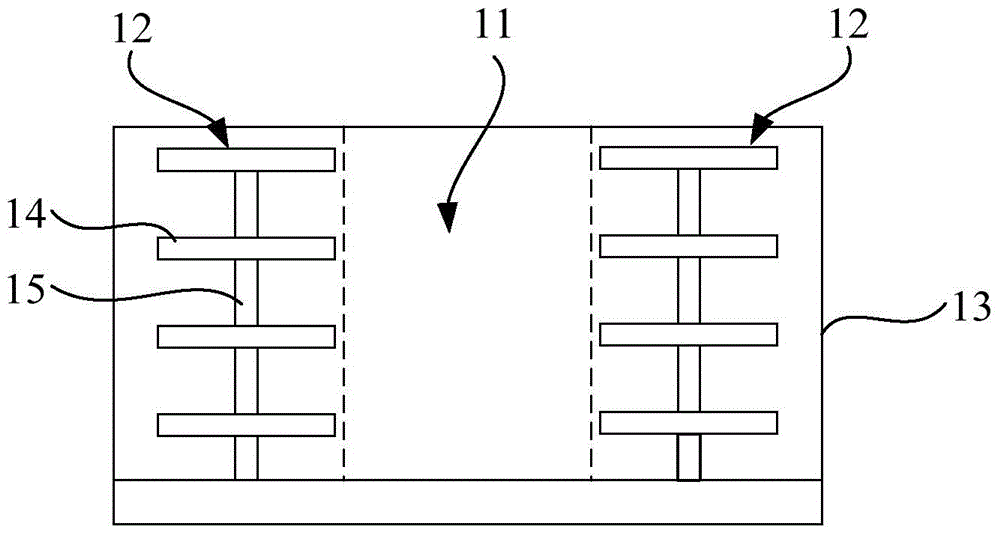

[0040] In order to make the above objects, features and advantages of the present invention more comprehensible, specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

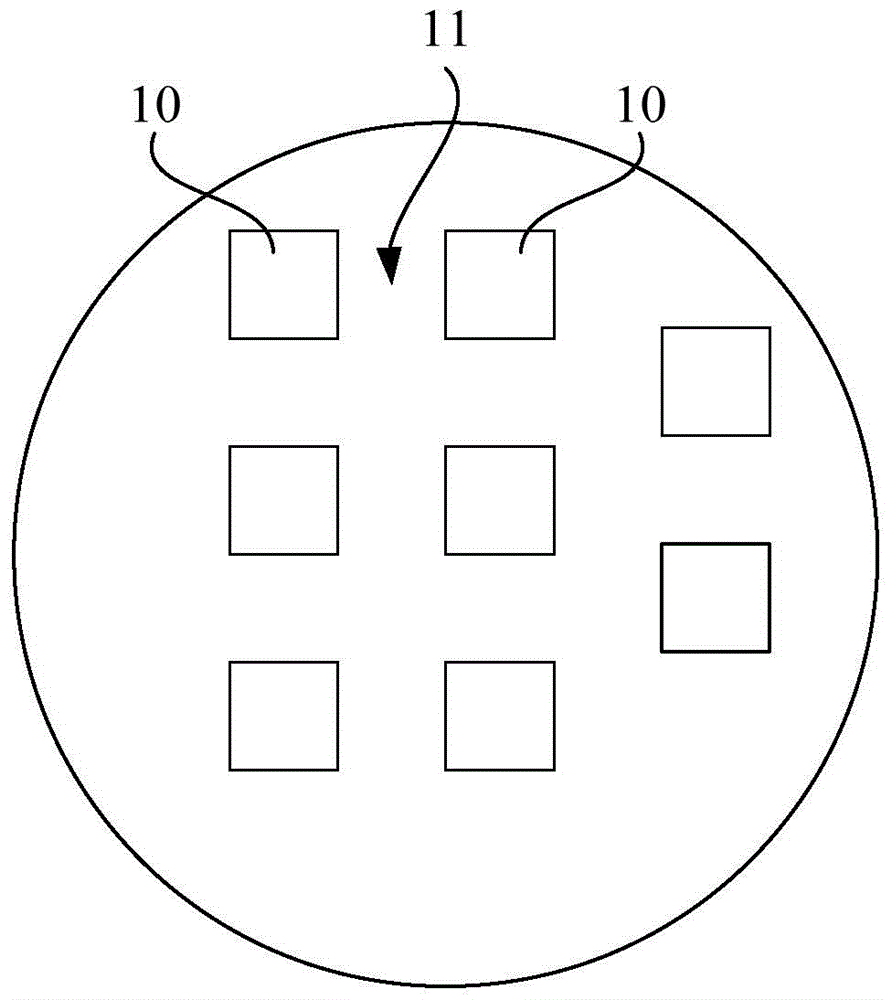

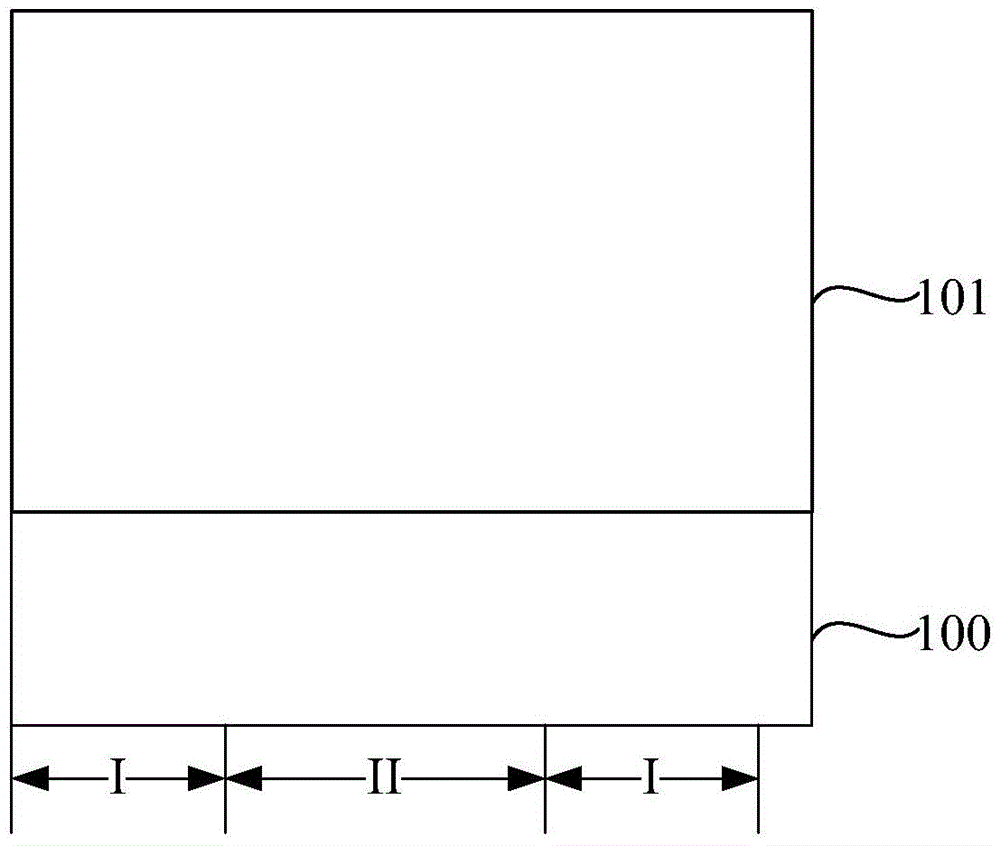

[0041] refer to image 3 A wafer 100 is provided, and the wafer 100 is divided into a plurality of chip regions I and a dicing line II located between two adjacent chip regions I. Cutting lane II is the subsequent wafer cutting position.

[0042] A device structure located in the wafer is formed in the chip area I, and the device structure is a functional device that can realize a specific function. However, no functional device is formed in the wafer at the position of dicing line II.

[0043] In a specific embodiment, the wafer 100 may be a silicon wafer, or may be a germanium, silicon germanium, gallium arsenide or silicon-on-insulator wafer. Those skilled in the art can select wafers according to needs, so the type of wafers should ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More