Clock signal generation circuit, grid driving circuit, display panel and display device

A gate drive circuit and clock signal technology, which is applied in the field of gate drive circuit, clock signal generation circuit, display panel and display device, can solve problems such as distortion, heavy load, and clock signal distortion, and achieve the target clock signal accuracy, Avoid insufficient charging and ensure the effect of display effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] Specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings. It should be understood that the specific embodiments described here are only used to illustrate and explain the present invention, and are not intended to limit the present invention.

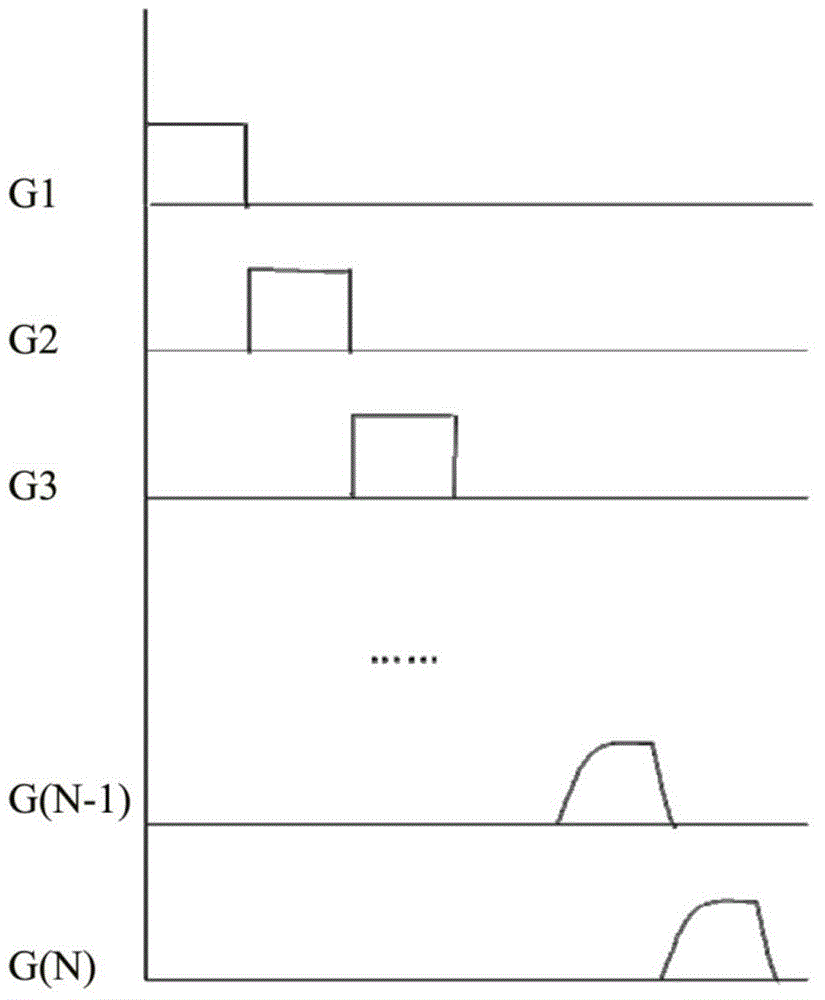

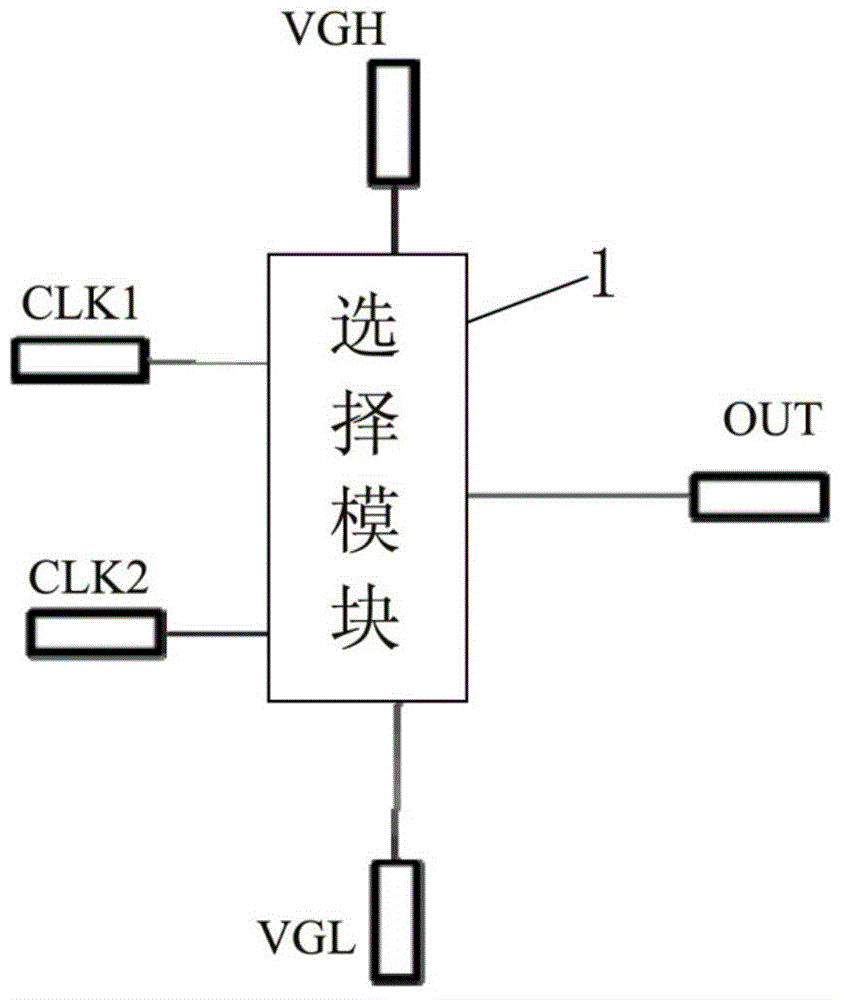

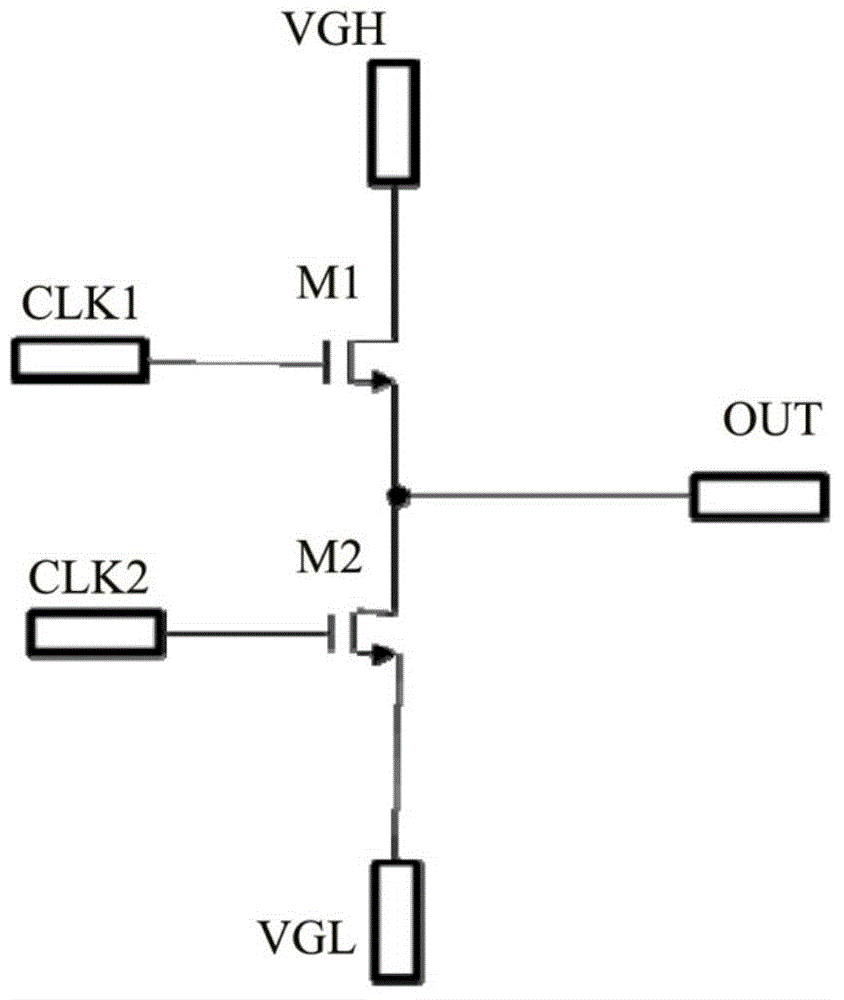

[0030] The present invention provides an implementation manner of a clock signal generation circuit, figure 2 It is a schematic diagram of a clock signal generation circuit provided by an embodiment of the present invention. Such as figure 2 As shown, in this embodiment, the clock signal generating circuit includes a selection module 1, a high-level signal input terminal VGH, a low-level signal input terminal VGL, a first clock signal terminal CLK1, and a second clock signal terminal CLK2, And the output terminal OUT; wherein, the first clock signal terminal CLK1 inputs the first clock signal to the selection module 1; the second clock signal terminal CLK2 i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More