Real-time binary image connected domain mark realizing method based on FPGA

A technology of connected domain labeling and implementation method, which is applied in the field of binary image connected domain labeling and achieves the effect of fast processing speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0042] The detailed structure of the present invention, application principle, function and effect, refer to the appended Figure 1-6 , which will be described through the following embodiments.

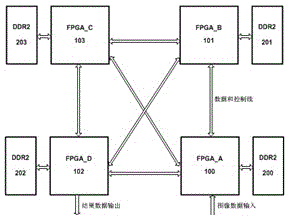

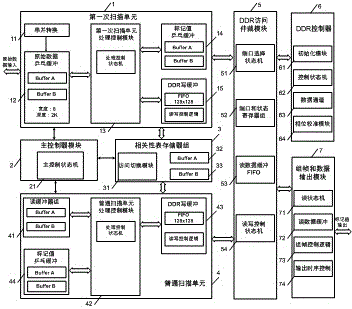

[0043] The hardware platform architecture of the present invention is as figure 1 As shown, it is composed of four symmetrical processing nodes, adopts VPX architecture, and uses high-speed serial interface for interconnection. In the present invention, the processing node realizes the architecture such as figure 2 As shown, it mainly includes seven main functional modules. These two parts have been described in detail in the summary of the invention.

[0044] The functions and specific design methods of each module in the system and processing nodes are described below, and the present invention is further explained, with the emphasis on explaining how the superscalar pipeline technology is embodied in the design and how to improve the system processing performance. In addition...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More