Array substrate, display panel, and manufacturing method of array substrate

A technology of array substrate and substrate substrate, which is applied in semiconductor/solid-state device manufacturing, instruments, semiconductor devices, etc., can solve problems such as signal breakage, copper surface bombardment, and transparent electrode oxidation and corrosion, and achieves improved reliability and low production cost. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

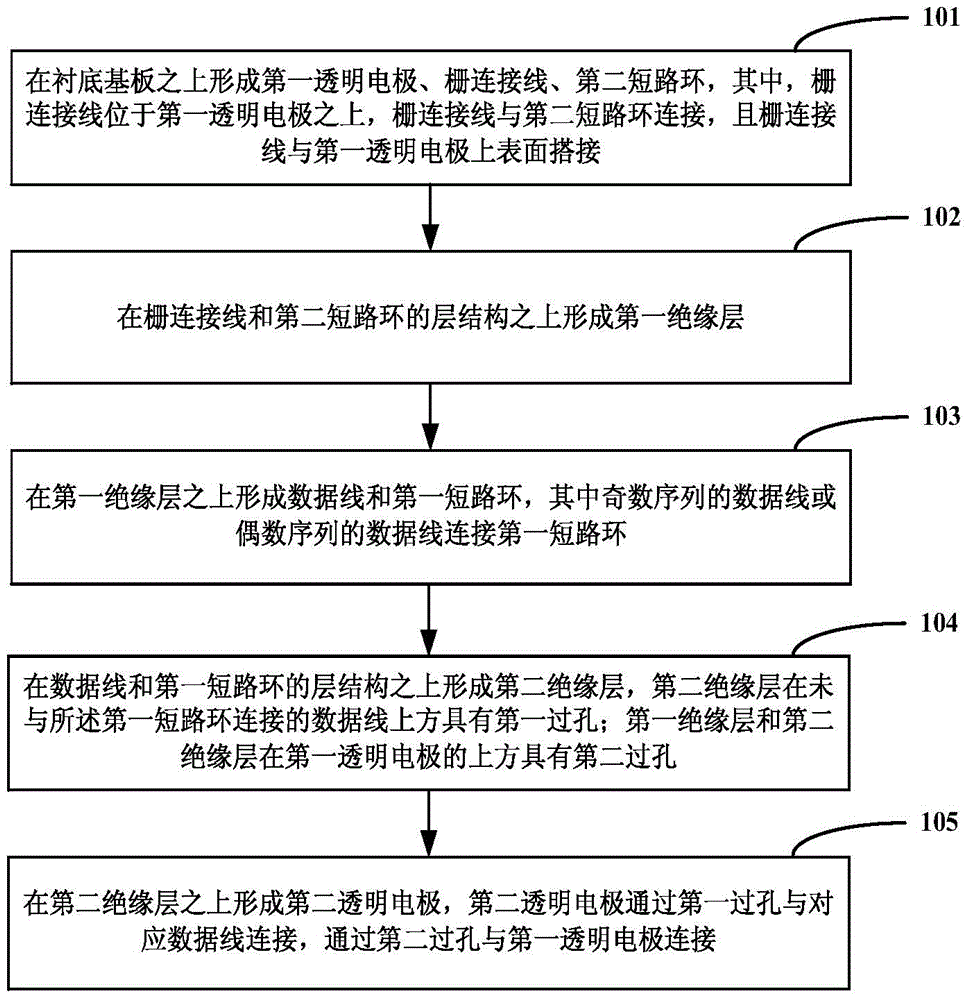

[0050] In order to improve the reliability of signal transmission at a via hole connected to a short-circuit ring on an array substrate, an embodiment of the present invention provides an array substrate, a display panel, and a method for manufacturing the array substrate. In order to make the purpose, technical solution and advantages of the present invention clearer, the following examples are given to further describe the present invention in detail.

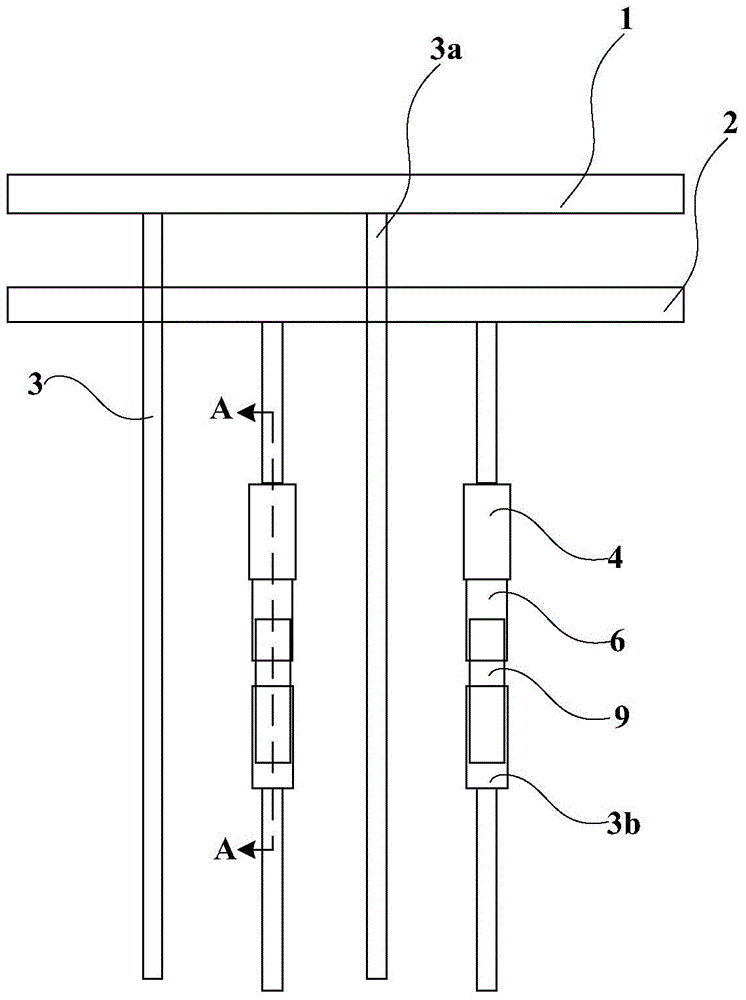

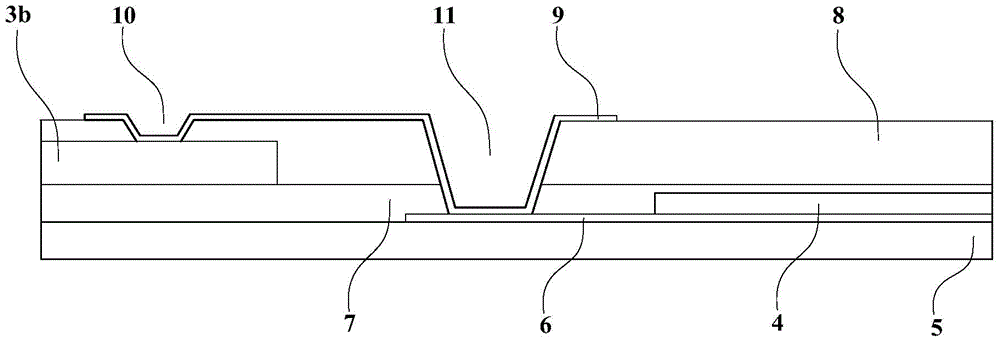

[0051] like figure 1 and figure 2As shown, the array substrate provided by the embodiment of the present invention includes a set of data lines 3 and a set of gate lines arranged crosswise, and a first short-circuit ring 1 and a second short-circuit ring 2 located in the peripheral area of the array substrate. The first short-circuit ring 1 is set on the same layer as a group of data lines 3, and the second short-circuit ring 2 is set on the same layer as a group of gate lines; in a set of data lines 3, two adjacent data ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More