Negative voltage level converting circuit inhibiting DC path

A DC path and conversion circuit technology, applied in the direction of logic circuit connection/interface layout, etc., can solve the problem of uncertainty of the working state of the level conversion circuit, and achieve the effect of ensuring high-reliability conversion, ensuring normal operation, and suppressing DC leakage.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

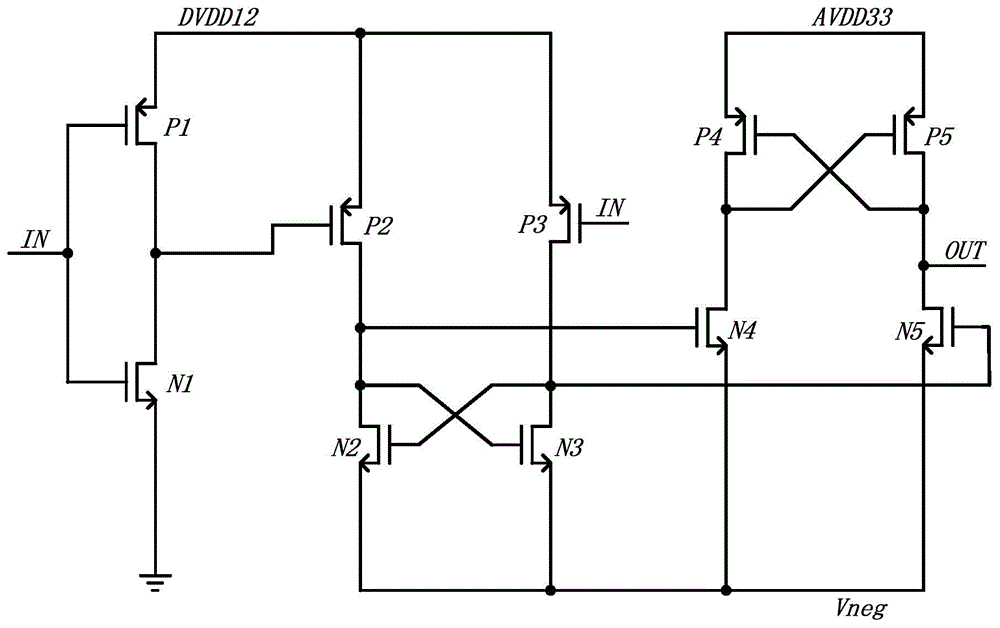

Image

Examples

Embodiment Construction

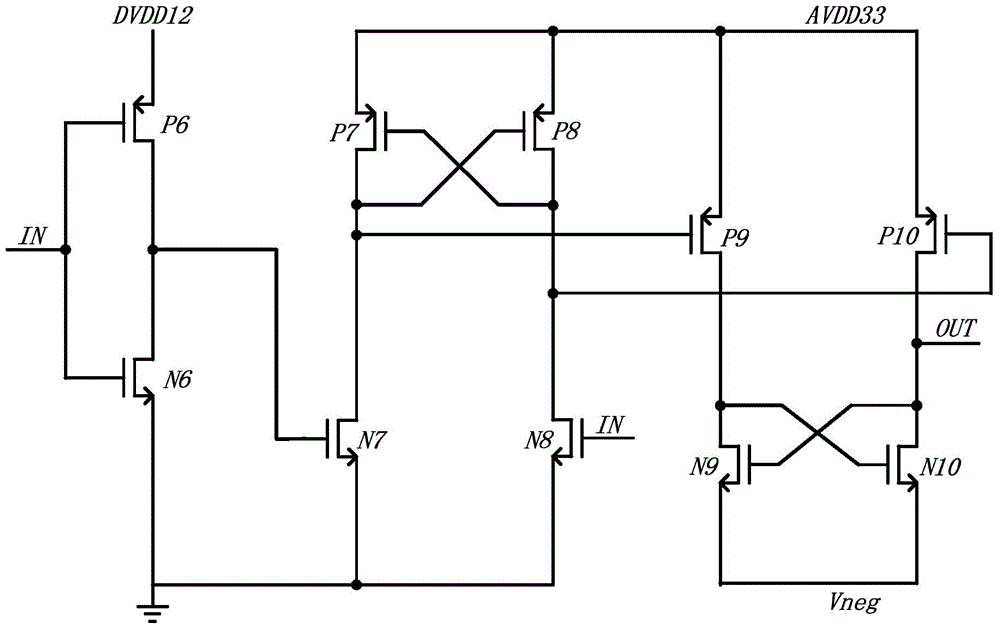

[0023] The present invention will be described in further detail below in conjunction with the accompanying drawings.

[0024] see figure 2 , the negative voltage level conversion circuit of the present invention includes five P-channel metal oxide semiconductor field effect transistors P6, P7, P8, P9, P10, and five N-channel metal oxide semiconductor field effect transistors N6, N7, N8 , N9, N10.

[0025] For the convenience of description, the P-channel MOSFET and the N-channel MOSFET will be referred to as P tube and N tube below.

[0026] DVDD12 is the 1.2V power supply voltage of the digital circuit, AVDD33 is the 3.3V power supply voltage of the analog circuit, and Vneg is a negative voltage signal. IN is an input signal between 0 and DVDD12, and OUT is an output signal between Vneg and AVDD33.

[0027] The negative voltage level conversion circuit of the present invention shown in the figure mainly includes the following branches:

[0028] The first branch, this br...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More