Task-level out-of-order multi-issue scheduler and scheduling method thereof

A multi-launcher and scheduler technology, applied in multi-program devices, resource allocation, etc., can solve the problems of low efficiency of correlation acquisition, instruction-level scheduler can not meet the design requirements of task-level coarse-grained scheduler, etc., and achieve parallel extraction Execution efficiency, high computing resource utilization efficiency, and the effect of efficient dynamic scheduling

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

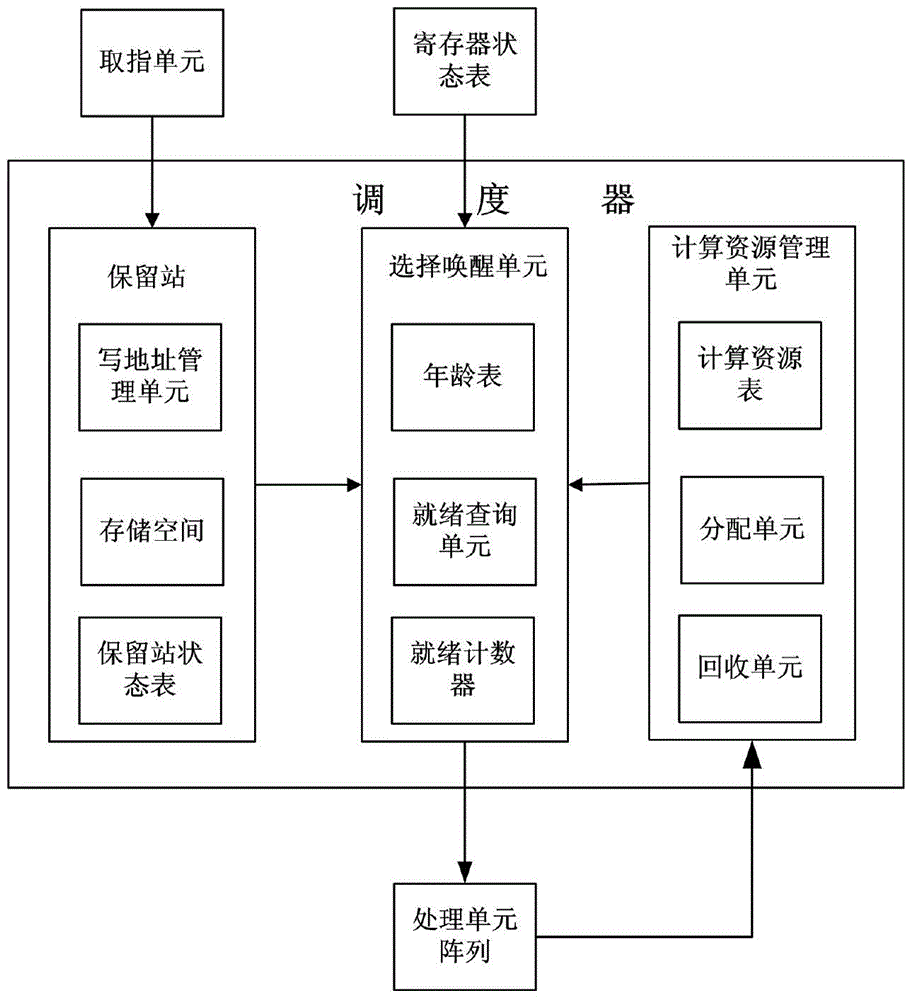

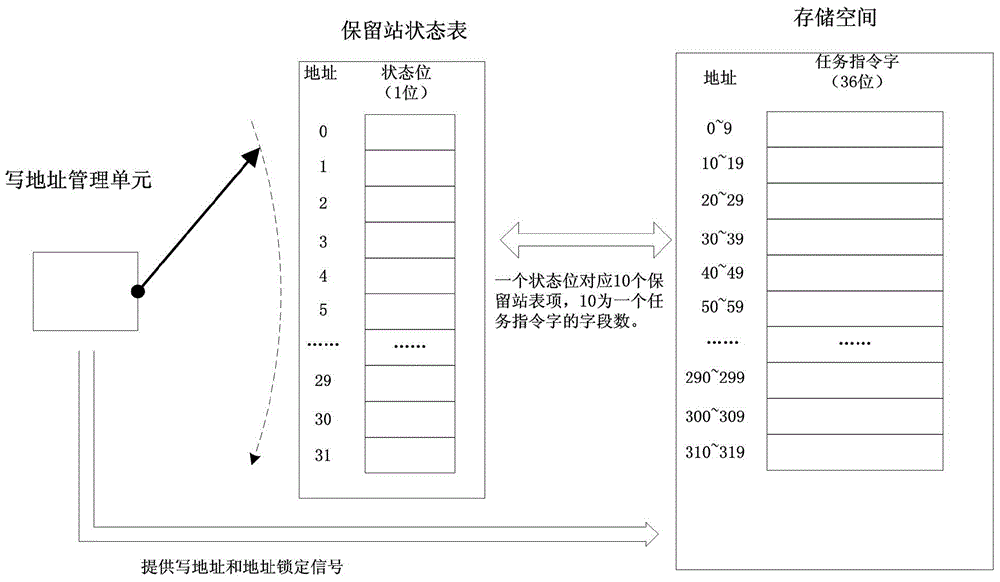

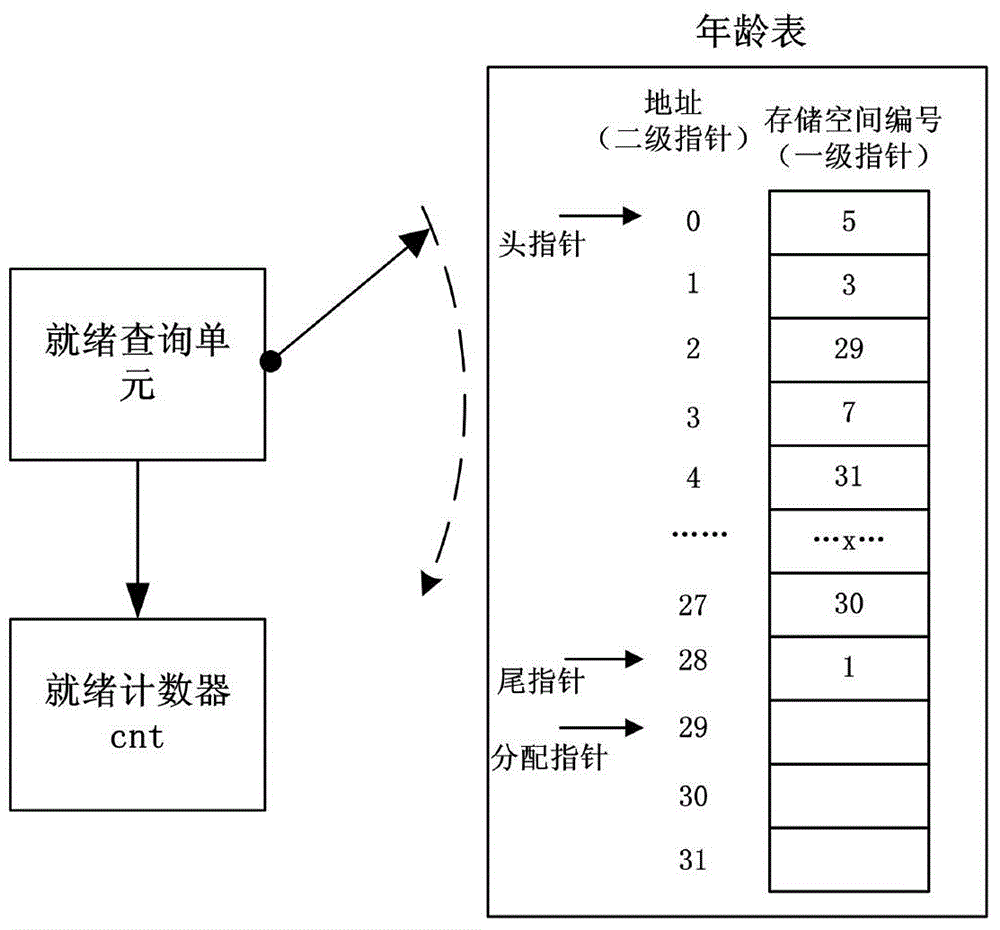

[0046] In this example, if figure 1 As shown, a task-level out-of-order multi-issue scheduler is arranged in a processor and is used to schedule M task instructions. The processor includes: an instruction fetch unit, a register state table and a processing unit array; the scheduler includes: Reserved station, selective wake-up unit and computing resource management unit; reserved station includes write address management unit, storage space and reserved station state table; selected wake-up unit includes age table, ready query unit and ready counter; computing resource management unit includes Calculation resource table, allocation unit and recycling unit;

[0047] Usually, a processor that supports dynamic scheduling includes a controller and a processing unit array. The controller includes an instruction fetching and decoding unit, a register renaming unit, a scheduler, a submission unit, physical registers, a register status table, etc.; The decoding unit obtains task inst...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More