Radio frequency LDMOS device and manufacturing method thereof

A manufacturing method and device technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., to achieve the effects of improving frequency characteristics, reducing equivalent dielectric constant, and reducing gate-to-drain capacitance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

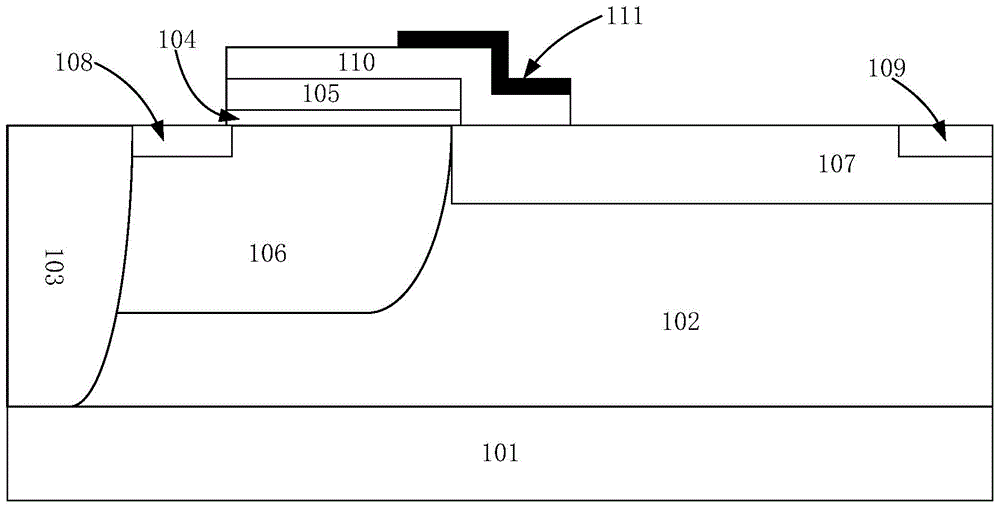

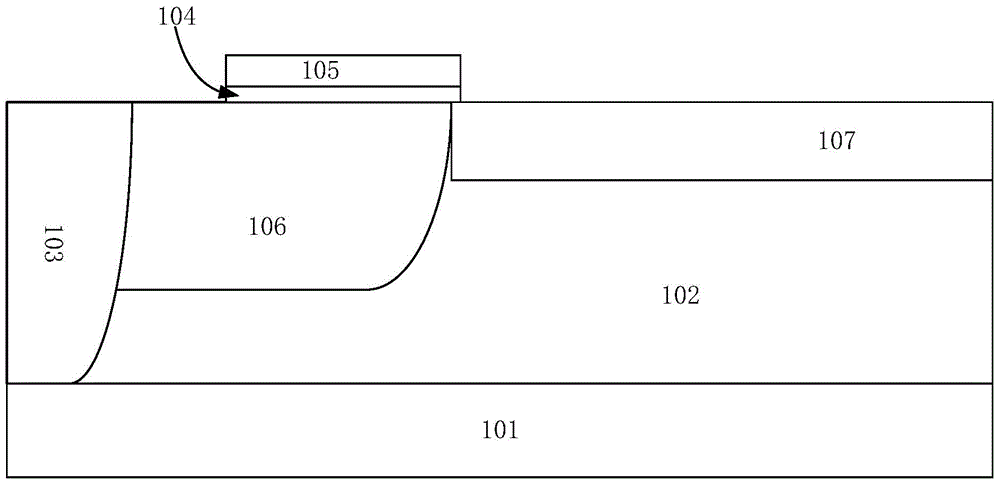

[0030] Such as figure 2 As shown, this example includes a P-type substrate 101 and a P-type epitaxial layer 102 located on the upper surface of the P-type substrate 101; the P-type epitaxial layer has P+sinker 103 and N-type lightly doped regions 107 on both sides, and the There is a P-type well region 106 between the P+sinker 103 and the N-type lightly doped region 107; the upper layer of the P-type well region 106 has a first N-type heavily doped region 108, and the first N-type heavily doped region 108 It is connected to the side of the P+sinker 103; the upper layer of the N-type lightly doped region 107 has a second N-type heavily doped region 109 on the side away from the P-type well region 106; the upper surface of the P-type well region 106 has a gate oxide Layer 104, the upper surface of the gate oxide layer 104 has a polysilicon gate 105, and the gate oxide layer 104 and the polysilicon gate 105 form a gate structure; the upper surface of the gate structure and the s...

Embodiment 2

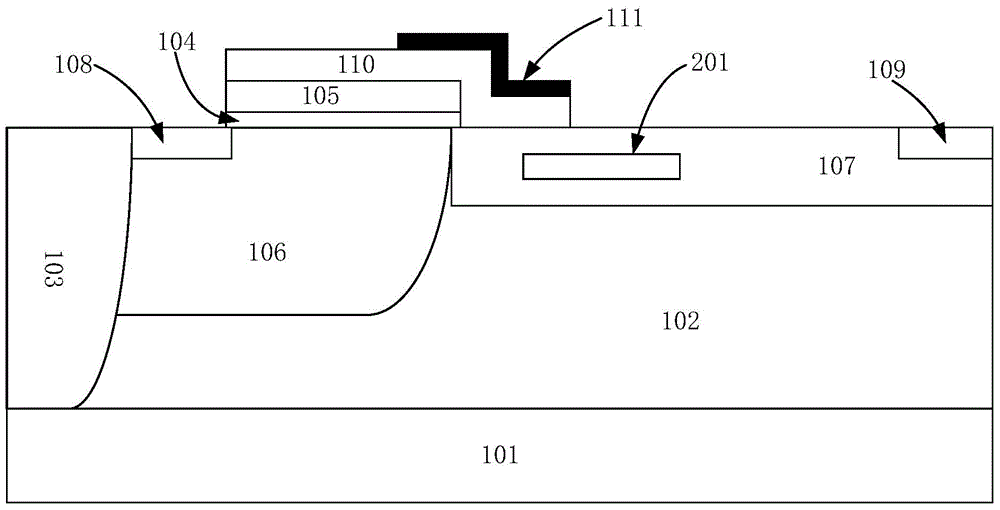

[0046] Such as Image 6 As shown, on the basis of Embodiment 1, the oxide layer region 201 is changed into two regions of the oxide layer region 601 and the oxide layer region 602 located on the same horizontal plane, so as to achieve more flexible control of the influence of the oxide layer region on device performance . It can also be changed into multiple oxide layer regions on the same horizontal plane according to specific circumstances.

Embodiment 3

[0048] Such as Figure 7 As shown, on the basis of the first embodiment, this example has a device structure with double-layer field plates. The principle of this example is the same as that of Embodiment 1. The invention is also applicable to device structures having multilayer field plates.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More