Device and method used for SDH (Synchronous Digital Hierarchy) clock jitter test

A clock jitter and clock recovery technology, applied in multiplex communication, time division multiplexing systems, electrical components, etc., can solve the problem of inaccurate measurement of clock jitter signal amplitude and frequency, and increase the cost of SDH clock jitter measurement. , reduce the signal signal-to-noise ratio and other issues, to achieve the effect of reducing the SDH clock jitter test error, avoiding the use of test instruments, and reducing the use of

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

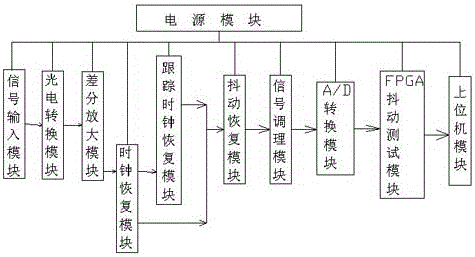

[0052] Such as figure 1 As shown, a device for SDH (Synchronous Digital Hierarchy) clock jitter test described in the present invention includes a power supply module, a signal input module, a photoelectric conversion module, a differential amplifier module, a clock recovery module, a tracking clock recovery module, and a jitter Recovery module, signal conditioning module, A / D conversion module, FPGA jitter test module, PXI bus control module and host computer module;

[0053] The power supply module is used for signal input module, photoelectric conversion module, differential amplification module, clock recovery module, tracking clock recovery module, jitter recovery module, signal conditioning module, A / D conversion module, FPGA jitter test module, PXI bus Power supply for control module and upper computer module;

[0054] The signal input module is used to receive SDH optical signals of different rates to be detected;

[0055] The photoelectric conversion module is used ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More