Method for forming self-aligned split-gate flash memory

A separate gate and self-alignment technology, which is applied in semiconductor devices, electrical components, circuits, etc., can solve the problems of unfavorable low and medium density, increase decoding devices, weaken the effect of cost reduction, etc., to ensure reading speed and programming efficiency Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] In order to make the above objects, features and advantages of the present invention more comprehensible, specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

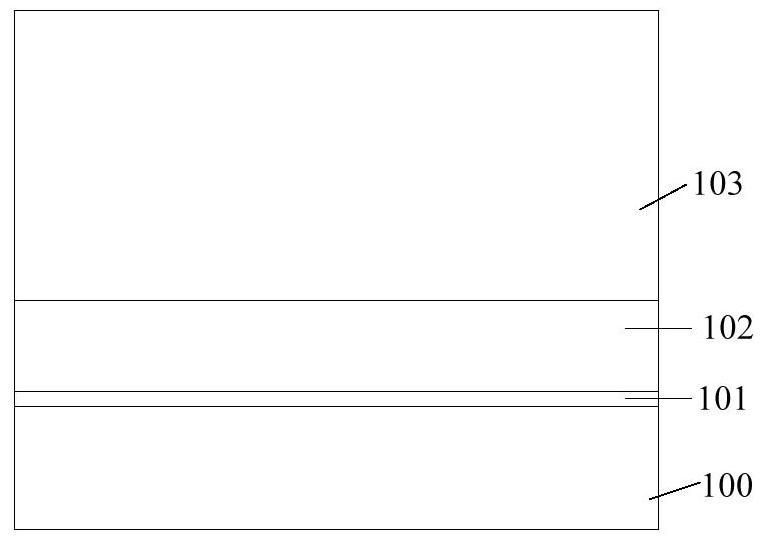

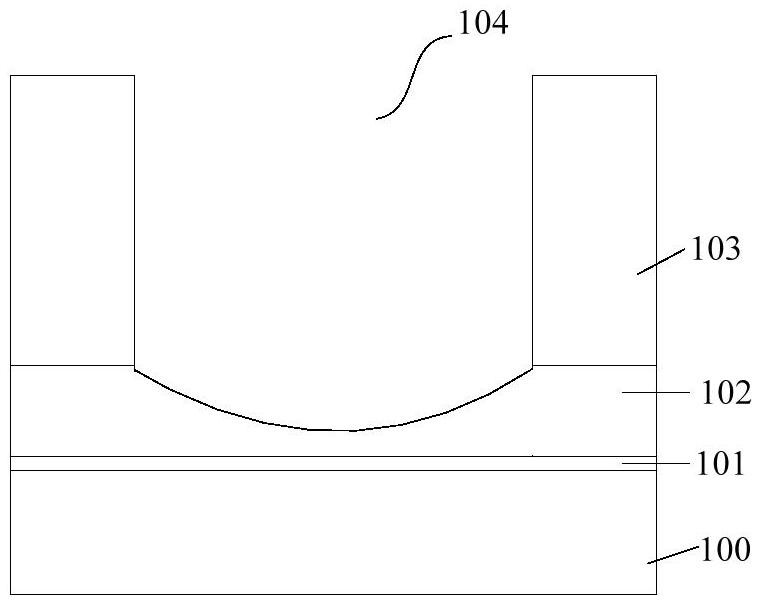

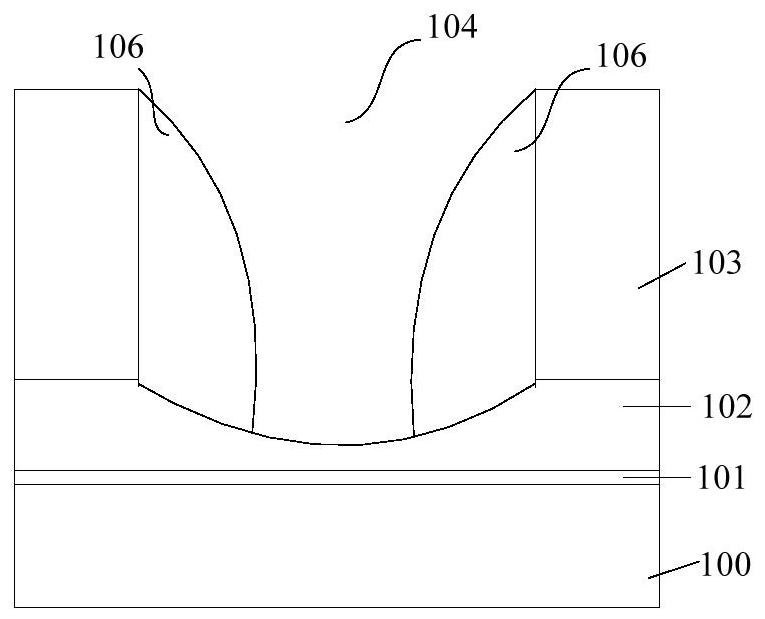

[0019] Figure 1 to Figure 6 A schematic cross-sectional view of a flash memory cell with a self-aligned split gate structure according to an embodiment is schematically given.

[0020] Please refer to figure 1 A substrate 100 is provided, and a thermal oxide layer 101 , a floating gate layer 102 and a hard mask layer 103 are sequentially grown on the surface of the substrate 100 .

[0021] The material of the substrate 100 is semiconductor silicon, which can be n-type or p-type semiconductor, or silicon-on-insulator etc. bottom), graded substrates, silicon-on-insulator substrates, epitaxial silicon substrates, partially processed substrates (including parts of integrated circuits and other components), patterned or unpatterned substrate...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com