Method and apparatus for reducing power bouncing of integrated circuits

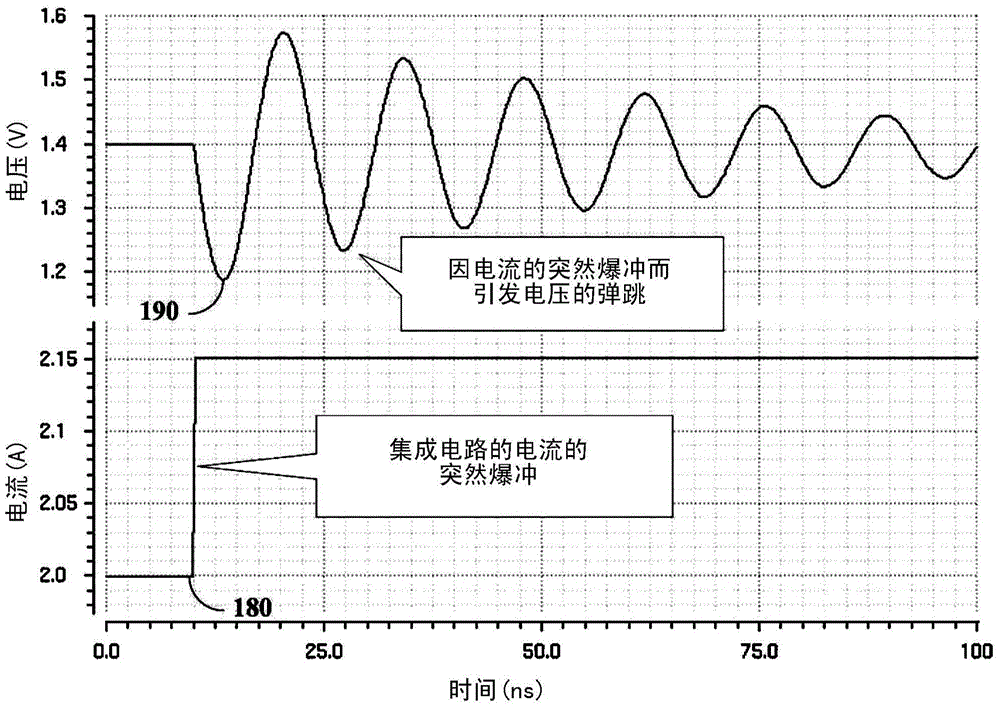

一种集成电路、封装式的技术,应用在封装式集成电路元件及其减少电源弹跳领域,能够解决电源弹跳不理想、封装电路昂贵、降低集成电路110可靠性等问题,达到减少电源弹跳的效果

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0089] The following detailed description refers to the accompanying drawings, and through the description of the drawings, various practicable embodiments of the present invention are disclosed. The described embodiments are specific and sufficiently disclosed to enable those skilled in the art to perform them. Different embodiments are not mutually exclusive, some embodiments can be combined with one or more embodiments to form new embodiments. Therefore, the following detailed description is not intended to limit the invention.

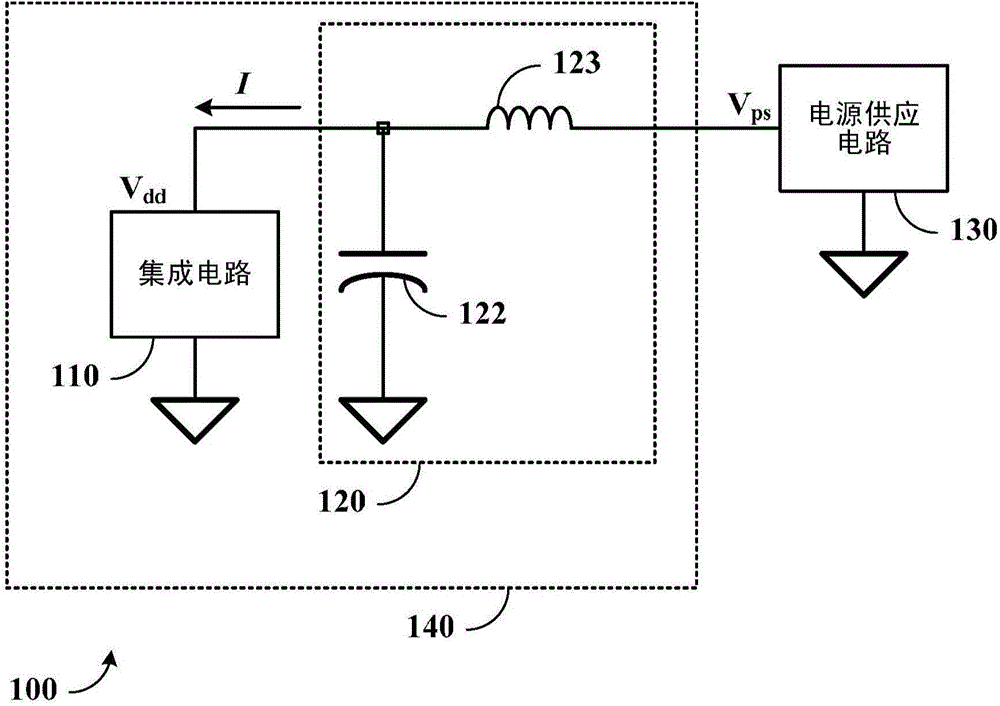

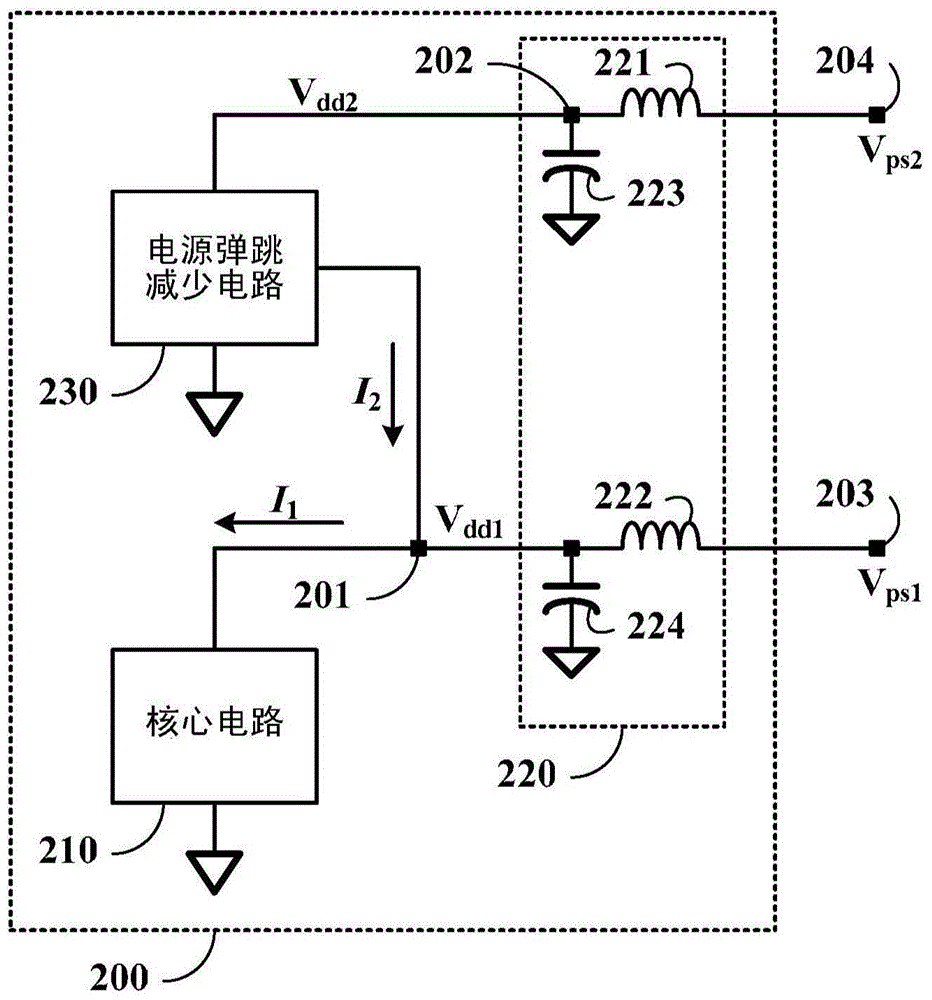

[0090] refer to figure 2 A packaged integrated circuit (IC) device 200 includes a core circuit 210 , a packaged circuit 220 and a power bounce reduction circuit 230 . The core circuit 210 is coupled to the first external power supply node 203 through the packaging circuit 220 . Here, the encapsulation circuit 220 is coupled between the first external power supply node 203 and the first internal power supply node 201 , and the core circuit 210 a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More