Semiconductor package with cooling fin, and packaging method for semiconductor package

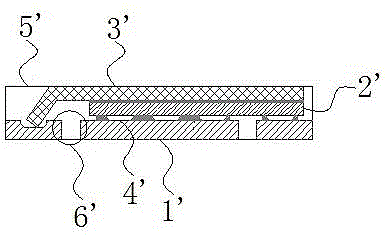

A technology for semiconductors and heat sinks, applied in semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., can solve the problem of reducing the effective connection area of the chip 2' source, reducing the effective utilization of product space, and operating procedures Complicated problems, to achieve the effect of increasing the effective welding surface, low cost, and reducing the operation process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] The present invention will be further elaborated below by describing a preferred specific embodiment in detail in conjunction with the accompanying drawings.

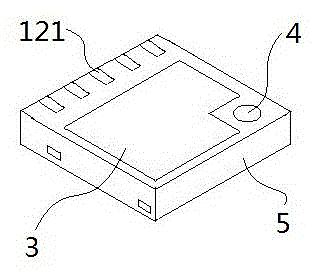

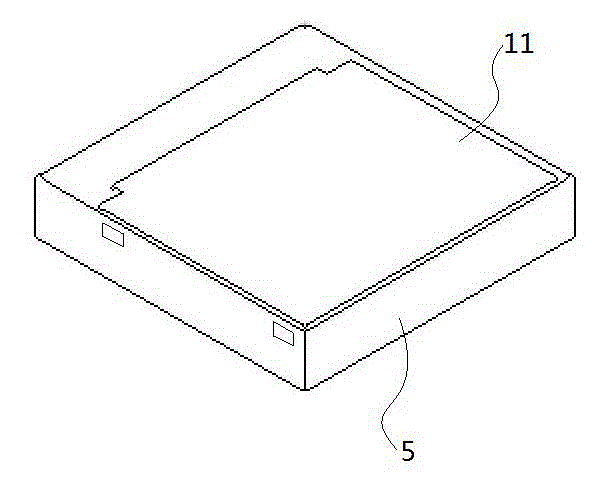

[0028] Such as Figure 2~Figure 5 shown, combined with Image 6 , a semiconductor package with a heat sink, comprising: a lead frame 1, the lead frame 1 includes a chip stage 11 and a plurality of pins 12 electrically connected to the chip stage 11 and bent, each pin 12 Including a pin surface 121 parallel to the loading table 11 and extending continuously without interruption between the loading table 11 and the pin surface 121;

[0029] A chip 2 is installed on the carrier stage 11, wherein the entire area of the chip drain metal layer 201a that completely covers the first surface 201 of the chip is connected to the carrier stage 11, and the source metal layer 202a and the gate metal layer of the chip 2 202b is disposed on the second surface 202 of the chip opposite to the drain metal layer of the chip 2, a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More