3D nonvolatile memory, and manufacturing method and power consumption reduction method thereof

A non-volatile, manufacturing method technology, applied in static memory, read-only memory, semiconductor/solid-state device manufacturing, etc., can solve the problems of increased chip area, high production cost of 3D memory, and complexity of 3D memory chips. Low leakage power consumption, flexible implementation method, and the effect of reducing parasitic capacitance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

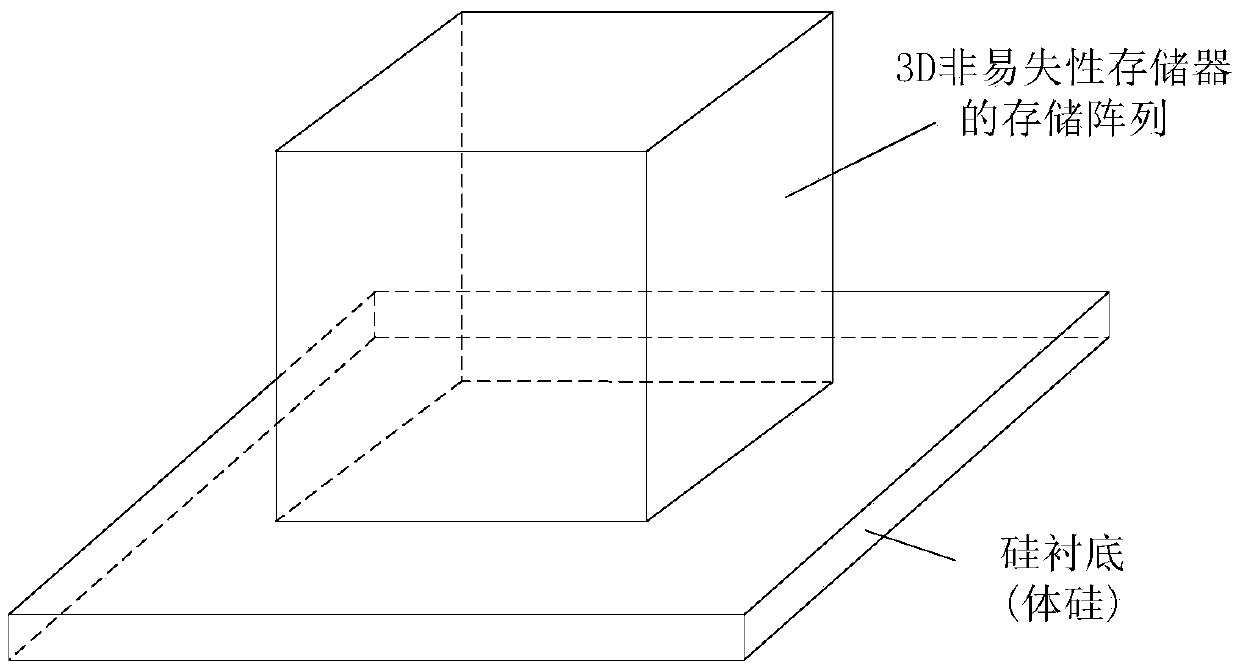

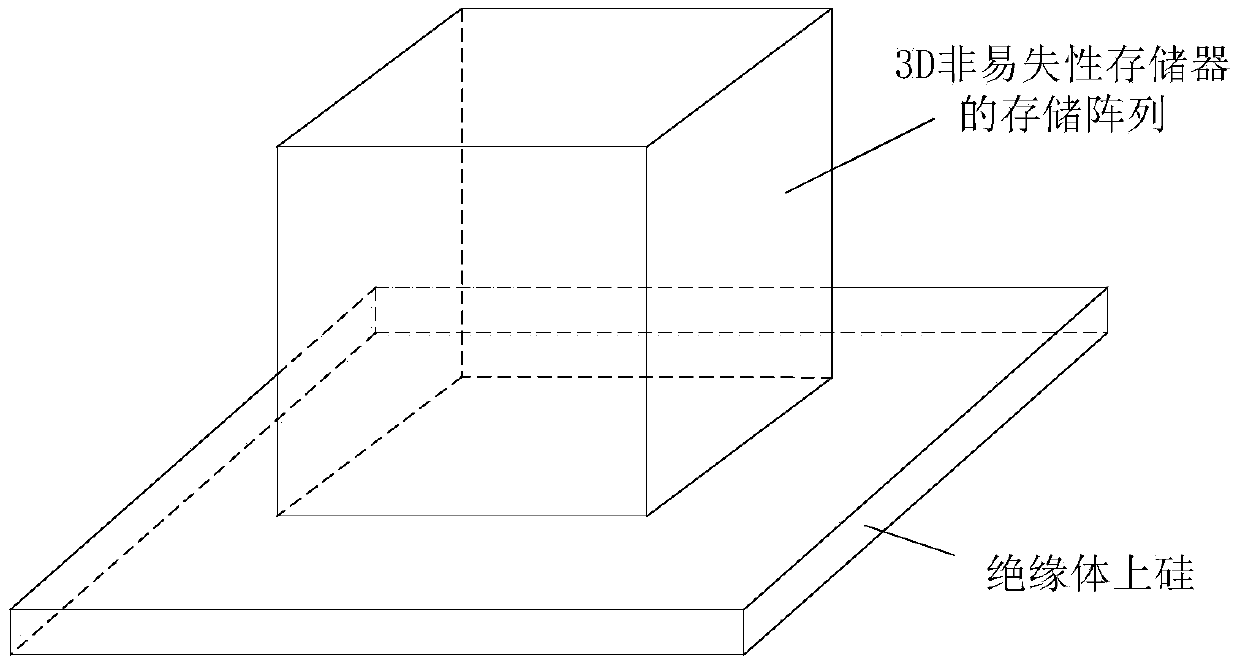

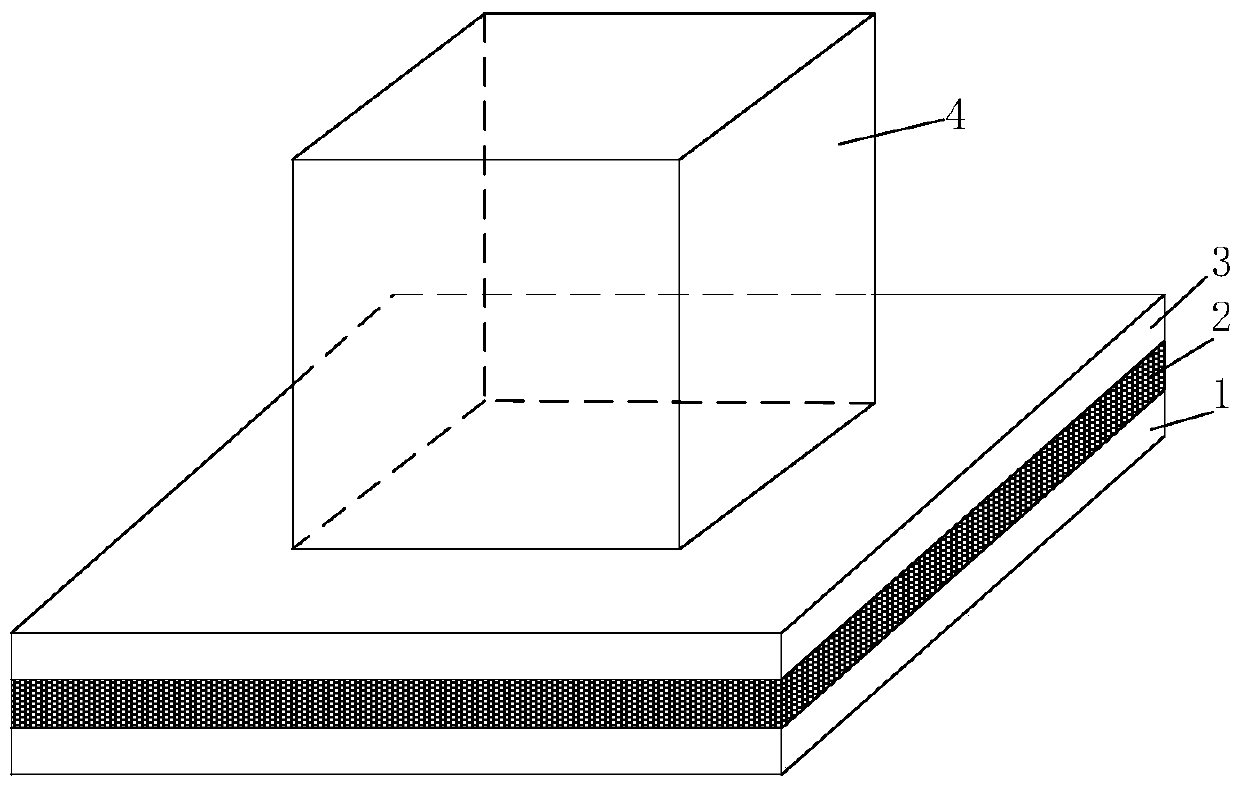

[0021] A specific embodiment of the 3D non-volatile memory based on the FDSOI process of the present invention is as follows image 3 shown. Among them, 1 is the silicon substrate (substrate); 2 is the buried oxide layer (BuriedOxideLayer, BOX), which acts as an insulating layer between 1 and 3; 3 is the top layer of monocrystalline silicon, which is used to realize the periphery of the 3D non-volatile memory CMOS logic circuit; 4 is a storage array of 3D non-volatile memory.

[0022] Furthermore, in the present invention, the performance and power consumption of different functional modules can be optimized by adjusting the back gate voltage. By adjusting the back gate voltage, the turn-on voltage of the transistor can be lowered, so that the transistor can work normally at a lower voltage, and can even work normally near the threshold voltage (near-Vt), so the power consumption of the chip will be greatly reduced . Such as Figure 4 What is shown is the peripheral CMOS l...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More