A kind of output circuit of SRAM

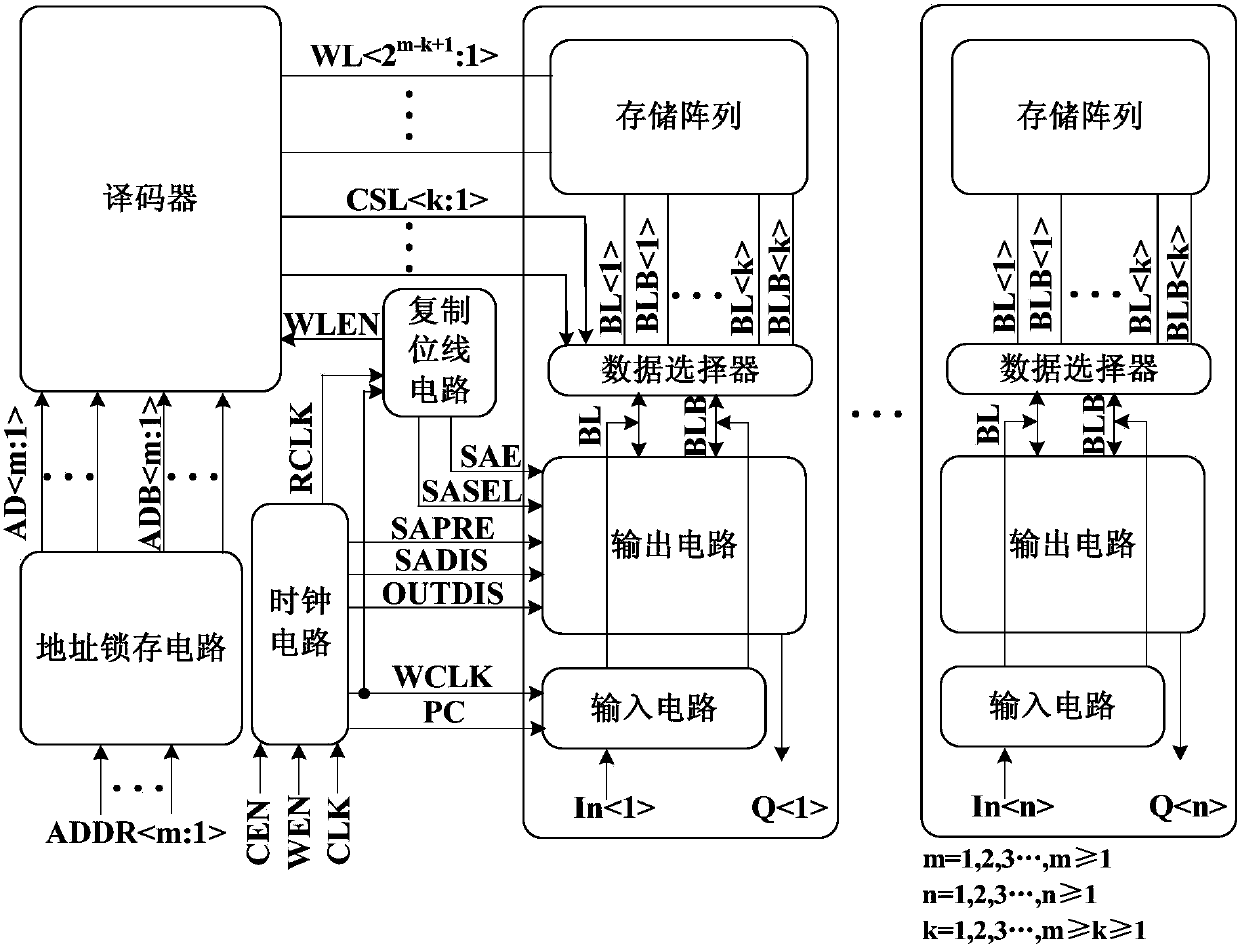

A static random, output circuit technology, applied in the field of output circuits, can solve the problems of reading data power consumption difference, static random access memory differential power consumption analysis attack threat, not suitable for design defense power consumption attack static random access memory and other problems, to eliminate Effects of Inconsistent Wiring Capacitance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

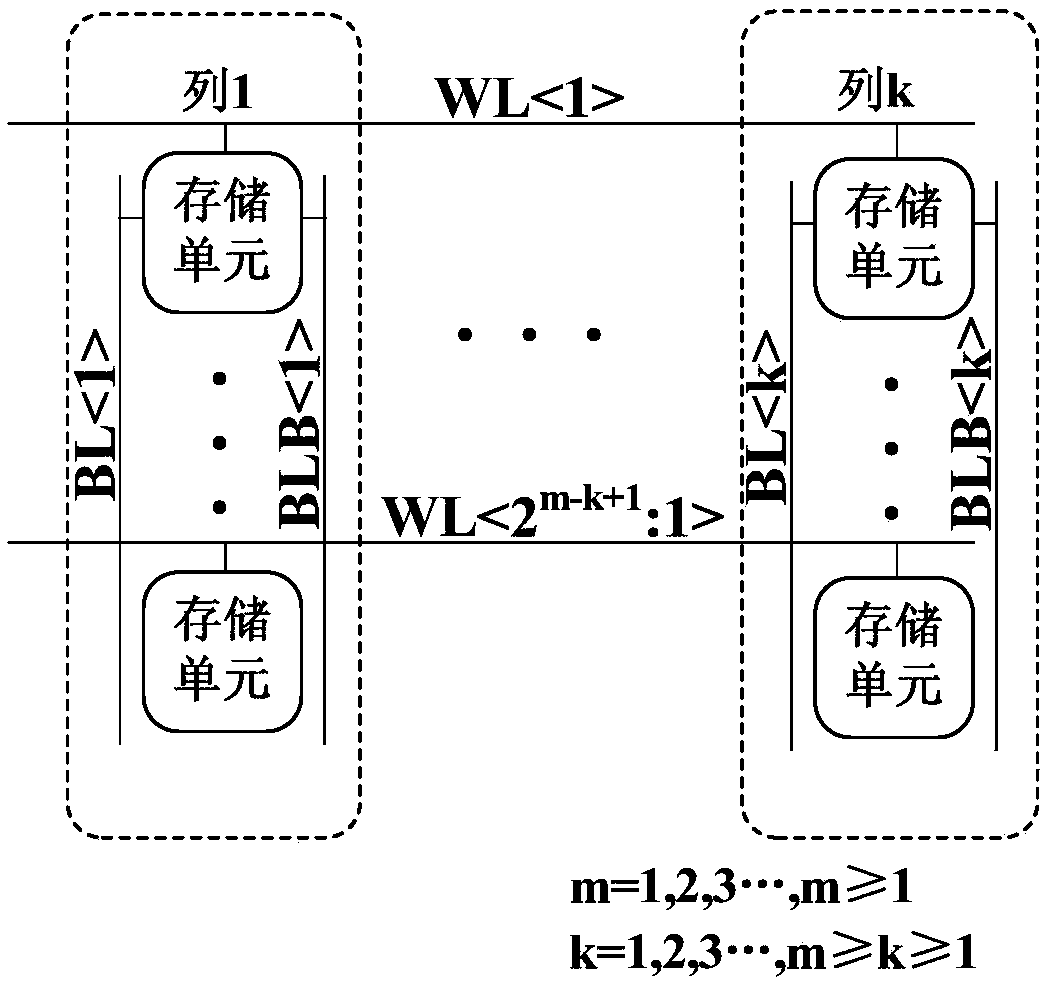

Method used

Image

Examples

Embodiment

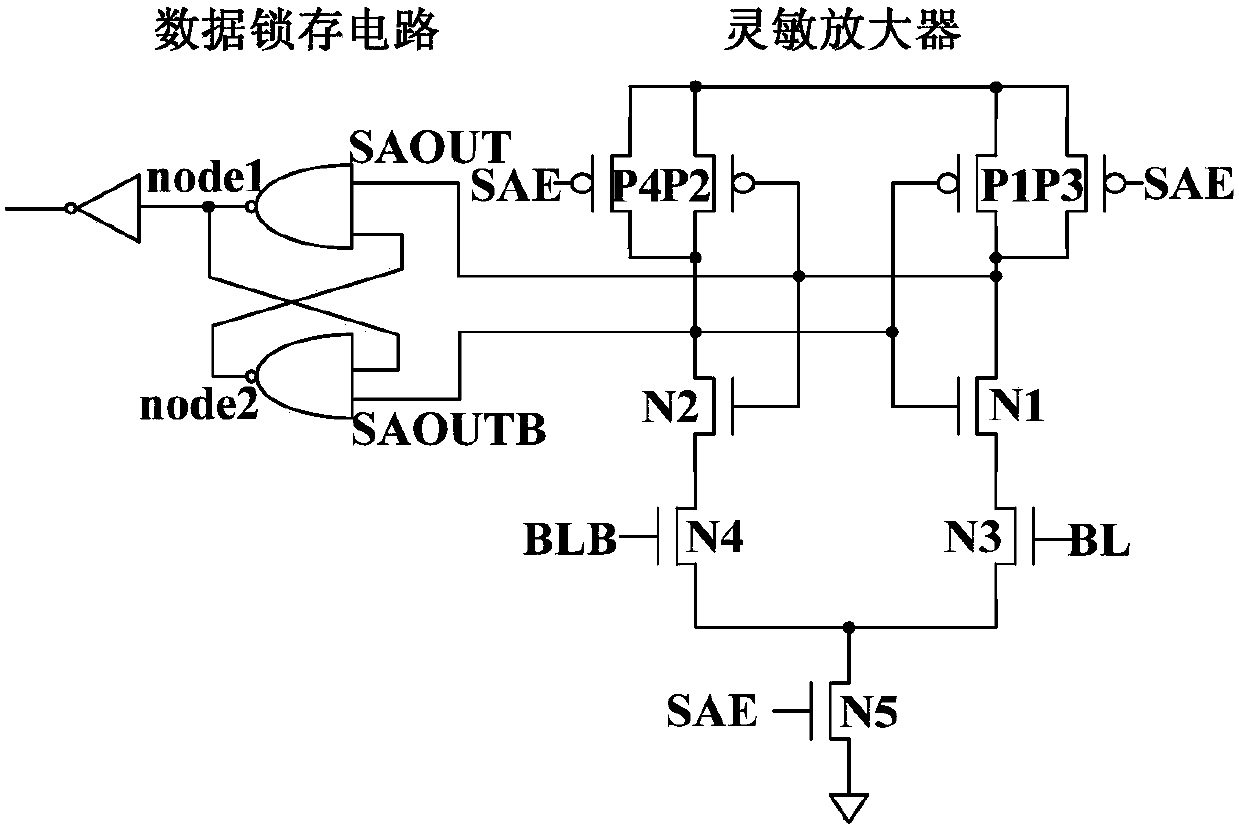

[0024] Example: such as Figure 6 As shown, an output circuit of an SRAM includes a sense amplifier and a data latch circuit, and the sense amplifier includes a first PMOS transistor P1, a second PMOS transistor P2, a third PMOS transistor P3, a fourth PMOS transistor P4, and a fifth PMOS transistor P4. PMOS transistor P5, sixth PMOS transistor P6, seventh PMOS transistor P7, first NMOS transistor N1, second NMOS transistor N2, third NMOS transistor N3, fourth NMOS transistor N4 and fifth NMOS transistor N5; the first PMOS transistor The source of P1, the source of the fourth PMOS transistor P4 and the source of the fifth PMOS transistor P5 are connected to the power supply, the drain of the first PMOS transistor P1, the source of the second PMOS transistor P2 and the third PMOS transistor P3 The source of the second PMOS transistor P2, the gate of the third PMOS transistor P3, the drain of the fourth PMOS transistor P4, the drain of the sixth PMOS transistor P6, the drain of ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More