Bus structure of SoC system

A bus structure and system bus technology, applied in the computer field, can solve problems such as low efficiency, mismatched bandwidth, and performance degradation of SoC systems, and achieve the effects of clear hierarchy, strong applicability, and high efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] In order to make the object, technical solution and advantages of the present invention clearer, various embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings. However, those of ordinary skill in the art can understand that, in each implementation manner of the present invention, many technical details are provided for readers to better understand the present application. However, even without these technical details and various changes and modifications based on the following implementation modes, the technical solution claimed in each claim of the present application can be realized.

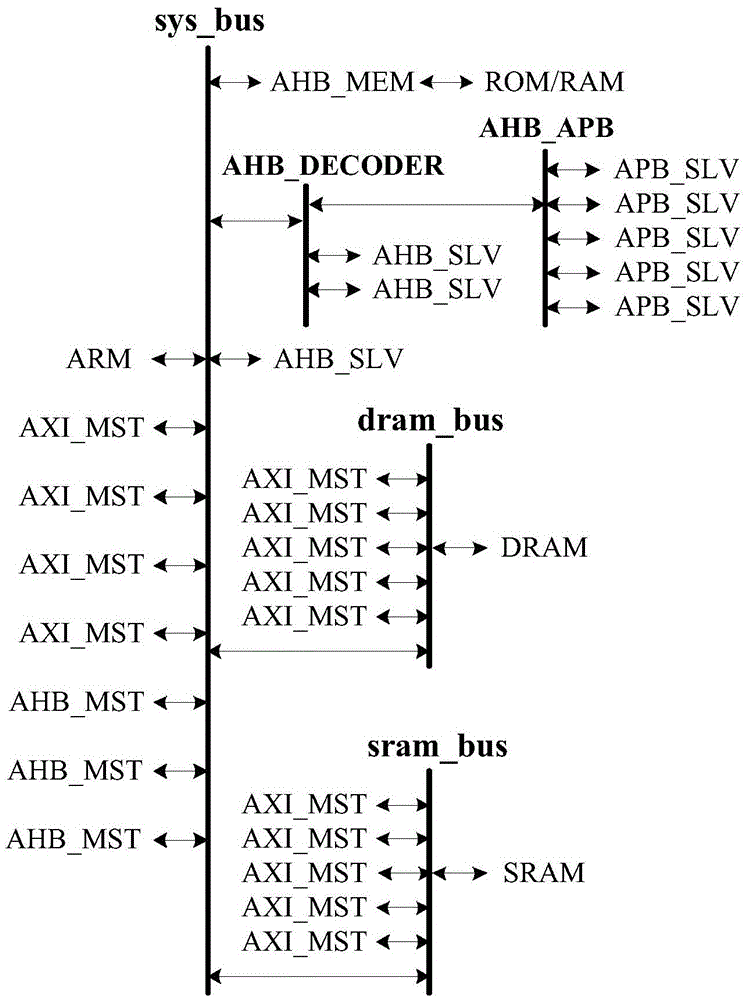

[0028] The first embodiment of the present invention relates to a bus structure of an SoC system, the specific schematic diagram is as follows figure 1 shown. Including: system bus (hereinafter referred to as sys-bus), dynamic memory access bus (hereinafter referred to as dram-bus), static memory access bus (hereinafter ref...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More