Wiring board

A technology of wiring substrates and insulating substrates, which is applied to the layout details of conductive patterns, printed circuits, electrical components, etc., can solve the problems of impedance mismatch, signal reflection, and inability to transmit high-frequency signals efficiently, and achieves a lower impedance. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

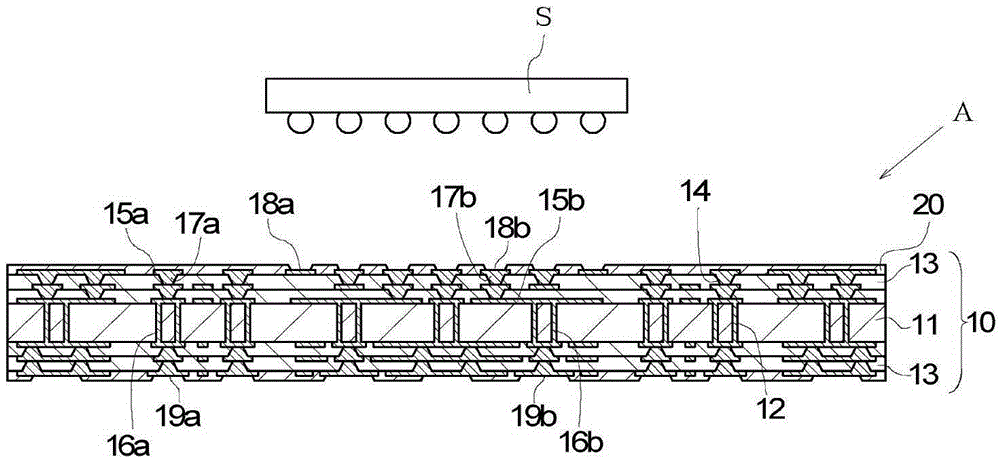

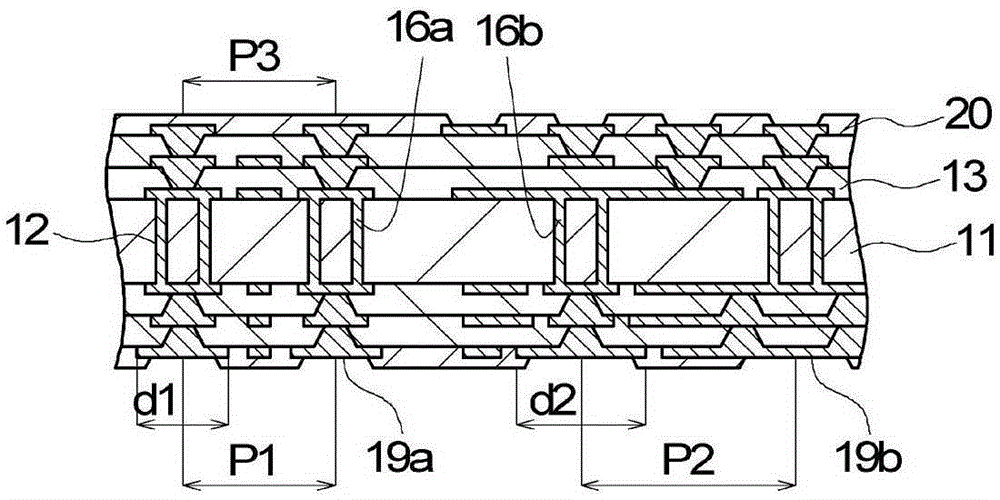

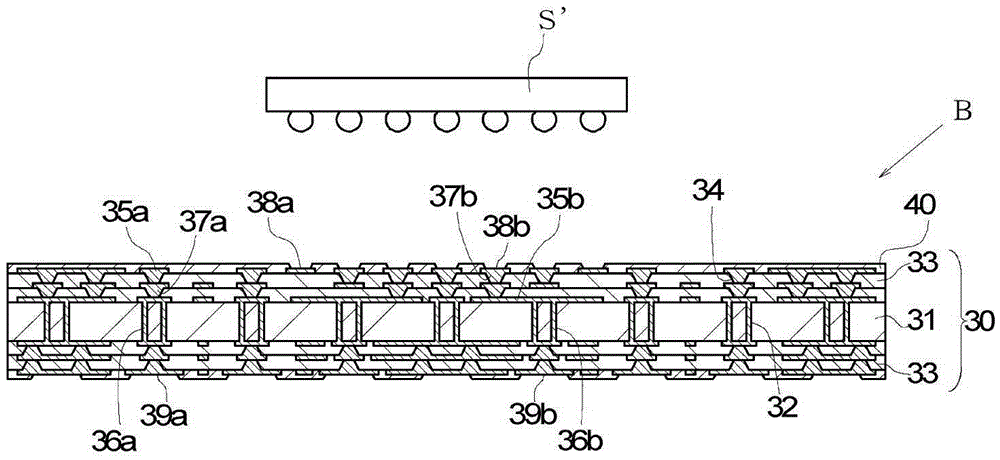

[0020] based on figure 1 as well as figure 2 A wiring board according to an embodiment will be described. figure 1 The illustrated wiring board A includes an insulating substrate 10 in which a plurality of insulating layers 13 having via holes 14 are stacked on upper and lower surfaces of an insulating plate 11 having through holes 12 .

[0021] The insulating sheet 11 is a member that becomes a core substrate of the wiring substrate A. As shown in FIG. The insulating plate 11 is formed, for example, of an electrical insulating material obtained by impregnating a thermosetting resin such as epoxy resin or bismaleimide triazine resin into a glass fabric in which glass fiber bundles are woven vertically and horizontally. owned. The thickness of the insulating plate 11 is about 0.3 to 1.5 mm. The diameter of the through hole 12 is about 0.1 to 0.3 mm.

[0022] Each insulating layer 13 laminated on the upper and lower surfaces of the insulating plate 11 is a reinforcing in...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More