Debugging method and system for programmable logic device

A programming logic and debugging system technology, applied in the debugging method and system field of programmable logic devices, can solve the problems that cannot meet the debugging requirements of FPGA technology, and achieve the effect of rich trigger condition configuration and simple use

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

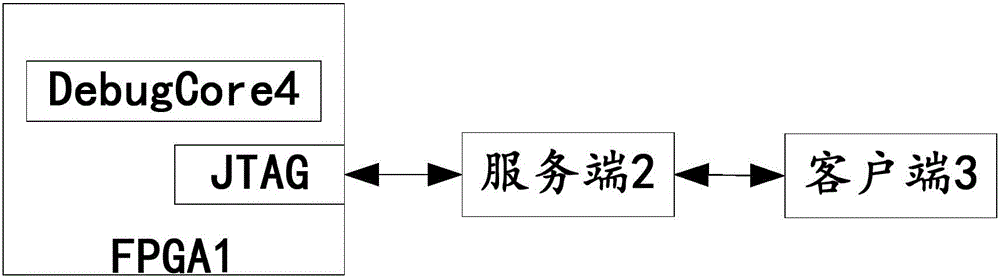

[0034] figure 1 It is a schematic structural diagram of the debugging system provided by the first embodiment of the present invention, which is represented by figure 1 It can be seen that in this embodiment, the debugging system provided by the present invention includes: a programmable logic device 1, a server 2, a client 3 and an enhanced logic analyzer core DebugCore4 embedded in a programmable logic device 1, wherein:

[0035] The client 3 is used to set the operating parameters of the enhanced logic analyzer core, and sends the bit stream file generated by compiling and compiling the operating parameters and the design to be tested to the server 2;

[0036] The server 2 is used to download the bit stream file to the programmable logic device 1;

[0037] The programmable logic device 1 is used to execute the design under test, and the enhanced logic analyzer core 4 collects and stores data according to the working parameters, and sends them to the server 2;

[0038] The...

no. 2 example

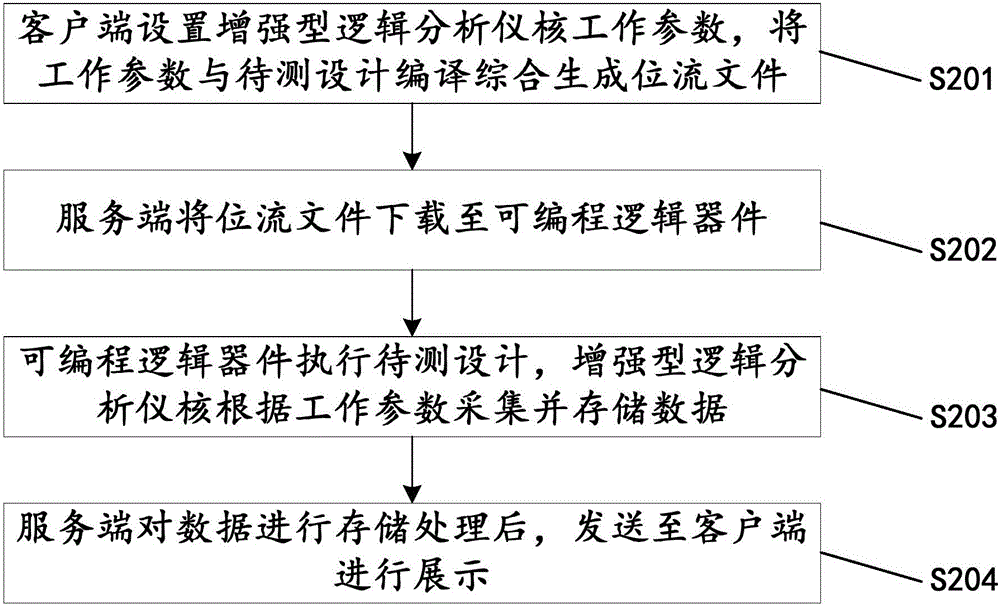

[0045] figure 2 The flow chart of the debugging method provided by the second embodiment of the present invention is composed of figure 2 It can be seen that in this embodiment, the debugging method provided by the present invention includes:

[0046] S201: The client sets the working parameters of the enhanced logic analyzer core, compiles and synthesizes the working parameters and the design under test to generate a bit stream file and sends it to the server;

[0047] S202: The server downloads the bit stream file to the programmable logic device;

[0048] S203: The programmable logic device executes the design under test, and the enhanced logic analyzer core collects and stores data according to the working parameters, and sends them to the server;

[0049] S204: After the server stores and processes the data, it sends it to the client for display.

[0050] In some embodiments, before the server downloads the bit stream file to the programmable logic device, the method...

no. 3 example

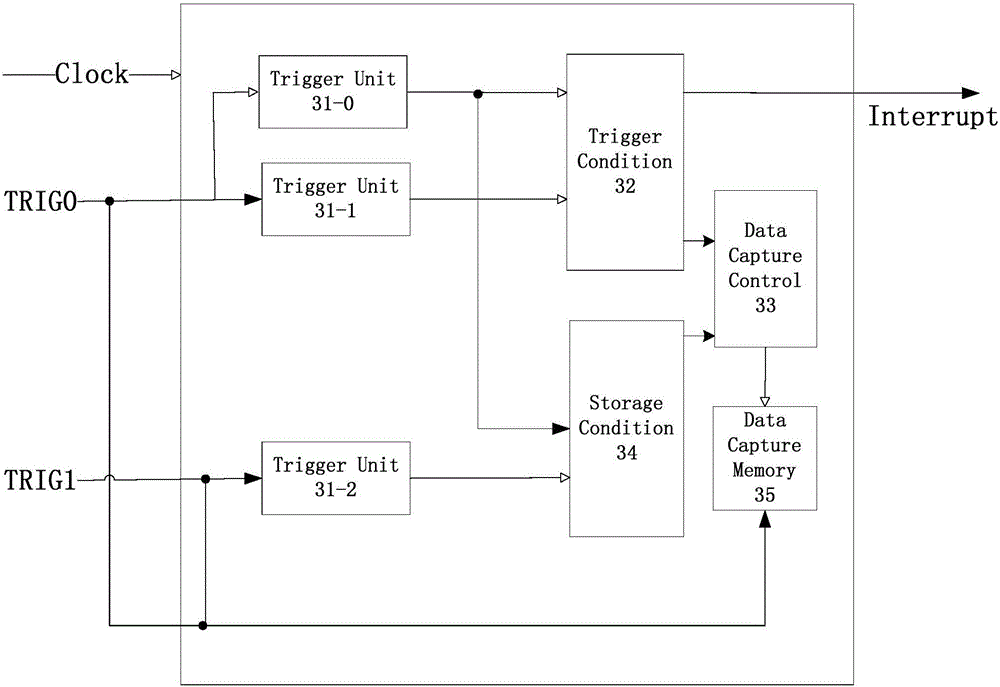

[0057] This embodiment provides an enhanced embedded logic analyzer based on PLD (programmablelogicdevice, programmable logic device), by inserting one or more logic analyzer cores in the FPGA design, the user can easily access the inside of the FPGA device All signals and nodes (including ports, wire nets and pins); by setting trigger conditions, the signals to be observed are triggered, data collected, stored, and displayed and observed on the client; used to solve the problem of ultra-high Density FPGA debugging is inconvenient. The embedded enhanced logic analyzer has the ability to support multiple DebugCores (enhanced logic analyzer cores) to sample data at the same time. When powering on and initializing, the configuration of grabbing signals and trigger conditions is more abundant and easy to use. Simple and other features, and has a powerful data analysis display function through the client.

[0058] In actual use, the embedded logic analyzer uses one or more DebugCor...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More