Chip scale sensing chip package and a manufacturing method thereof

A technology for sensing wafers and sizes, applied in printed circuit manufacturing, semiconductor/solid-state device manufacturing, character and pattern recognition, etc., can solve problems such as defective products, damage, poor production workability of packaging substrates, etc., to avoid mismatching , the effect of reducing production costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0086] The following will match Figure 1A ~ Figure 1E and Figure 1C'~Figure 1E' , illustrating the wafer-scale sensing chip package module and its manufacturing method according to Embodiment 1 of the present invention.

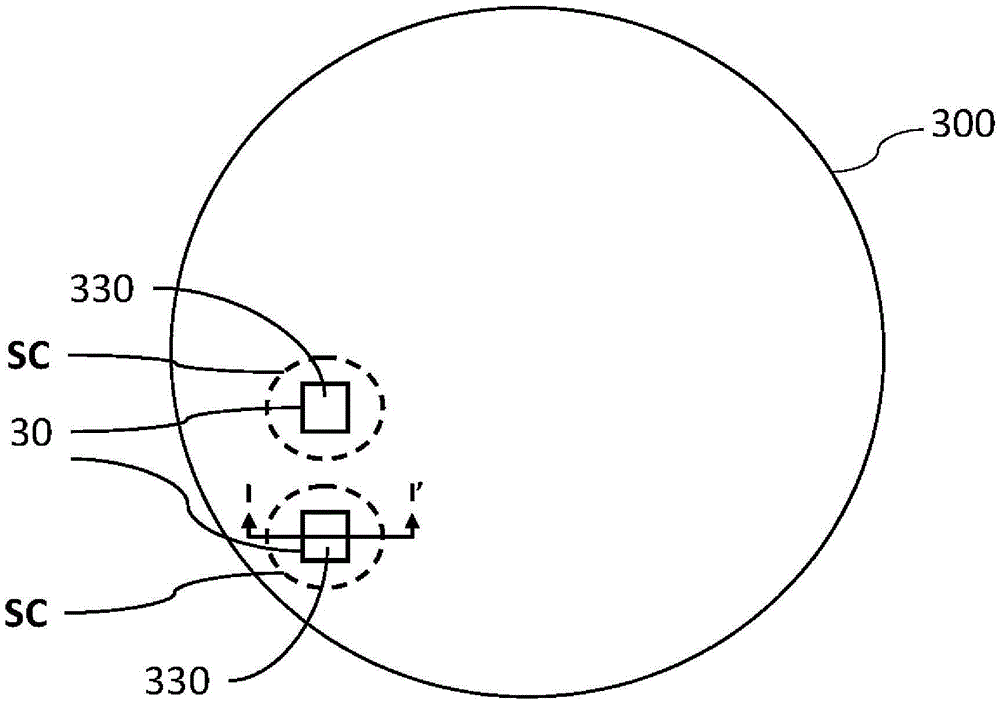

[0087] Please refer to Figure 1A Firstly, a touch panel wafer 300 is provided, the surface of which includes a plurality of die-bonding regions 30 , and a predetermined circular dicing line SC is formed on the periphery of each die-bonding region 30 . In this embodiment, the touch panel wafer 300 can be selected from a transparent material with a hardness greater than 7, such as glass.

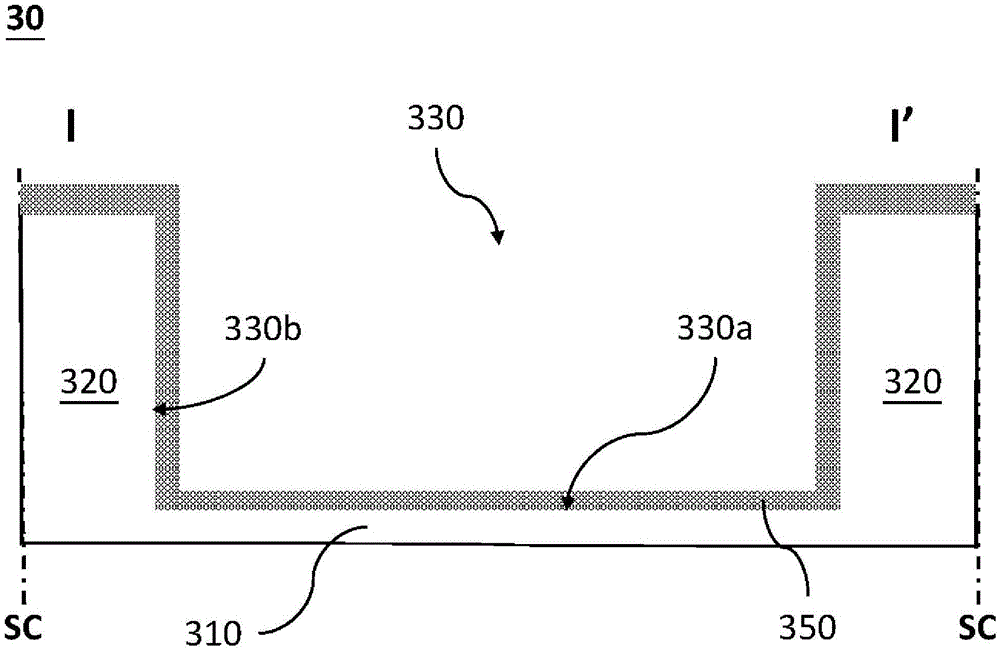

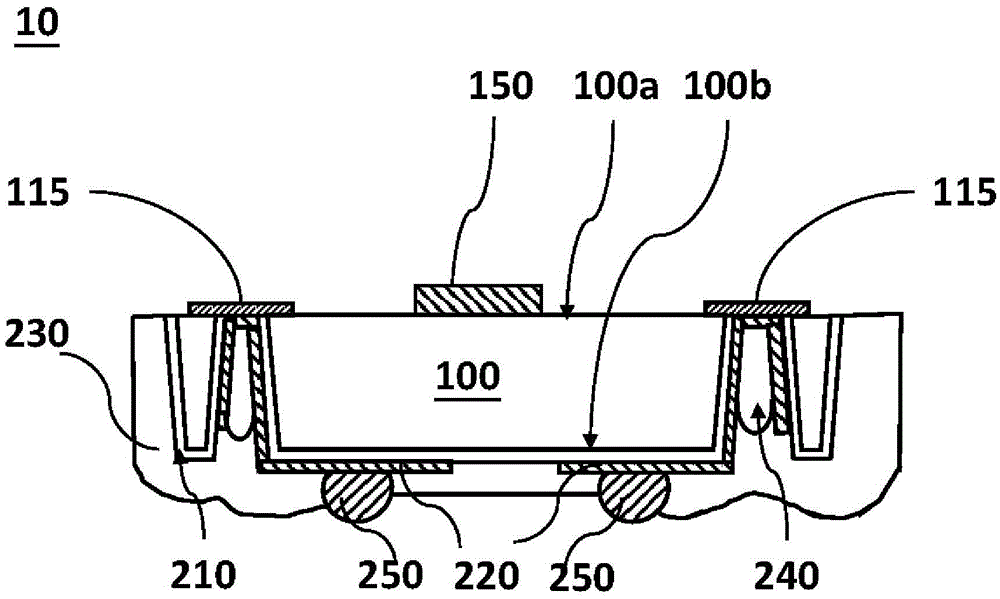

[0088] Next, please refer to Figure 1B , which is shown along the Figure 1A The cross-sectional view of the crystal-bonding region 30 presented by the cross-section line I-I'. Such as Figure 1B As shown, the crystal bonding area 30 includes a base 310 and a spacer 320 positioned on the base, the spacer 320 has a cavity 330 that exposes the surface of the base 310, ...

Embodiment 2

[0094] The following will match Figure 2A to Figure 2C and Figure 2B' to Figure 2C' , illustrating the sensing chip package module of the wafer size level and its manufacturing method according to the second embodiment of the present invention.

[0095] Please refer to Figure 2A , which shows a schematic cross-sectional view of a crystal-bonding region 50 . Such as Figure 2A As shown, the die bonding area 50 includes a base 510 and a spacer 545 on the base 510 and surrounding the base 510 , wherein the spacer 545 also includes a cavity 550 exposing the surface of the base 510 . In addition, the base 510 of this embodiment includes a touch panel 540 , a colored layer 520 and a second adhesive layer 530 sandwiched between the touch panel 540 and the colored layer 520 , and the spacer 545 is formed on the colored layer 520 .

[0096] Next, please refer to Figure 2B and Figure 2B' , through the first adhesive layer 400, so that as Figure 1C or Figure 1C' A sensor wa...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More