Trench Schottky chip applicable to metal wire bonding and processing technology thereof

A metal wire and bonding technology, applied to electrical components, electrical solid devices, circuits, etc., can solve problems such as chip failure and groove damage, and achieve the effects of improving chip performance, reducing consumption, and facilitating finding fault points

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

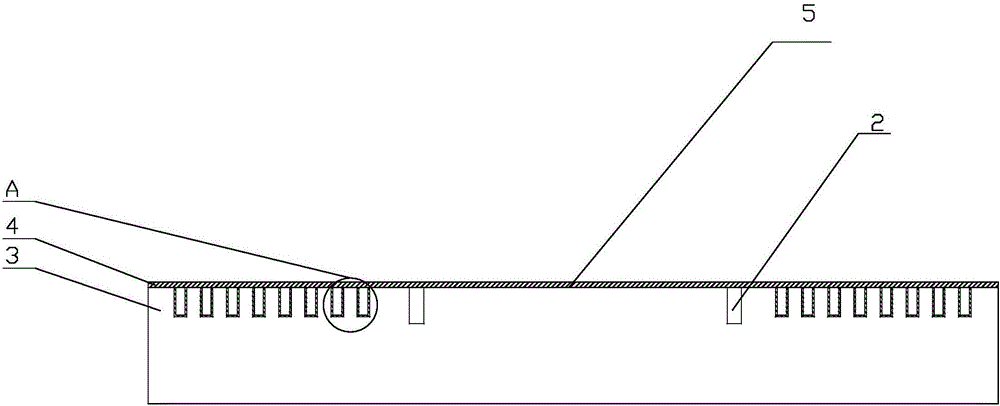

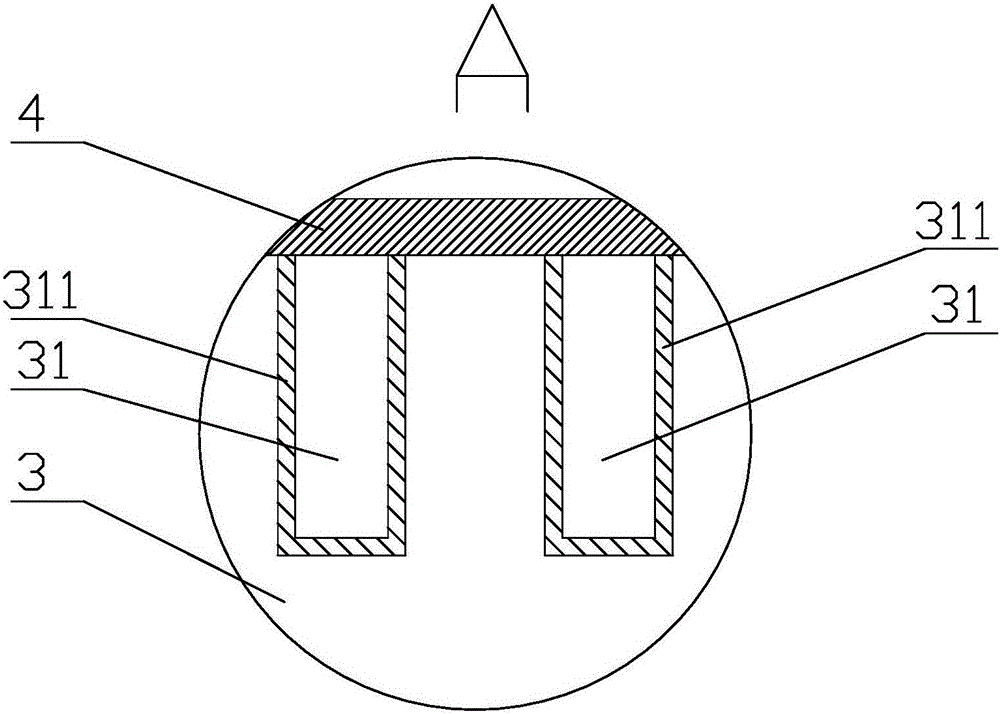

[0036] Such as image 3 As shown, an oxide layer is provided around the trench area to avoid chip damage during processing. The trench region 3 is evenly distributed with grooves 31, and the grooves 31 are filled with polysilicon material, which is used to increase the contact area of the chip and reduce the forward conduction voltage, and obtain a lower reverse voltage by selecting a barrier metal with a higher energy level. to the leakage current. Surface metal is laid on the surface of the trench area. Use the good electrical conductivity of the surface metal to conduct with the plane bonding area. The trench area 3 is also provided with a plane bonding area 5 , the plane bonding area 5 is a smooth plane, and the surface metal 4 is laid on the plane bonding area 5 . The surface metal 4 has good electrical conductivity, which reduces the internal resistance of the chip, thereby reducing power consumption of the chip. The planar bonding area 5 is used for soldering with...

Embodiment 2

[0038] Such as Figure 4As shown, an oxide layer is provided around the trench area to avoid chip damage during processing. The trench region 3 is evenly distributed with grooves 31, and the grooves 31 are filled with polysilicon material, which is used to increase the contact area of the chip and reduce the forward conduction voltage, and obtain a lower reverse voltage by selecting a barrier metal with a higher energy level. to the leakage current. Surface metal is laid on the surface of the trench area. Use the good electrical conductivity of the surface metal to conduct with the plane bonding area. The trench area 3 is also provided with a plane bonding area 5 , the plane bonding area 5 is a smooth plane, and the surface metal 4 is laid on the plane bonding area 5 . The surface metal 4 has good electrical conductivity, which reduces the internal resistance of the chip, thereby reducing power consumption of the chip. The planar bonding area 5 is used for soldering with...

Embodiment 3

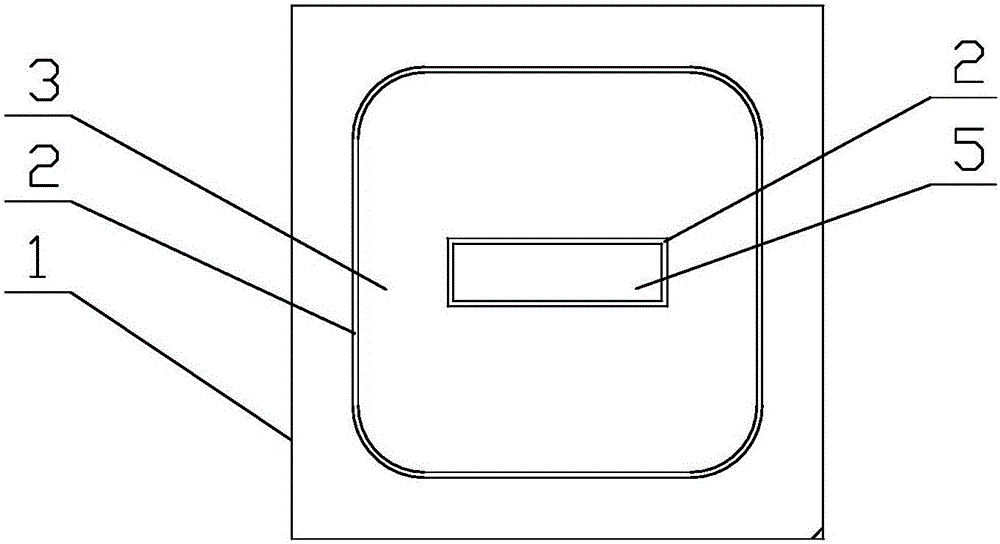

[0040] Such as Figure 5 As shown, an oxide layer is provided around the trench area to avoid chip damage during processing. The trench region 3 is evenly distributed with grooves 31, and the grooves 31 are filled with polysilicon material, which is used to increase the contact area of the chip and reduce the forward conduction voltage, and obtain a lower reverse voltage by selecting a barrier metal with a higher energy level. to the leakage current. Surface metal is laid on the surface of the trench area. Use the good electrical conductivity of the surface metal to conduct with the plane bonding area. The trench area 3 is also provided with a plane bonding area 5 , the plane bonding area 5 is a smooth plane, and the surface metal 4 is laid on the plane bonding area 5 . The surface metal 4 has good electrical conductivity, which reduces the internal resistance of the chip, thereby reducing power consumption of the chip. The planar bonding area 5 is used for soldering wit...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More