Forming method of semiconductor structure

A semiconductor and gate structure technology, applied in the field of semiconductor structure formation, can solve problems affecting transistor performance and poor interface layer quality, and achieve the effect of improving reactivity and quality

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

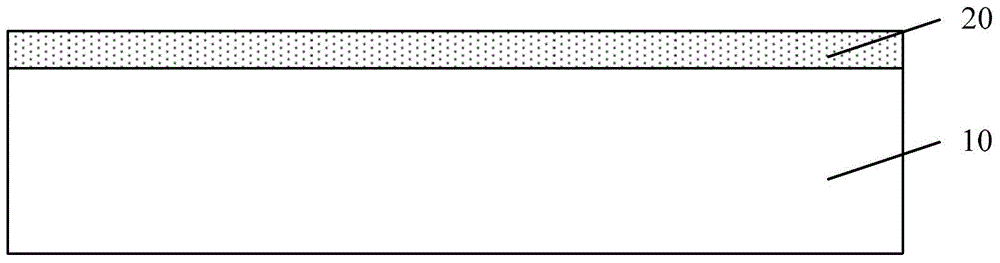

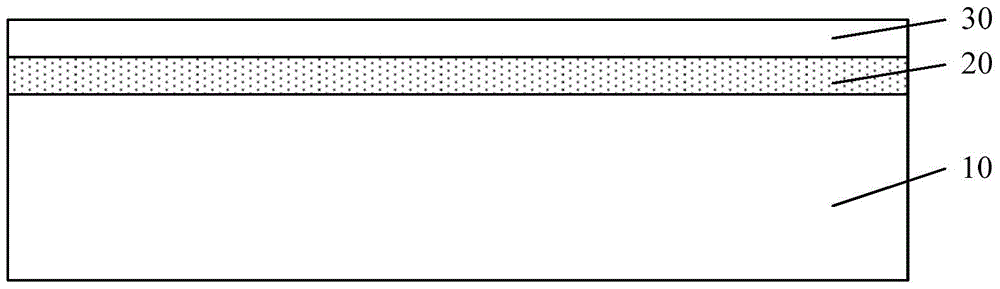

[0032] As mentioned in the background art, the quality of the interface layer formed in the prior art needs to be further improved.

[0033] Studies have found that in order to form a denser interface layer, an oxidation process is usually used to oxidize the surface of the semiconductor substrate to form an oxide layer as an interface layer. Since the thickness of the interface layer is generally thin, in order to effectively control the growth rate of the interface layer, the temperature of the oxidation process is usually lower to avoid the formation of an excessively thick oxide layer. However, the oxidation process at a lower temperature tends to cause the material of the formed interface layer to be relatively loose and have more unsaturated bonds, which affects the quality of the interface layer and ultimately affects the performance of the formed transistor.

[0034] The study found that after the formation of the interface layer, the high temperature N 2 The annealin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com