DPWM module for synchronous segmentation delay chain based on FPGA

A delay chain and clock control module technology, applied in the direction of transforming continuous pulse chains into pulse chain devices with required modes, automatic power control, pulse duration/width modulation, etc., can solve poor stability and high resolution Ratio, can not be realized and other problems, to achieve the effect of improving stability, improving linearity and stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

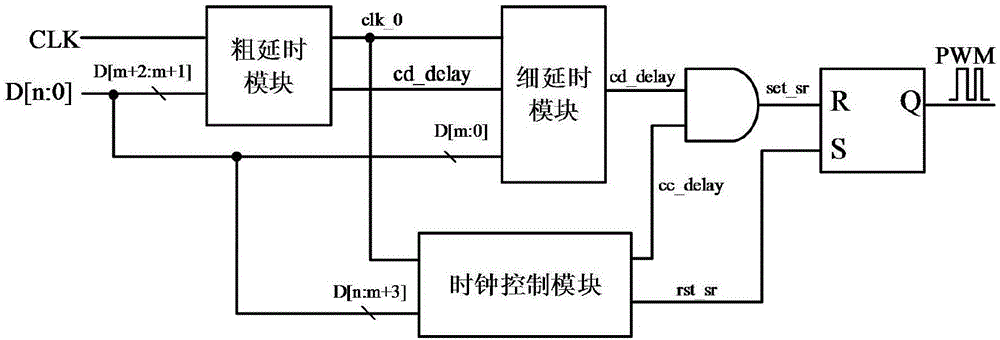

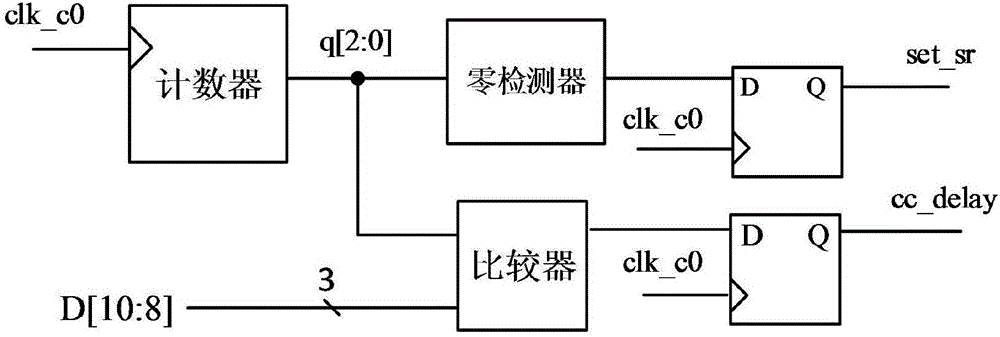

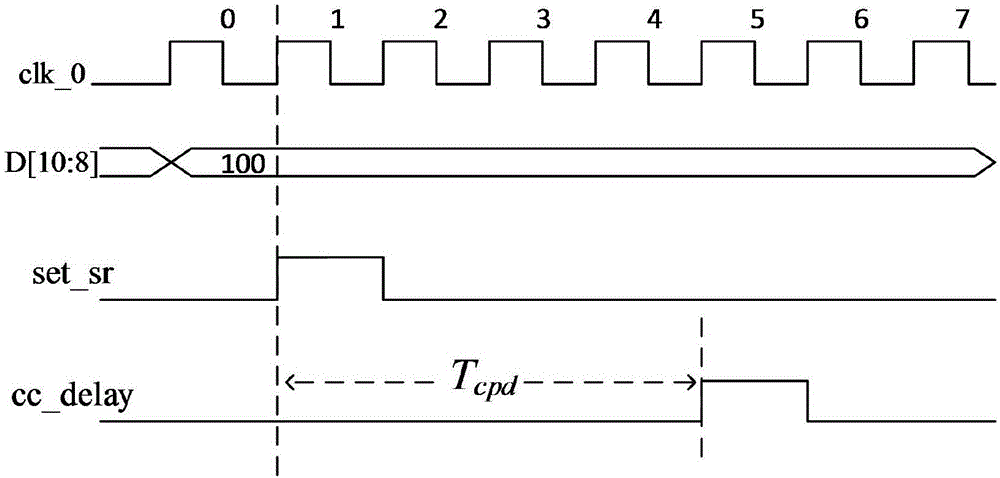

[0034] In this embodiment, a kind of DPWM module of FPGA-based synchronous segmentation delay chain, such as figure 1As shown, including: clock control module based on counter, coarse delay module based on phase-locked loop, fine delay module based on adder chain, AND gate and RS latch;

[0035] The coarse delay module based on the phase-locked loop receives the external clock signal CLK and performs frequency multiplication and phase-shift processing to obtain the phase-shifted clock signals clk_0, clk_90, clk_180, and clk_270; the phase-shifted clock signal clk_0 is used as the synchronous clock of the DPWM module And passed to the clock control module based on the counter and the fine delay module based on the adder chain respectively;

[0036] The coarse delay module based on the phase-locked loop shifts the clock signals clk_0, clk_90, clk_180, clk_0, clk_90, clk_180, clk_270 performs coarse delay selection, obtains the coarse delay signal cd_delay and sends it to the fi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More