Three-dimensional network-on-chip dynamic frequency regulation method based on prediction

An on-chip network and dynamic frequency technology, which is applied to architectures with a single central processing unit, instruments, and general-purpose stored-program computers, can solve problems such as greatly affecting system performance, improve flexibility, improve timeliness, and reduce system costs. The effect of energy reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

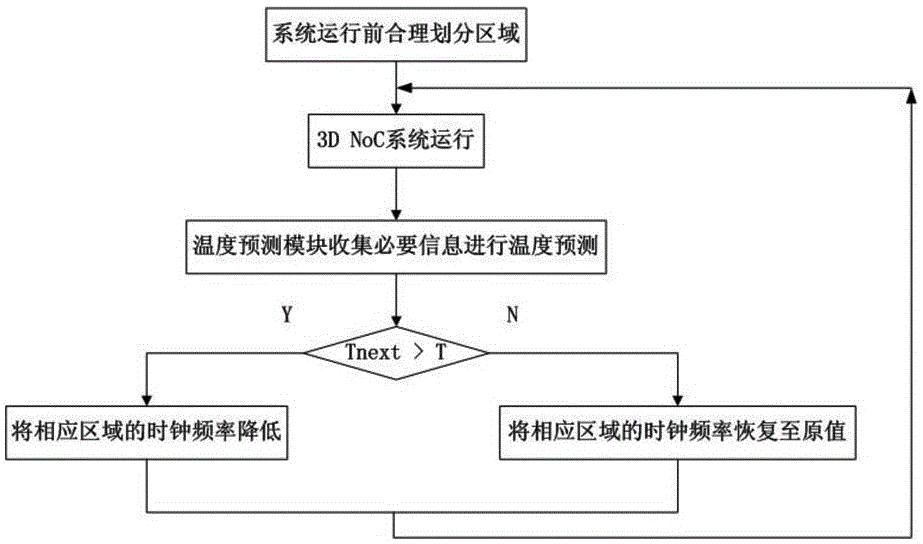

[0036] As shown in Fig. 1, the method for adjusting the dynamic frequency of the three-dimensional network-on-chip based on the prediction of the present invention, the steps are:

[0037] S1: System partitioning of the 3D network on chip;

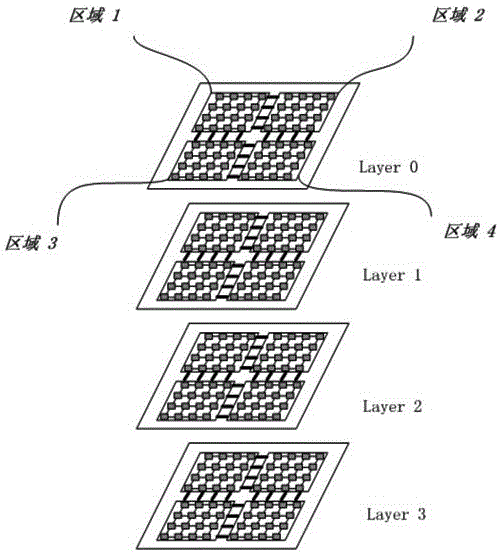

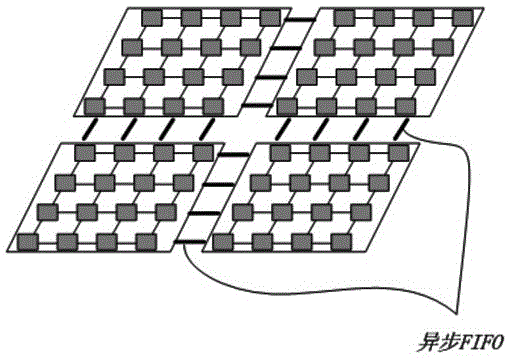

[0038] Divide the whole system into several areas, and each area is called a frequency adjustment area. Each node in the area uses the same clock signal, while nodes belonging to different areas use different clock signals. Clock signals in different areas can be adjusted according to corresponding requirements. Use the same or different clock frequencies. The partitioned system can perform distributed frequency adjustment or global frequency adjustment according to the actual situation, thereby reducing the performance overhead caused by dynamic frequency adjustment.

[0039] The principle of t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More