A wide-bit accumulator circuit and its design method, programmable logic device

A technology of bit accumulator and circuit design, which is applied in the field of FPGA to achieve the effects of excellent timing performance, reducing delay and saving soft IP resources

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

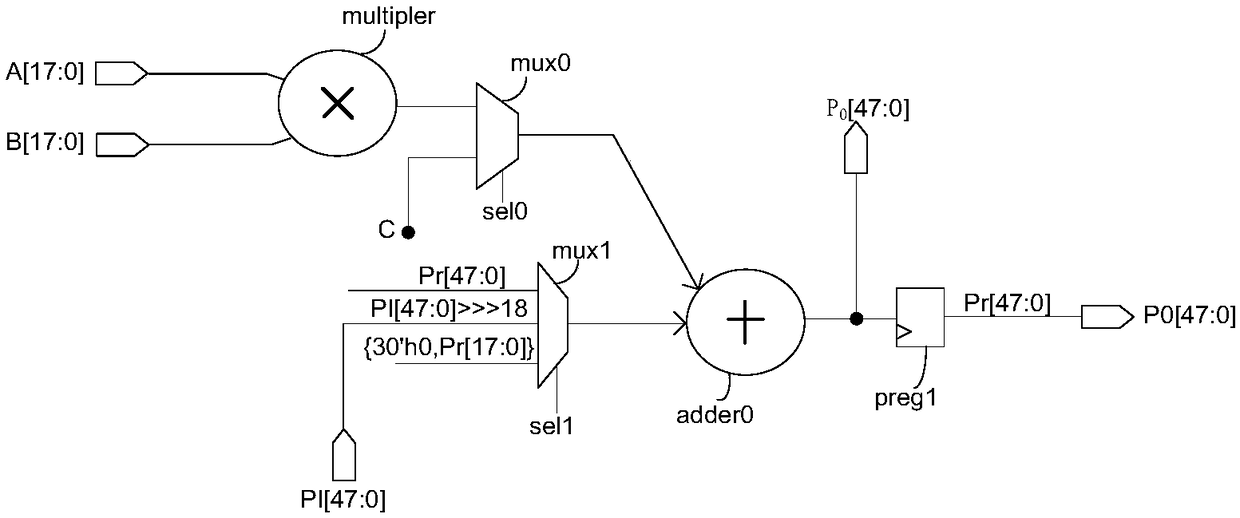

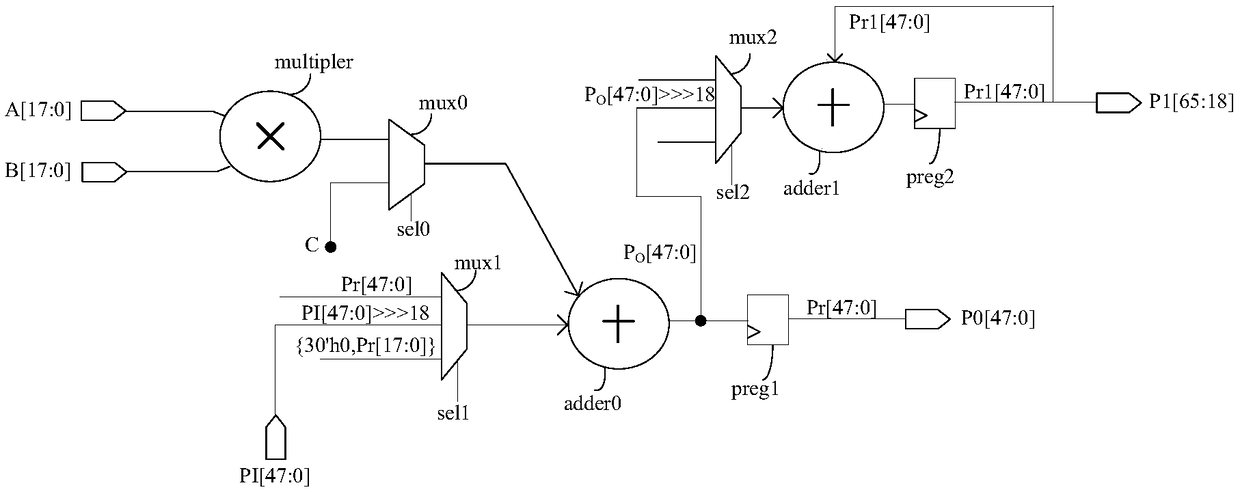

[0031] See figure 1 , figure 1 The schematic diagram of the circuit connection of the wide-bit accumulator circuit provided by the first embodiment of the present invention is represented by figure 1It can be seen that, in this embodiment, the wide-bit accumulator circuit provided by the present invention includes: a first input terminal A, a second input terminal B, a third input terminal C, a fourth input terminal PI, a first output terminal P0, a An adder adder0 and a first branch connected to the first input terminal A, a second input terminal B and a third input terminal C, a second branch connected to the fourth input terminal PI, and the The third branch connected to the first output terminal P0, wherein the two input terminals of the first adder adder0adder0 are respectively connected to the output terminals of the first branch and the second branch, for connecting the first branch and the second The output result of the branch is subjected to operation processing, a...

no. 2 example

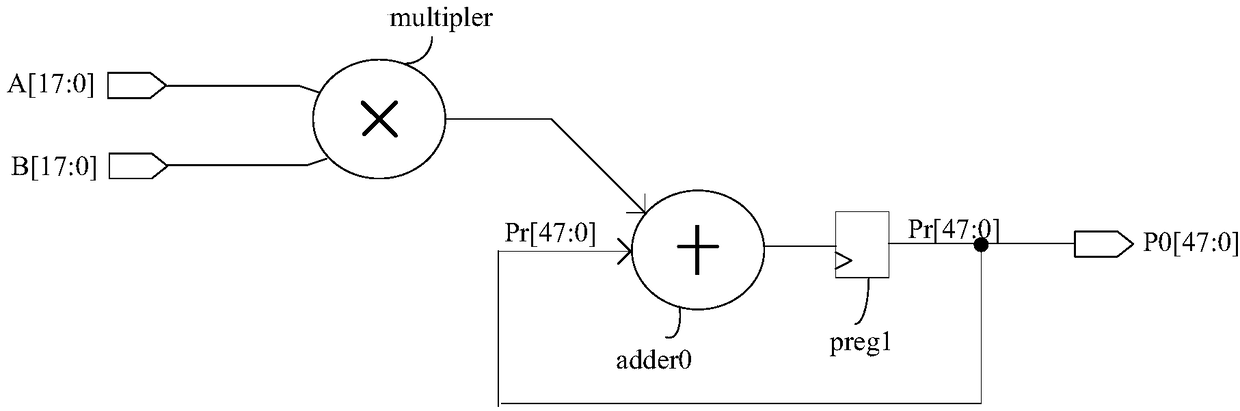

[0047] Figure 5 For the flow chart of the wide-bit accumulator circuit design method provided by the first embodiment of the present invention, please refer to Figure 5 , the wide-bit accumulator circuit includes: a first branch, a second branch, a first output register preg1, a first output terminal P0 connected to the first output register preg1 and a first adder adder0, when designing the The circuit is specifically implemented through hard core configuration, and its configuration design process is as follows:

[0048] S501. Set a multiplier and a first selector mux0 on the first branch.

[0049] In this step, the first branch is configured with a multiplier multiplier and a two-to-one selector through the hard core configuration, and the two input terminals of the multiplier multiplier are respectively connected to the first input terminal A and the second input terminal B Connection, used to receive the data A[17:0] and B[17:0] input by the two input terminals, and m...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com