A method and device for entering a test mode of a security chip

A security chip and test mode technology, applied in static memory, instruments, etc., can solve problems such as poor feasibility, low security, and performance degradation of security chips, and achieve the effects of strong feasibility, improved performance, and improved security

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

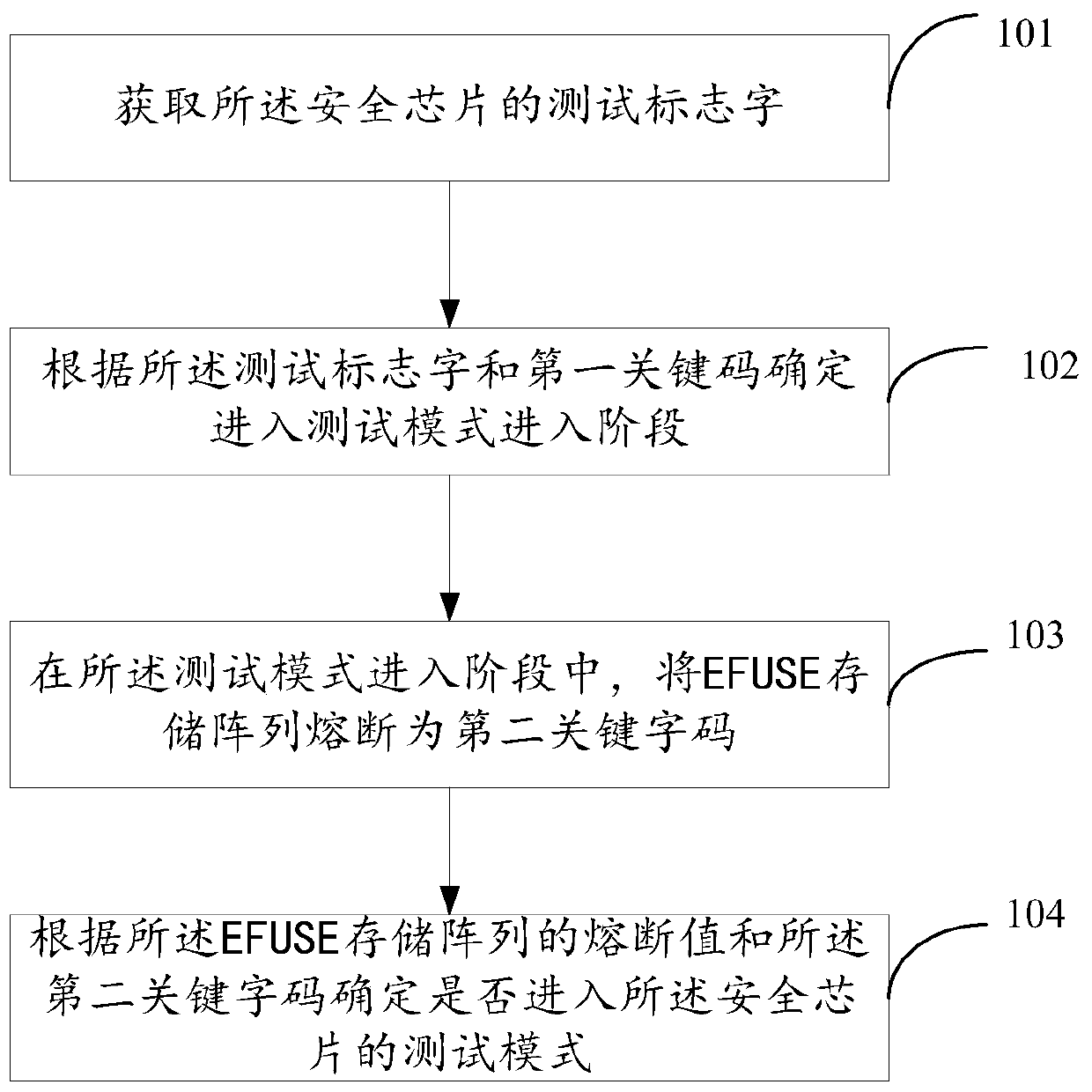

[0040] An embodiment of the present invention provides a method for a security chip to enter a test mode. The method is suitable to be deployed on a device or equipment capable of testing security chips. Such as figure 1 As shown, after the security chip is powered on and started, the method includes:

[0041] 101. Obtain a test flag word of the security chip;

[0042] Wherein, the test flag word can be read from the non-volatile memory.

[0043] 102. Determine to enter the test mode entry stage according to the test flag word and the first key code;

[0044] Optionally, the first key code is a set of fixed first random sequence codes set by the security chip manufacturer;

[0045] In the embodiment of the present invention, two stages of security detection are required before the security chip is tested in a test mode. First, it is necessary to detect whether the process before entering the test meets the safety requirements for entering the test phase, and then determin...

Embodiment 2

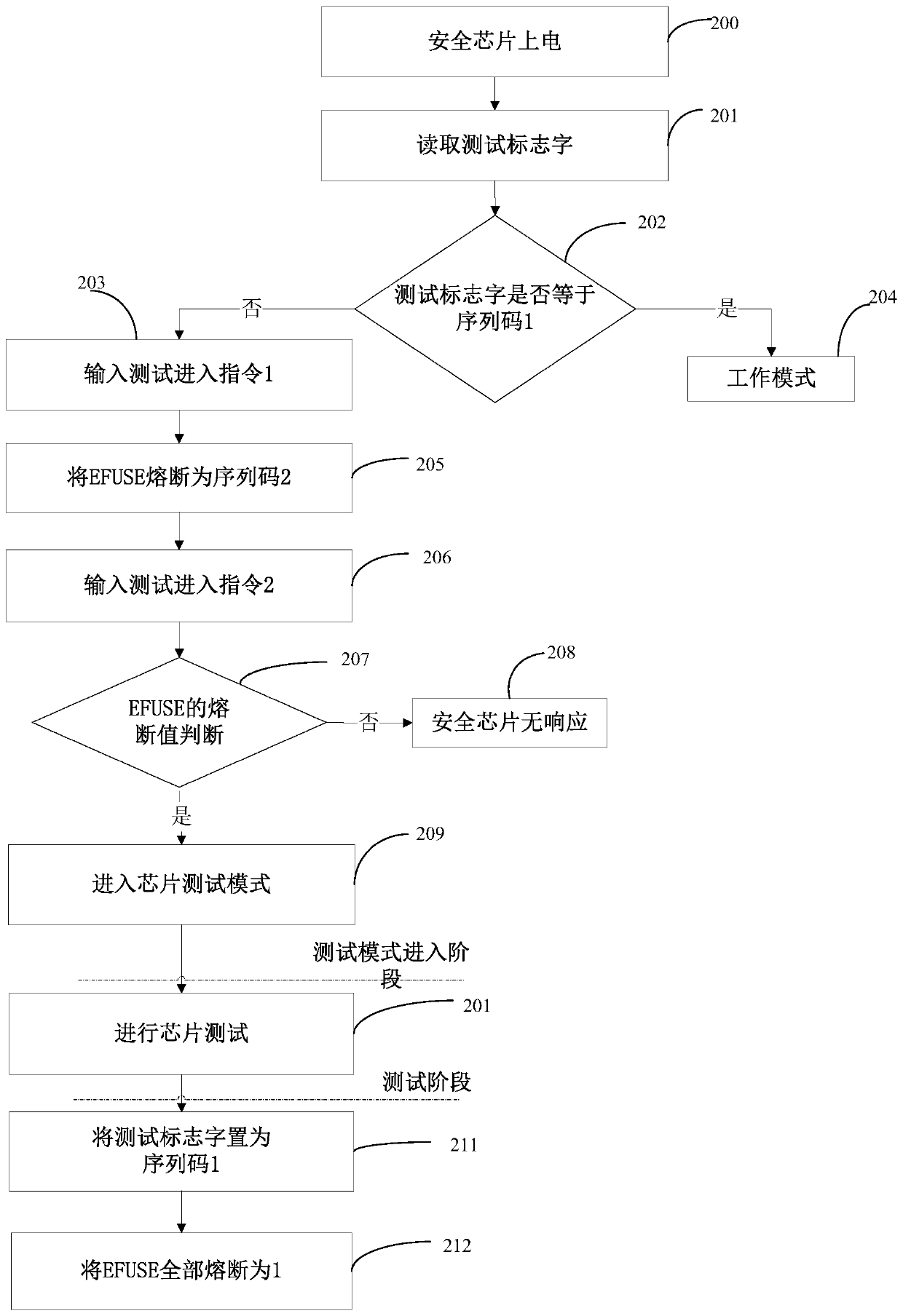

[0058] The embodiment of the present invention specifically describes a method for a security chip to enter a test mode. In the method, a security mechanism for entering the test mode is provided by combining the characteristics of the EFUSE memory. The principle of this security mechanism comes from:

[0059] (1) Introduction to EFUSE memory

[0060] The electronic programmable fuse EFUSE memory adopts the working principle of metal fuse (Metal Fuse) or polycrystalline fuse (Poly Fuse) blown by high current to carry out memory programming.

[0061] Taking the polysilicon fuse as an example, the initial resistance of the polysilicon fuse in the EFUSE memory is very small, and when a large current flows through the polysilicon fuse, the polysilicon fuse is melted. When a large current continues to flow through the polysilicon fuse, it will cause the polysilicon fuse to be blown, the resistance of the polysilicon fuse will double, and it will remain permanently broken, and the ...

Embodiment 3

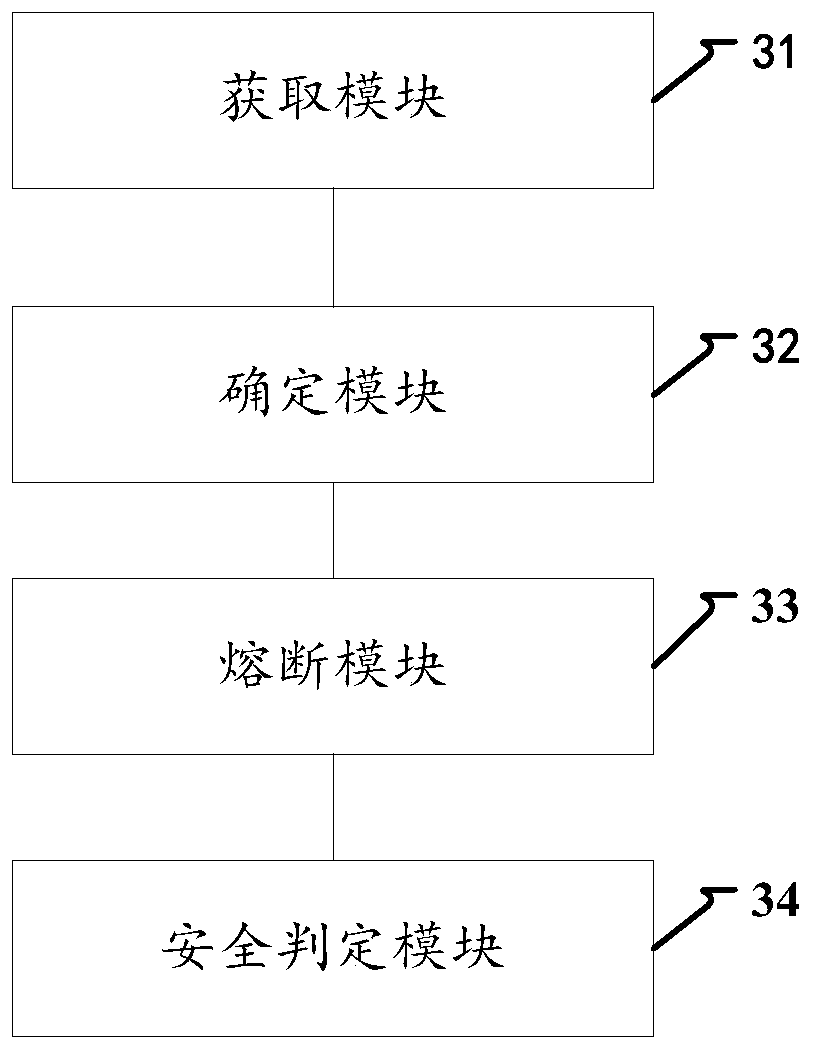

[0099] In order to facilitate the implementation of the methods in the first and second embodiments above, the embodiment of the present invention continues to provide a device for the security chip to enter the test mode, such as image 3 shown, including:

[0100] An acquisition module 31, configured to acquire the test flag word of the security chip;

[0101] Determining module 32, is used for determining to enter the stage of entering test mode according to described test mark word and first key code;

[0102] The fusing module 33 is used to fuse the EFUSE storage array to the second key code during the entry phase of the test mode;

[0103] A security decision module 34, configured to determine whether to enter the test mode of the security chip according to the fusing value of the EFUSE storage array and the second key code.

[0104] In the device provided by the embodiment of the present invention, before entering the test mode of the security chip, first obtain the t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More