Column-level ADCs for cmos image sensors with hybrid CDs

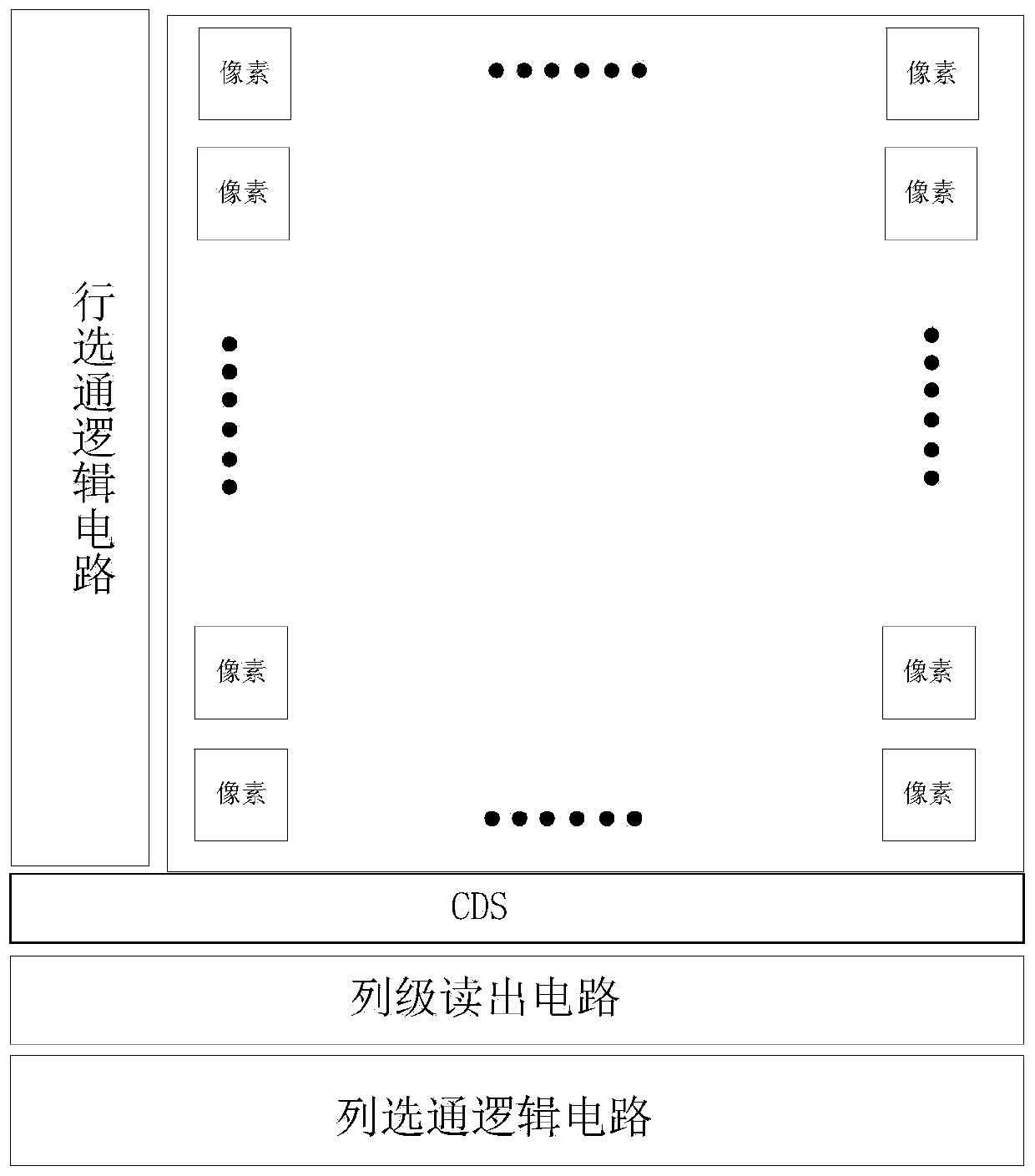

An image sensor and column-level technology, applied in the field of column-level ADC, can solve the problem of reducing the quantization speed of ADC, and achieve the effect of reducing the impact and improving the quantization speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

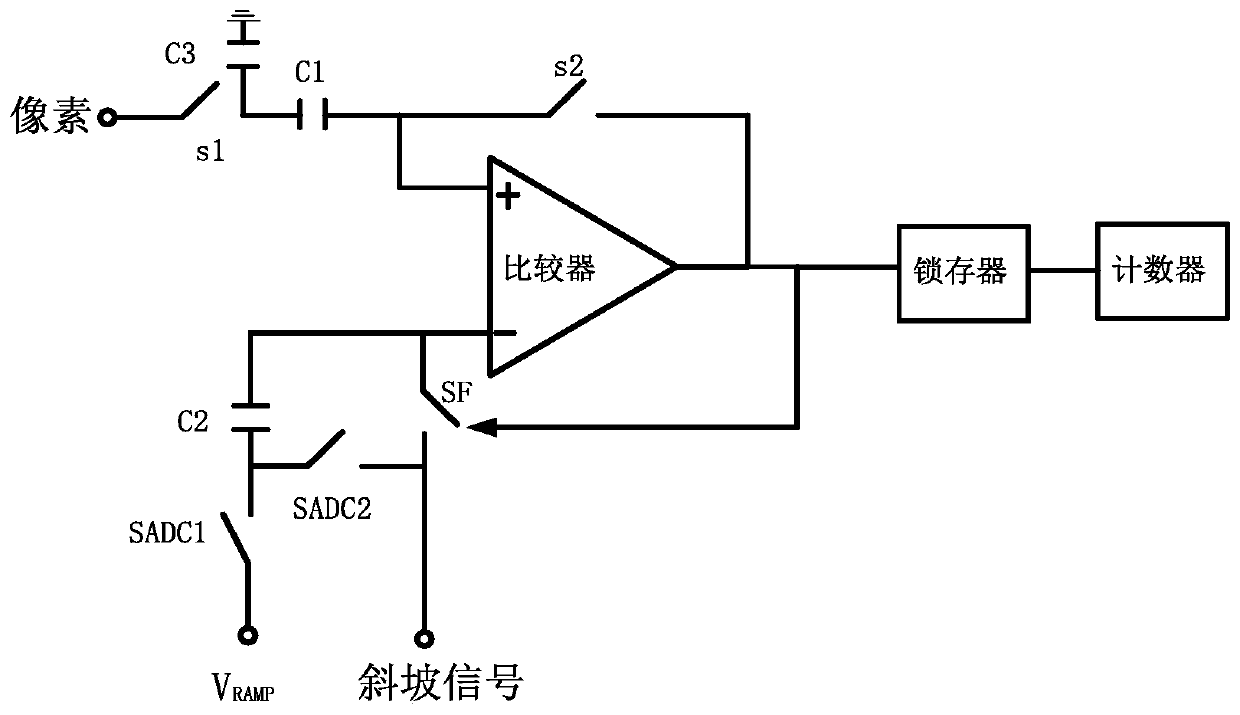

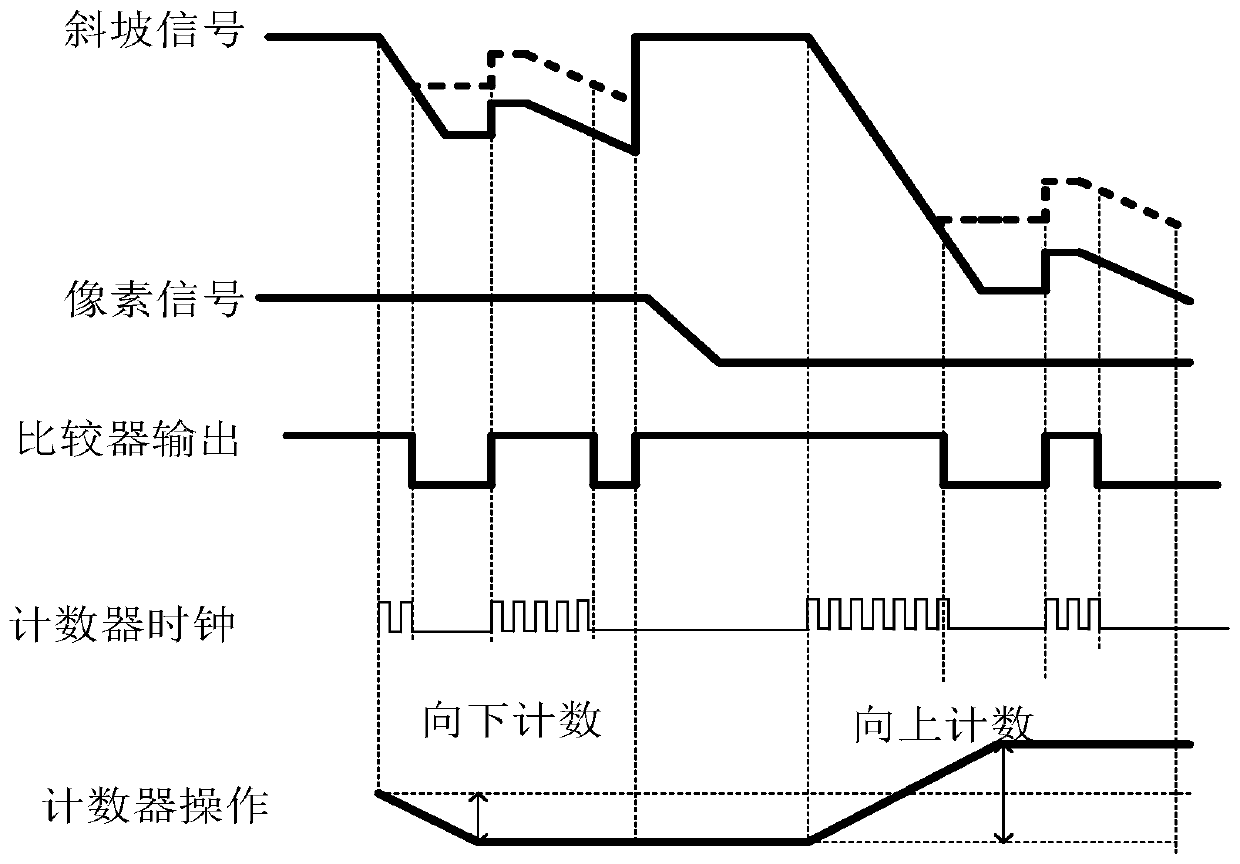

[0012] The technical scheme of the present invention is, adopt the block diagram of the two-step monoclinic rank ADC circuit structure of H-CDS as figure 2 . It includes comparators, latches, counters, capacitors C1, C2, C3 and switches SADC1, SADC2, S1, S2, and SF. The pixel output is connected to the upper plates of the capacitors C1 and C3 through the switch s1. The lower plate of capacitor C3 is grounded, and the lower plate of capacitor C1 is connected to the non-inverting input terminal of the comparator. Moreover, the non-inverting input terminal of the comparator is connected to the output terminal of the comparator through the switch s2. The inverting input terminal of the comparator is connected to the ramp signal through the switch SF, and at the same time, the inverting input terminal is connected to the reference voltage through the capacitor C2 and the switch SADC1. The upper plate of the capacitor C2 is connected to the inverting input terminal of the compar...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More