Formation method for assistance graph

A technology of auxiliary graphics and graphics, which is applied to the photoplate-making process of the patterned surface, the original for photomechanical processing, optics, etc., can solve the problems of large verification time and small process window, and achieve the goal of saving chip verification time Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

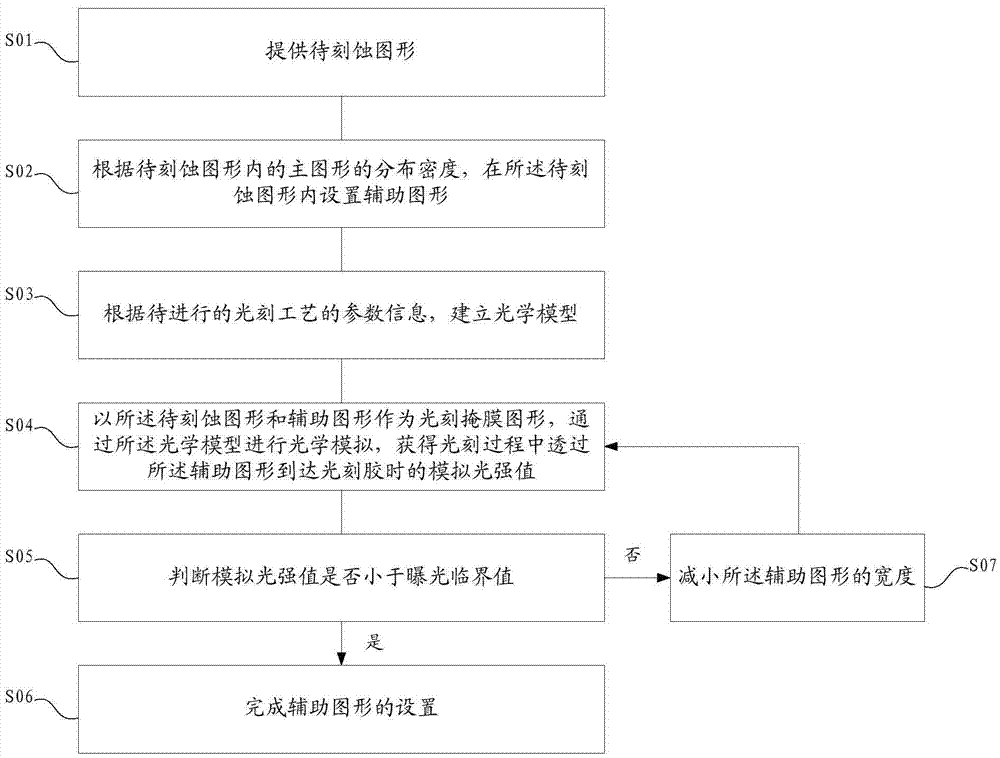

[0029] As mentioned in the background technology, after the auxiliary pattern is formed in the prior art, chip verification is required to determine whether the added auxiliary pattern can form a pattern on the photoresist; until the sub-resolution auxiliary pattern cannot be formed on the photoresist Form a pattern; if the sub-resolution auxiliary pattern can form a pattern on the photoresist, it is necessary to adjust the sub-resolution auxiliary pattern, and then perform chip verification until the sub-resolution auxiliary pattern cannot be formed on the photoresist. Forming a pattern on the glue requires a lot of chip verification time.

[0030] In an embodiment of the present invention, through optical simulation, the simulated light intensity value when passing through the initial auxiliary pattern and reaching the photoresist during the photolithography process is obtained. If the maximum value of the simulated light intensity value is less than the exposure critical val...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More