How the transistor is formed

A transistor and well region technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of easy breakdown of the gate dielectric layer and affect the withstand voltage performance of LDMOS, so as to reduce the breakdown phenomenon and improve the The effect of uneven threshold voltage distribution and improved performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] It can be seen from the background art that the LDMOS in the prior art has the problem that the gate dielectric layer is easily broken down. Now combined with the structure of LDMOS in the prior art, the reason why the gate dielectric layer is easy to be broken down is analyzed:

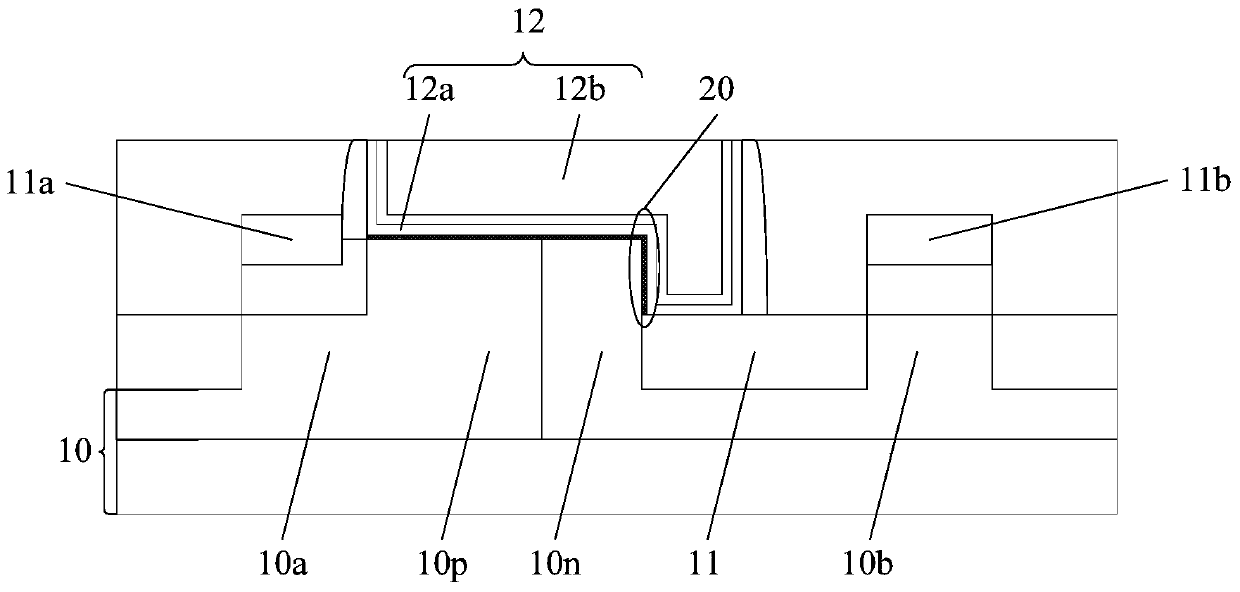

[0037] refer to figure 1 , shows a schematic structural diagram of an LDMOS in the prior art.

[0038] Such as figure 1 shown, the LDMOS includes:

[0039] The adjacent P-type well region 10p and N-type well region 10n are formed in the substrate 10; the isolation structure 11 located in the N-type region, the top surface of the isolation structure 11 is lower than the P-type well region 10p and the The top surface of the N-type well region 10n; the gate structure 12 located on the surface of the substrate 10, the gate structure 12 covering the top of the P-type well region 10p, the top and side walls of the N-type well region 10n, and part of the surface of the top of the isolation structu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More