Method of filling through-holes to reduce voids and other defects

A substrate and a predetermined time period technology, which is applied in the plating of superimposed layers, liquid chemical plating, and the formation of electrical connections of printed components, etc., can solve the problems of worker error leaving space and low efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

example 1

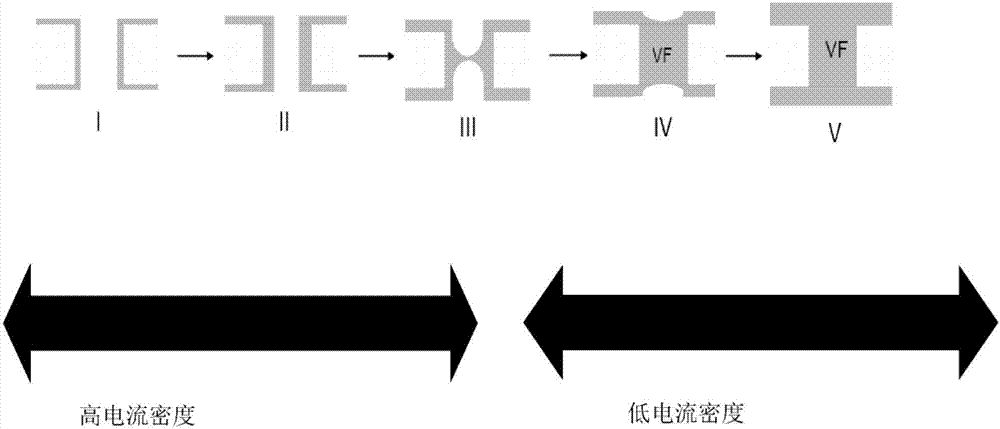

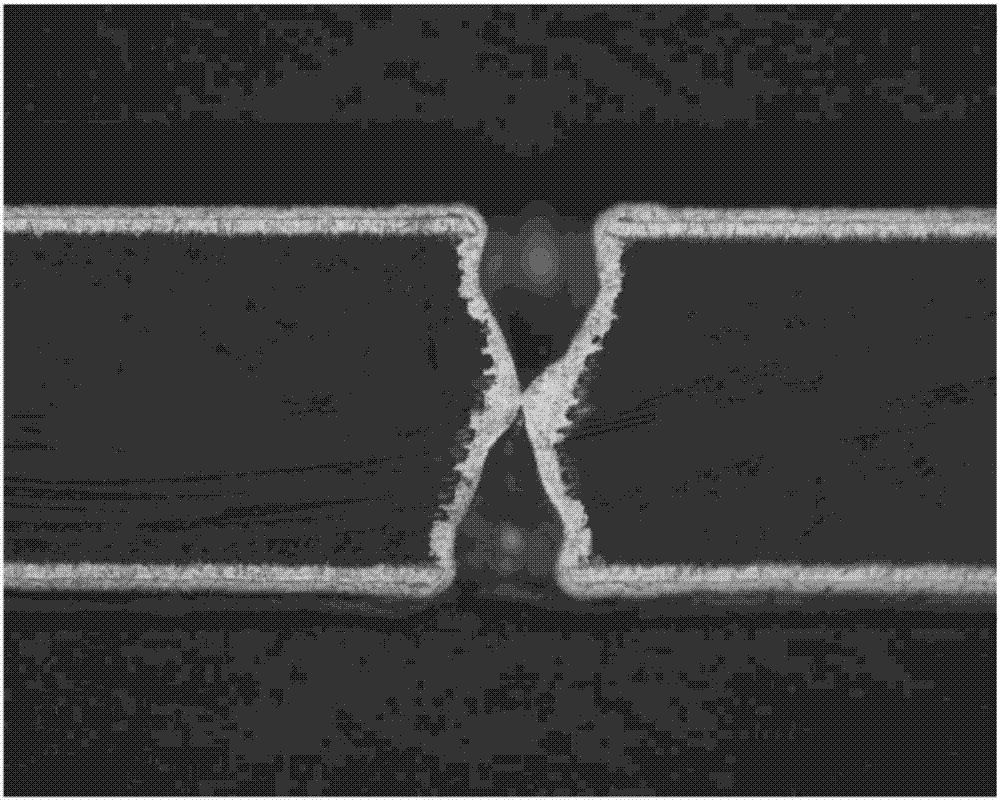

[0044] FR4 / glass-epoxy coupons 5 cm wide, 15 cm long, and 200 μm thick with multiple through holes were supplied by Tech Circuit. The average diameter of the via holes is 100 μm. CIRCUPOSIT for test strips TM 880 Electroless Process Plating Formulation and Method (available from Dow Electronic Materials, Marlborough, Mass.) plated to form a copper layer on one side of the coupon and on the walls of the vias. The thickness of the copper layer on the test piece was 0.3 μm. Pre-clean the coupons with a regular copper cleaner. The coupons were then placed in a Haring cell containing a copper electroplating bath having the formulation as indicated in the table.

[0045] sheet

[0046] components quantity copper sulfate pentahydrate 220g / L sulfuric acid 40g / L Chloride ions from hydrochloric acid 50ppm polyethylene glycol 2g / L 4-Phenylimidazole / Imidazole / 1,4-Butanediol Diglycidyl Ether Copolymer 50mg / L (sulfopropyl)-disodium dis...

example 2

[0048] Example 2 (comparison)

[0049] FR4 / glass-epoxy coupons 5 cm wide, 15 cm long, and 200 μm thick with multiple through holes were supplied by Tech Circuit. The average diameter of the via holes is 100 μm. CIRCUPOSIT for test strips TM 880 Electroless Process Plating Formulation and Method (available from Dow Electronic Materials, Marlborough, Mass.) plated to form a copper layer on one side of the coupon and on the walls of the vias. The thickness of the copper layer on each test piece was 0.3 μm. Pre-clean the coupons with a regular copper cleaner. The coupons were then placed in a Harlem cell containing a copper electroplating bath having the formulation as shown in the table in Example 1.

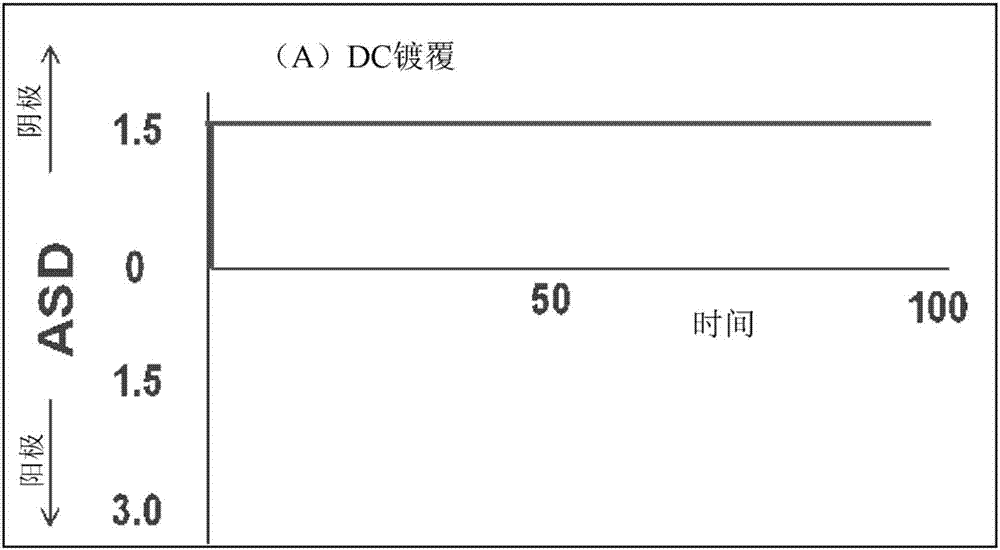

[0050] Connect the coupon to a conventional DC rectifier. The counter electrode in a Haring cell is an insoluble anode. The plating bath was air agitated at 4 liters / minute during electroplating. Plating was performed at room temperature for 63 minutes. The current density ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| diameter | aaaaa | aaaaa |

| number average molecular weight | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More