Apparatus and method for managing breakdown of eeprom memory access transistors

A memory and memory cell technology, applied in the field of memory, can solve the problems of inappropriate consumption, limited increase in duration of erasing and programming high-voltage pulse applications, unacceptable number of programming times, etc., and achieve the effect of avoiding breakdown and leakage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

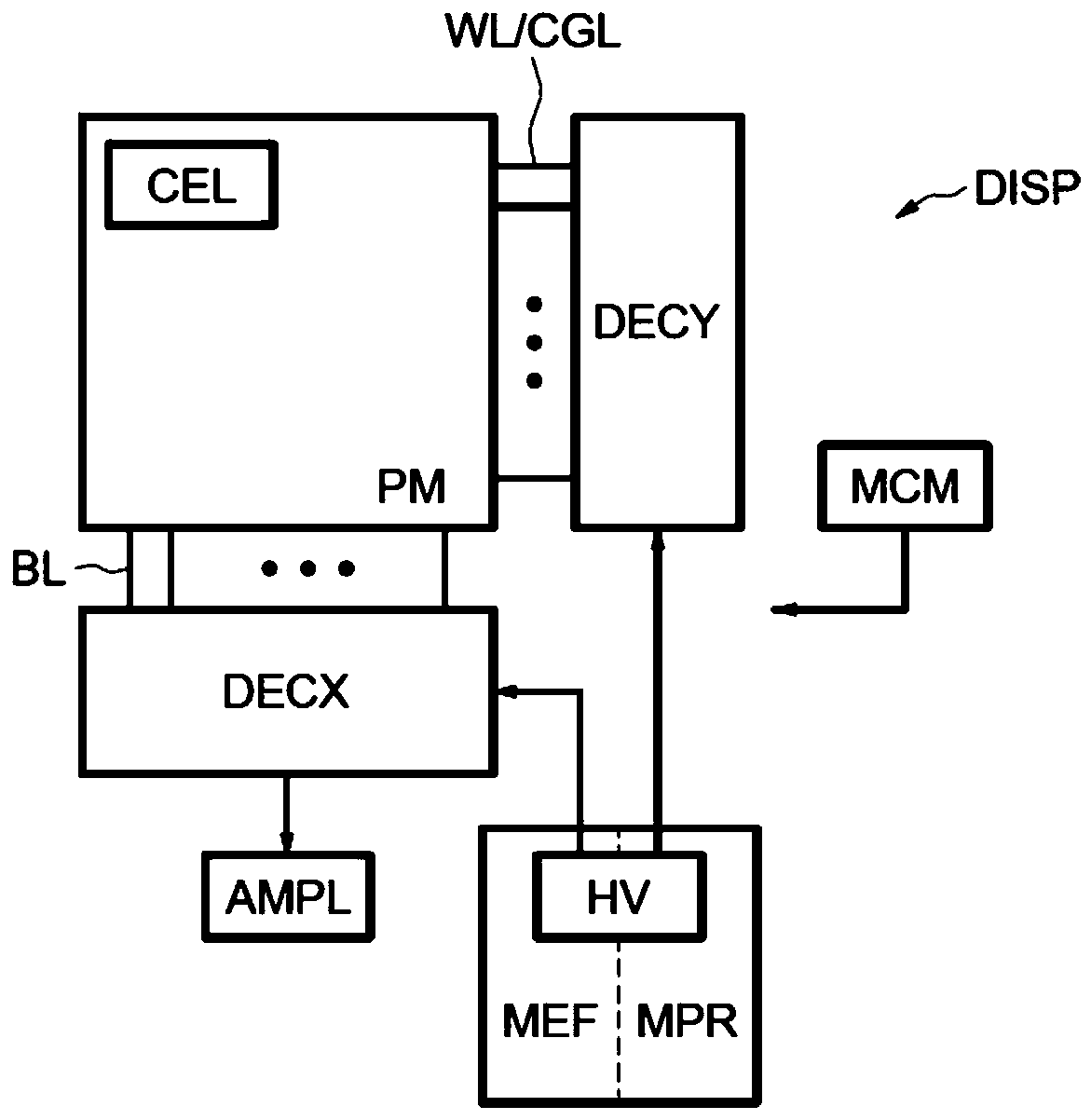

[0036] exist figure 1 In , reference numeral DISP denotes an example of an EEPROM type memory device according to the present invention.

[0037] This means DISP comprises a memory plate PM of memory cells CEL, as well as programming means MPR and erasing means MEF notably comprising means HV allowing high programming or erasing voltages to be applied, row and column decoders DECY and DECX and comprising Read device for read amplifier AMPL.

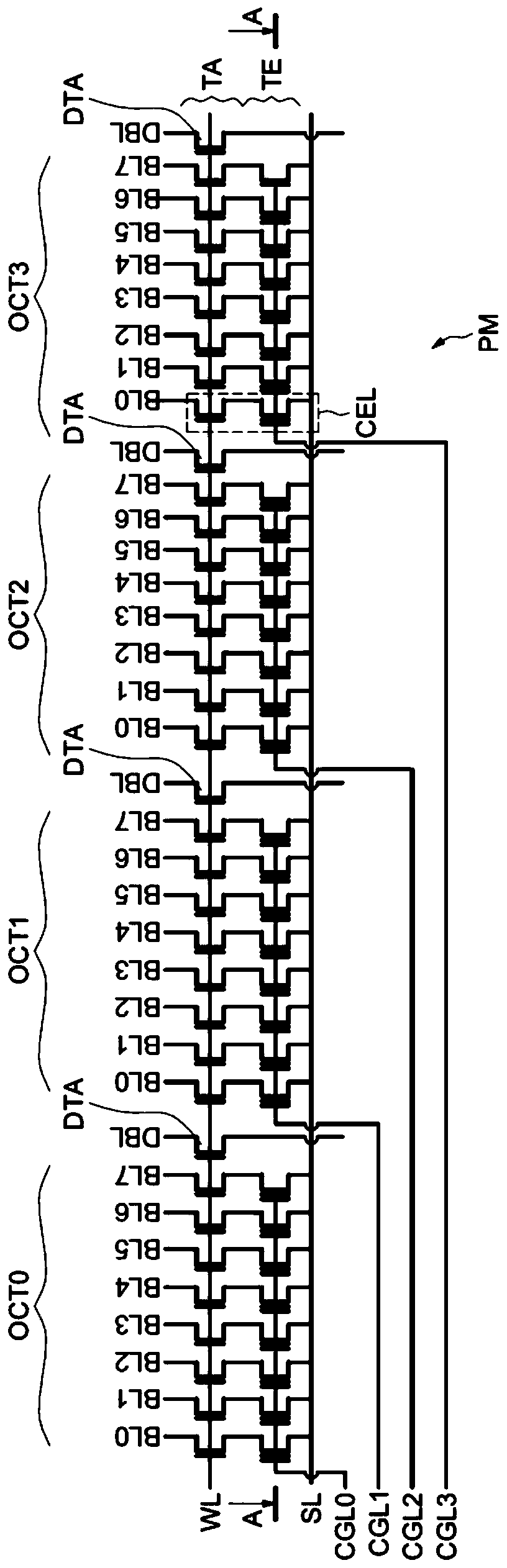

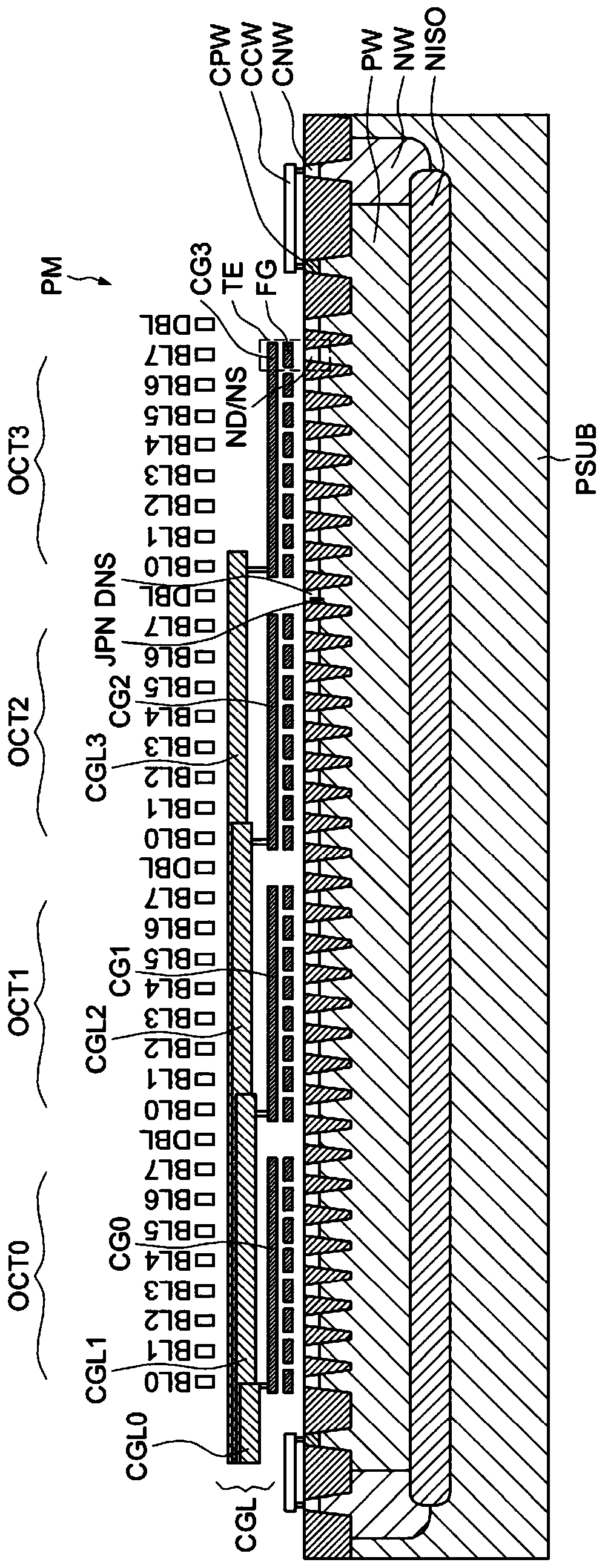

[0038] The row decoder DECY and the column decoder DECX are notably controlled by the programming means MPR and the erasing means MEF and are configured to pass through word lines and control lines WL / CGL respectively and via bit lines BL, for example by means of control blocks. A signal is sent to select a memory cell.

[0039] The means DIS also comprise control means MCM comprising, for example, logic means capable of implementing notably the conventional structure of the respective programming means MPR, erasing means MEF and readi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com