Adaptive slope compensation circuit suitable for controlling buck converter in peak current mode

A peak current and slope compensation technology, applied in the direction of converting DC power input to DC power output, regulating electrical variables, and controlling/regulating systems, etc. It can solve the problems of quantity and other issues, so as to achieve the effect of simple and easy solution, avoiding sub-harmonic oscillation and reducing the load capacity of the system.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] The technical solution of the present invention will be specifically described below in conjunction with the accompanying drawings and specific embodiments:

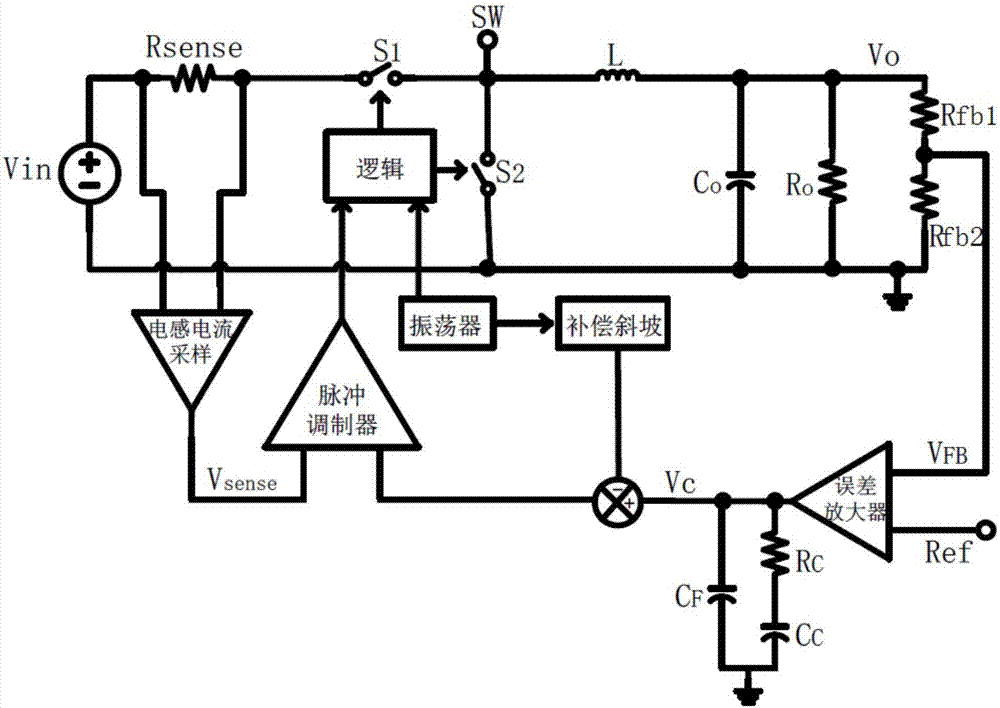

[0025] figure 1 Shown is the schematic control diagram of the peak current mode control type step-down converter loop, which includes the input voltage Vin, the inductor L, the upper and lower power transistors S1 and S2, the output capacitor Co and the output load Ro, and the output voltage is Vo . The time when the upper tube is turned on and the lower tube is turned off is Ton, and the end mark is when the sampling inductor current after the superimposed compensation slope touches the output Vc of the error amplifier (EA). Here, the error amplifier adopts type II compensation, and its compensation network is composed of RC, CC, and CF located at the output end of the error amplifier; the time when the upper tube is turned off and the lower tube is turned on is Toff, because the peak current mode control type s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com