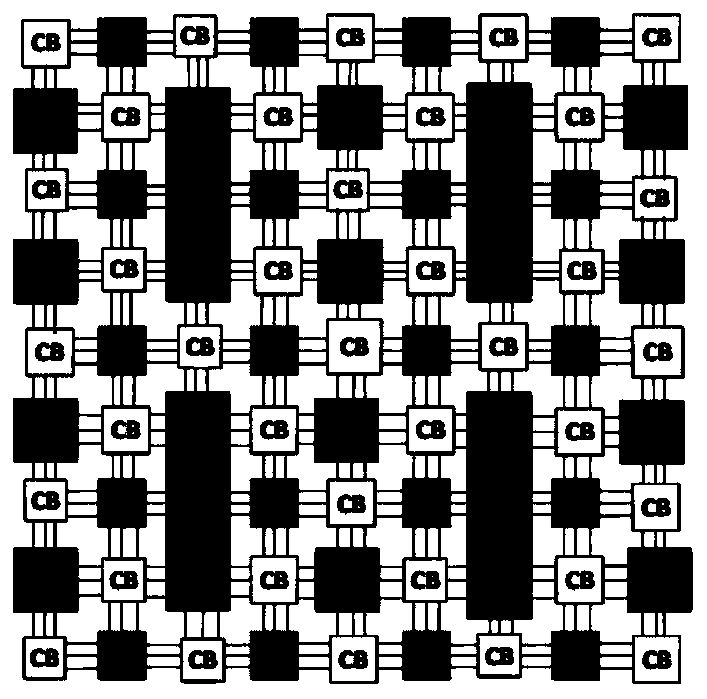

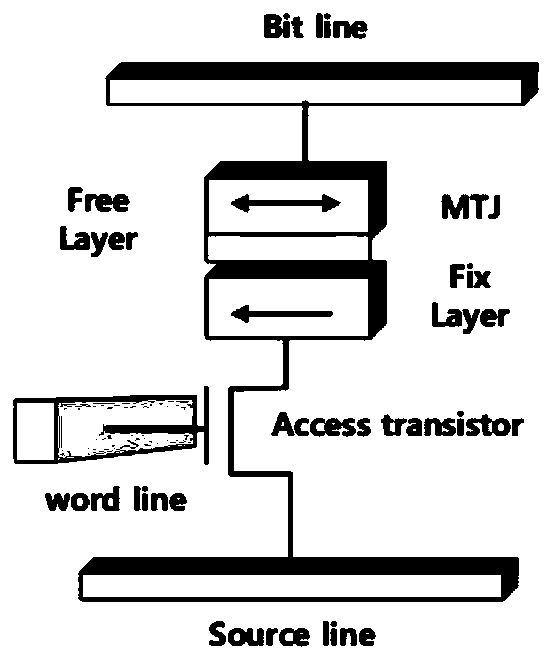

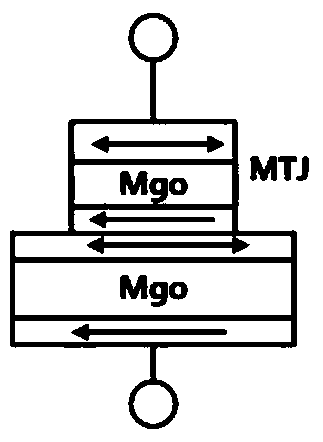

Architecture and design method of fpga BRAM based on non-volatile memory

A non-volatile, architecture design technology, applied in CAD circuit design, instrumentation, calculation, etc., can solve the problems of delay and high power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach

[0089] like Figure 5 As shown, the process of using VTR7.0 for FPGA design is:

[0090] Step (1): Input the detailed description of the circuit and architecture. The benchmark requires the use of Verilog 1995 version. The detailed description of the architecture refers to the description of the underlying hardware by k6_frac_N10_mem32K_40nm.xml;

[0091] Step (2): Carry out logic synthesis and optimization;

[0092] Perform logic synthesis on the input RTL level circuit to generate a gate level circuit (generate .blif file). During the optimization process, remove some useless redundant wiring mappings in the circuit.

[0093] Step (3): Packing, packing gate-level circuits into logic blocks, and generating netlist file .net;

[0094] Step (4): carry out the layout, which means that the tool automatically arranges the optimal position of each logic block;

[0095] Step (5): Perform wiring. Wiring means that the tool automatically connects each logic block, after which the c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More