Semiconductor packaging method capable of improving precision of upper cover plate

A packaging method and semiconductor technology, which is applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., to achieve the effect of improving assembly yield

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] The present invention will be further described below in conjunction with the accompanying drawings and specific embodiments, so that those skilled in the art can better understand the present invention and implement it, but the examples given are not intended to limit the present invention.

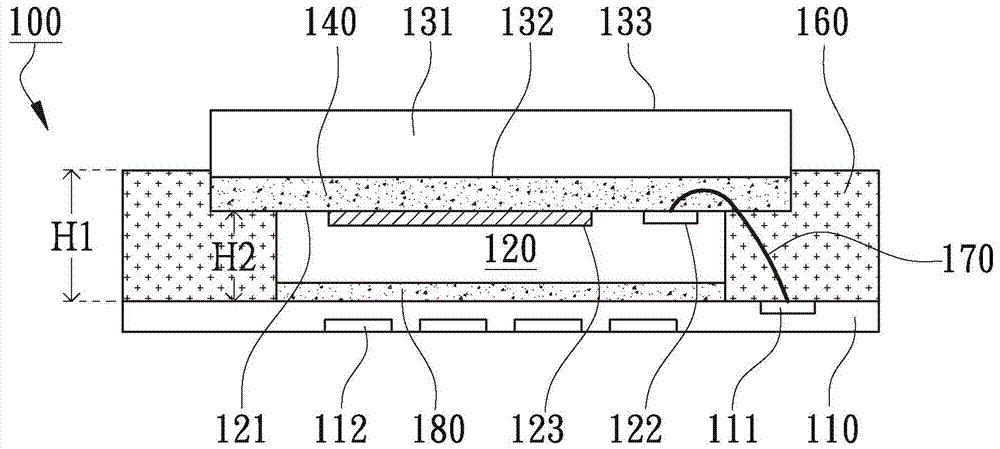

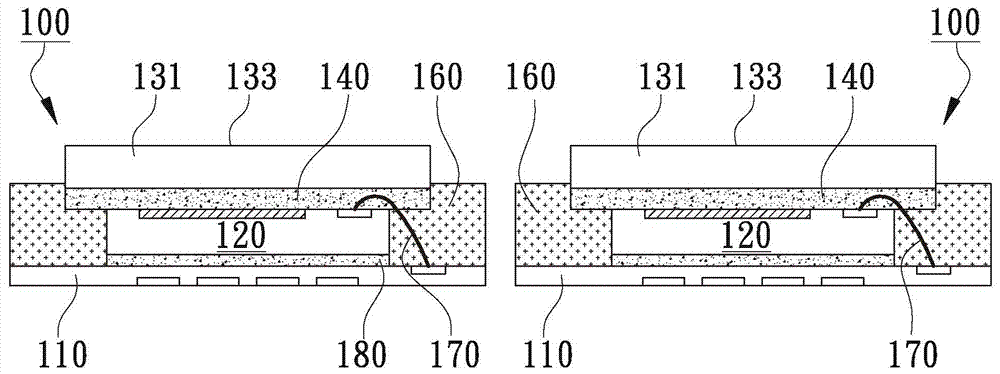

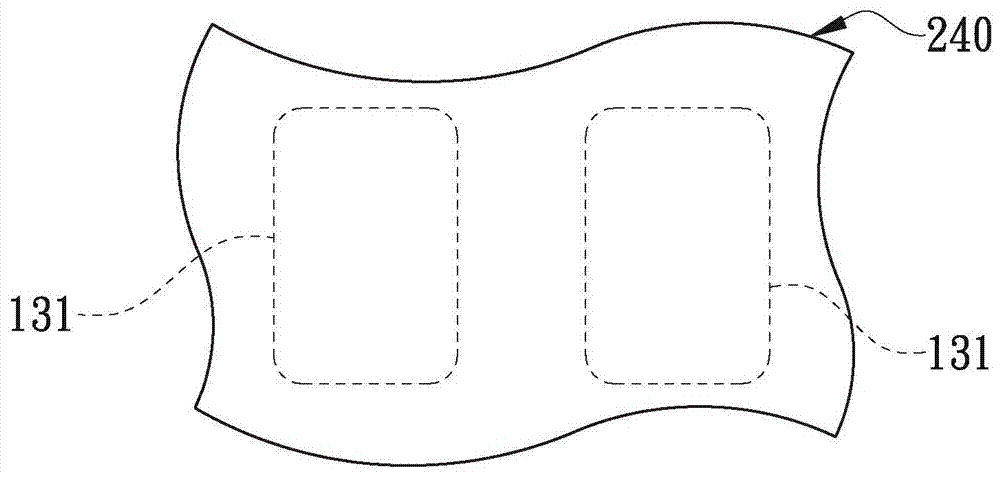

[0037] According to a specific embodiment of the present invention, a semiconductor packaging structure 100 manufactured by a semiconductor packaging method is illustrated in figure 1 cross-sectional schematic diagram. Figure 2A to Figure 2I A schematic cross-sectional view of components showing each main step in a semiconductor packaging method. Figure 3A to Figure 3D A schematic diagram of the surface of the cover plate is shown in the process of adding identification feature points in the semiconductor packaging method.

[0038] see figure 1 , a semiconductor packaging structure 100 disclosed in the present invention mainly includes a substrate 110 , a chip 120 , a cover pl...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More