A Parallel Communication Method

A communication method and a technology of communication status, which are applied in the direction of instruments, electrical digital data processing, etc., can solve the problems of fewer timing links, more timing links, and fewer bus pins, so as to avoid logical conflicts, have fewer timing links, and read The effect of fast writing speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] In order to fully understand the technical content of the present invention, the technical solution of the present invention will be further introduced and illustrated below in conjunction with schematic diagrams, but is not limited thereto.

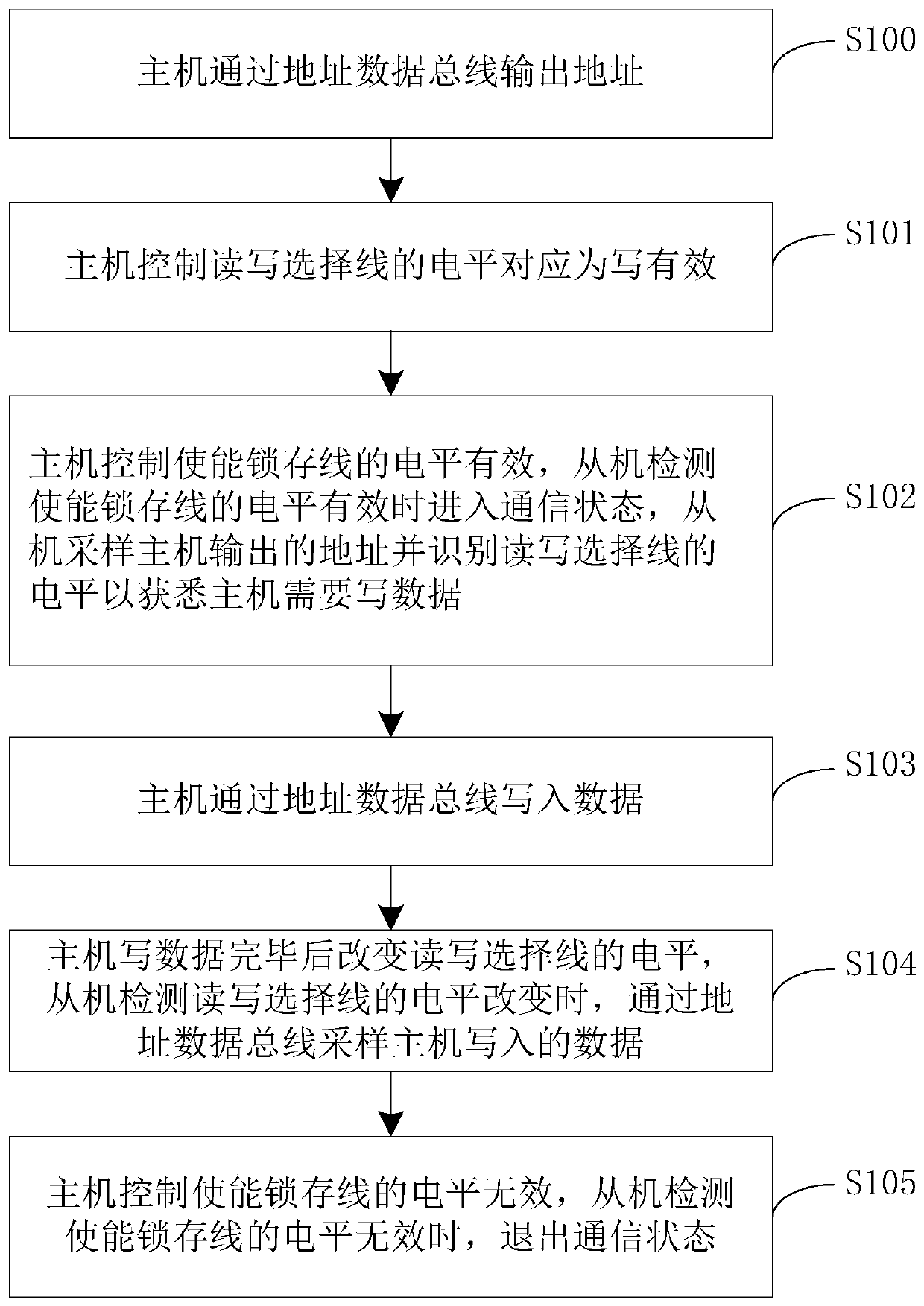

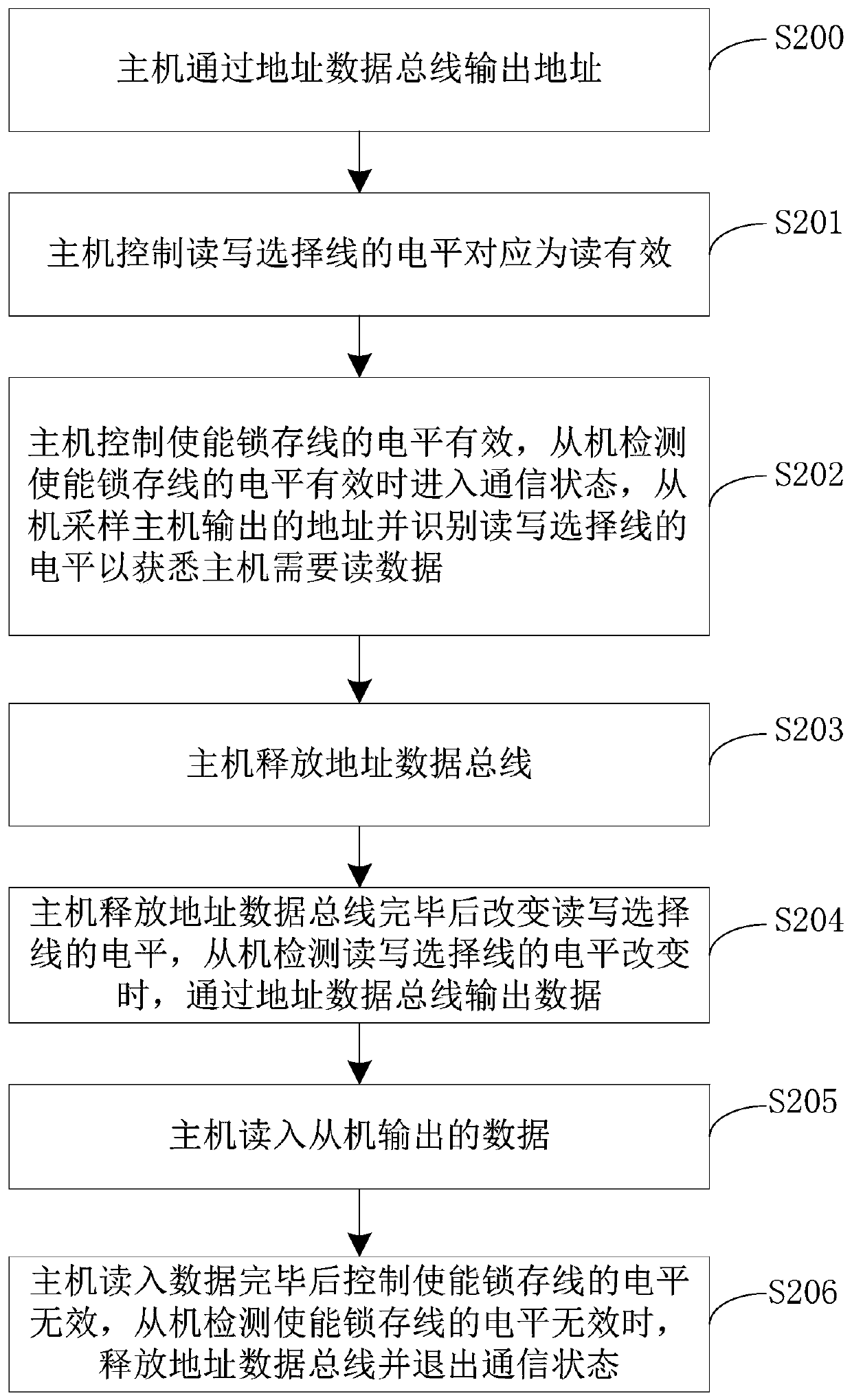

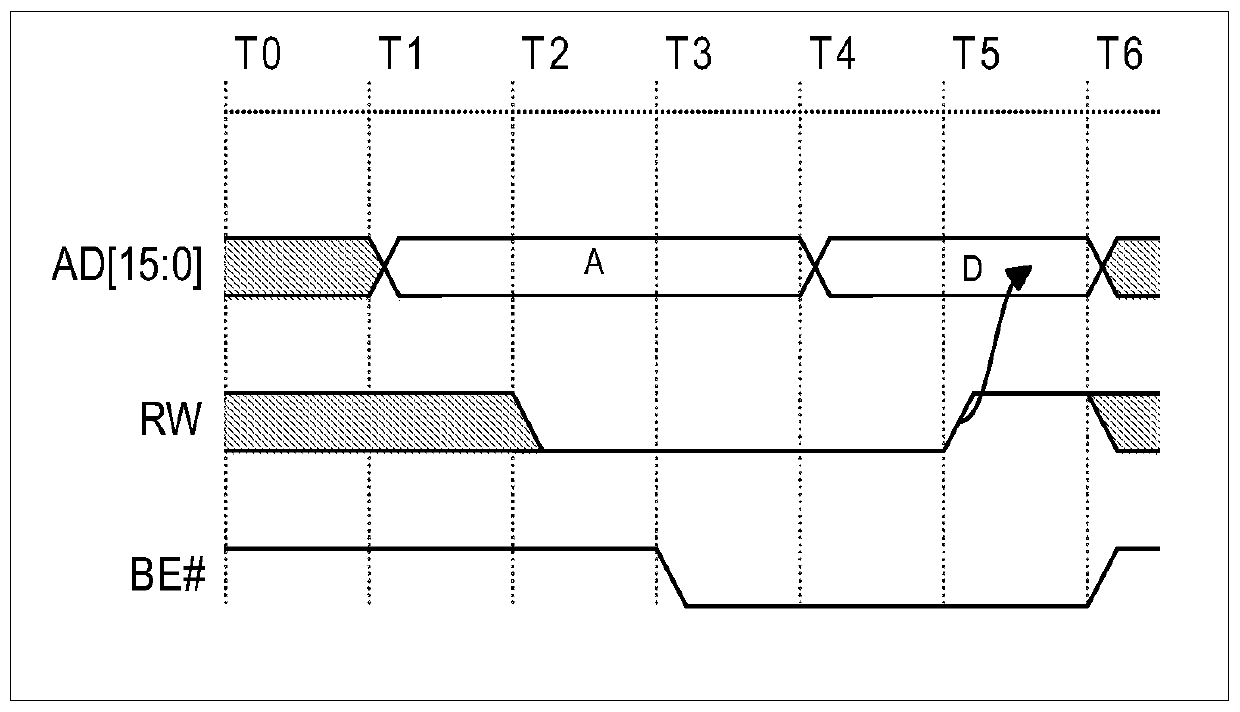

[0042] Such as Figure 1 to Figure 4As shown, in the present invention, the parallel communication method includes a bus connected between a master and a slave for parallel communication, and the bus includes an address data bus, a read / write selection line and an enable latch line. In this embodiment, the addressing space of the master is 64KB, and there are 16 address data buses, 1 read-write selection line and 1 enable latch line in the bus. The master and the slave are connected through these 18 lines. Can finish communication, its bus number is identical with the HCS12 single-chip microcomputer MEBI bus of the prior art, but it is less than the number of the PC machine ISA bus and the MCS-51 single-chip microcomputer bus of t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More