Processor chip emulator with nonvolatile memory

A non-volatile memory technology, applied in software simulation/interpretation/simulation, faulty computer hardware detection, memory address/allocation/relocation, etc., can solve non-volatile memory performance inconsistency, troublesome use, Problems such as complex process, to achieve the effect of improving usability and debugging performance, ensuring functions, and facilitating development

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

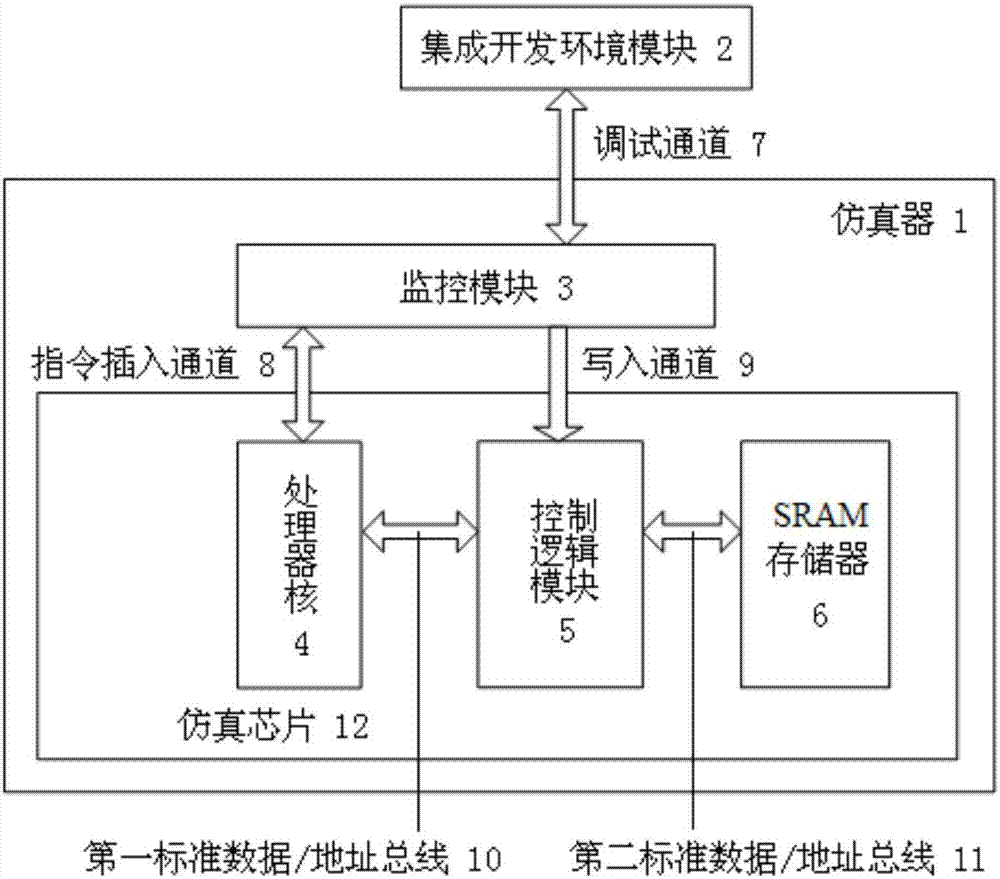

[0015] like figure 1 As shown, the processor chip emulator 1 with non-volatile memory (i.e. figure 1 The emulator in the emulator) includes: a monitoring module 3 and an emulation chip 12, and an integrated development environment module 2 installed on the user's computer. The simulation chip 12 includes a processor core 4 , a control logic module 5 and an SRAM memory 6 . The monitoring module 3 is connected with the integrated development environment module 2 through the debugging channel 7 . The SRAM memory 6 is connected to the control logic module 5 through the second standard data / address bus 11 , and the control logic module 5 is connected to the processor core 4 through the first standard data / address bus 10 . The monitoring module 3 is connected with the control logic module 5 in the emulation chip 12 through the writing channel 9 , and the monitoring module 3 is connected with the processor core 4 in the emulation chip 12 through the instruction insertion channel 8 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More