Half period time delay circuit

A delay circuit, half-cycle technology, applied in the direction of electrical components, pulse processing, pulse technology, etc., can solve the problems of signal transmission distortion, large area and power consumption cost, multiple MOS tubes, etc., and achieve strong resistance to common mode noise interference ability, enhanced resistance, and the effect of saving chip area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

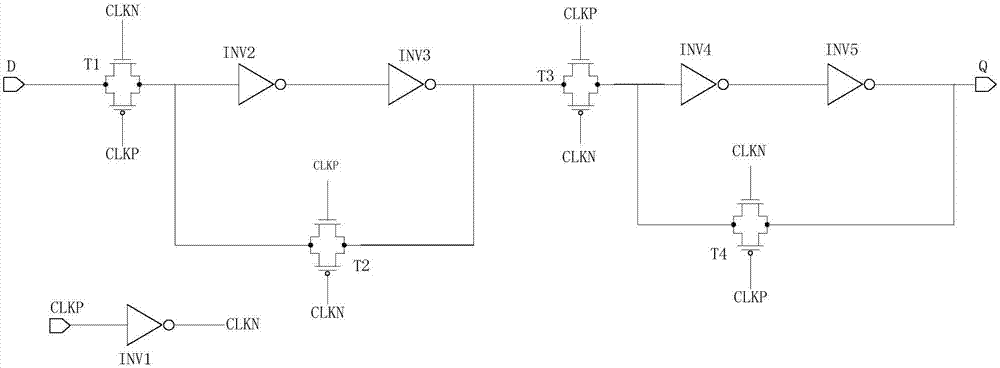

[0021] Embodiments of the present invention will now be described with reference to the drawings, in which like reference numerals represent like elements. As mentioned above, the present invention provides a half-cycle delay circuit. The half-cycle delay circuit of the present invention reduces the number of field effect transistors that need to be used, saves power consumption and the area occupied by chips; at the same time, it enhances the Anti-common mode noise interference capability.

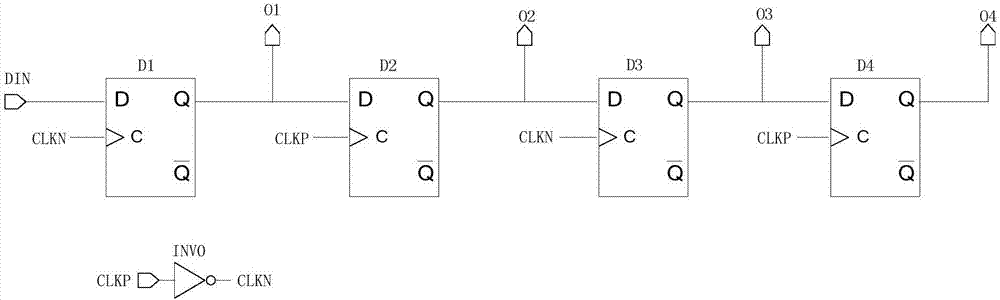

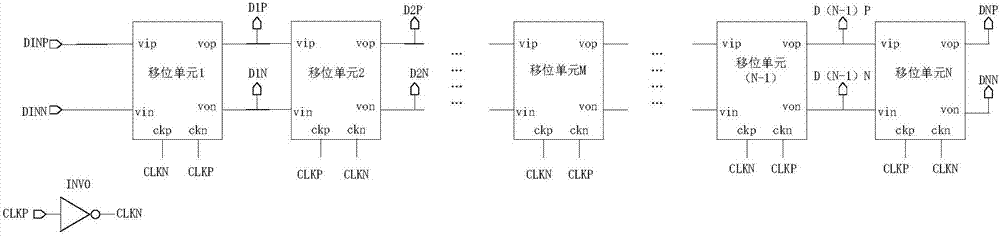

[0022] Please refer to image 3 , image 3 Structural diagram of the half-period delay circuit of the present invention. As shown in the figure, the half-cycle delay circuit of the present invention carries out N half-cycle delays to the input digital signal (DINN, DINP); the half-cycle delay circuit of the present invention includes an inverter INV0 and N shift unit (shift unit 1, 2...N), and N is a natural number greater than 1. Of course, in actual use, the value of N can be flexibl...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More