A dynamic reconfiguration controller for fpga against single event effect

An anti-single event effect and dynamic reconfiguration technology, which is applied to architectures, instruments, and computers with a single central processing unit, can solve problems that affect the correct operation of the system, errors in the reconstruction process, and high sensitivity to single event effects, etc. question

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

[0024] For the convenience of description, the relevant technical terms appearing in the specific implementation are explained first:

[0025] SRAM (Static Random Access Memory): static random access memory;

[0026] FSM (Finite State Machine): finite state machine;

[0027] ICAP (Internal Configuration Access Port): internal configuration access channel;

[0028] MV (Majority Voter): majority voter

[0029] BRAM (Block Random Access Memory): block memory;

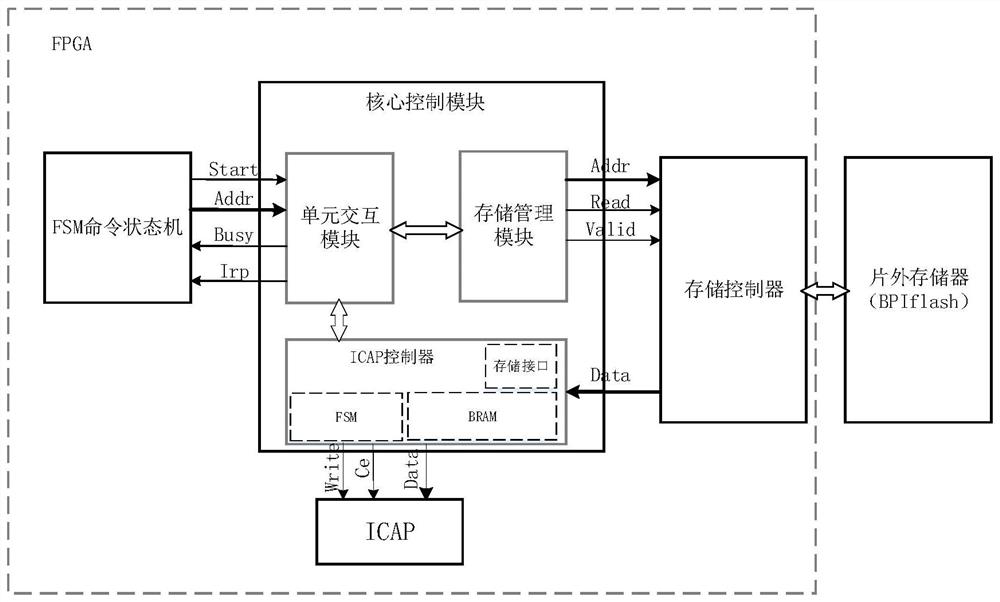

[0030] figure 1 It is a schematic diagram of an FPGA dynamic reconfiguration controller for anti-single event effect of the present invention.

[0031] In this example, if figure 1 As shown, the present invention is an anti-single event effect FPGA dynamic reconfiguration controller, including: FSM command state machine, core control module, memory controller, ICAP unit and off-chip memory.

[0032] Below we combine figure 1 In detail, specifically:

[0033] FSM command state machine, including all reconstruction m...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More