Logic circuit for zero-relay extraction of image sharpness information in assembly line mode and extraction method

A logic circuit and assembly line technology, applied in image communication, television, electrical components, etc., can solve problems such as target tracking failure and timing delay, and achieve the effect of one-button focusing, improved integration, and real-time servo autofocus

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] Now in conjunction with embodiment, accompanying drawing, the present invention will be further described:

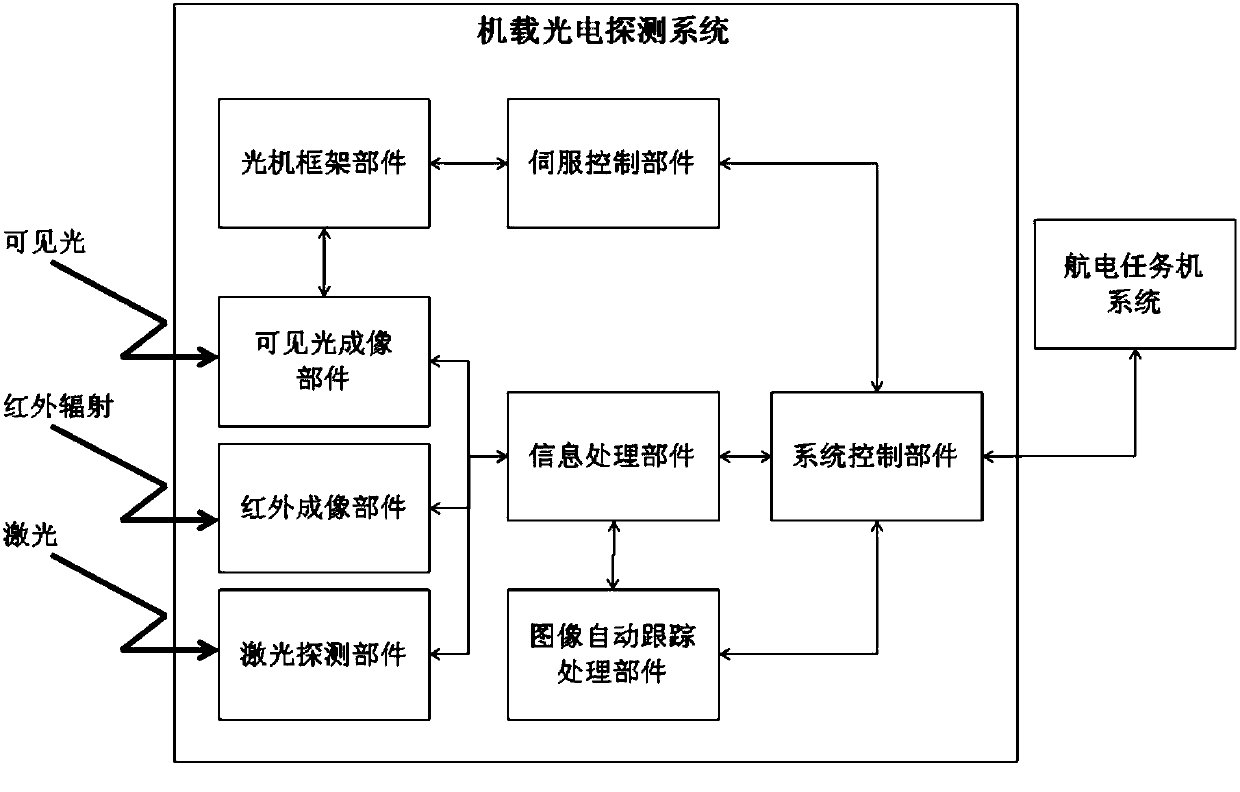

[0031] The visible light video source of a certain type of airborne photoelectric detection device adopts the high-definition SDI format. The front end of the visible light imaging component is equipped with a visible light video acquisition circuit, and the rear end is equipped with a digital focus control circuit. The middle section implements the logic circuit described in the present invention. The automatic focus function needs to be completed by the relevant program software associated with the present invention.

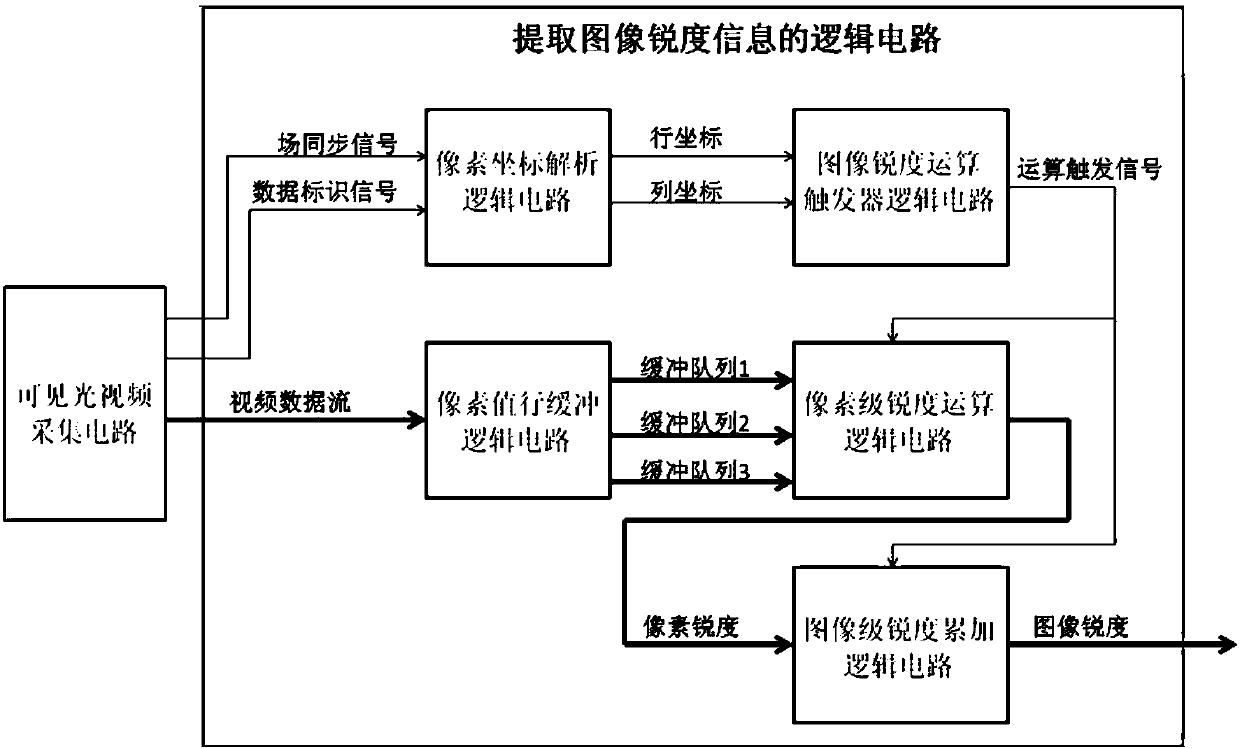

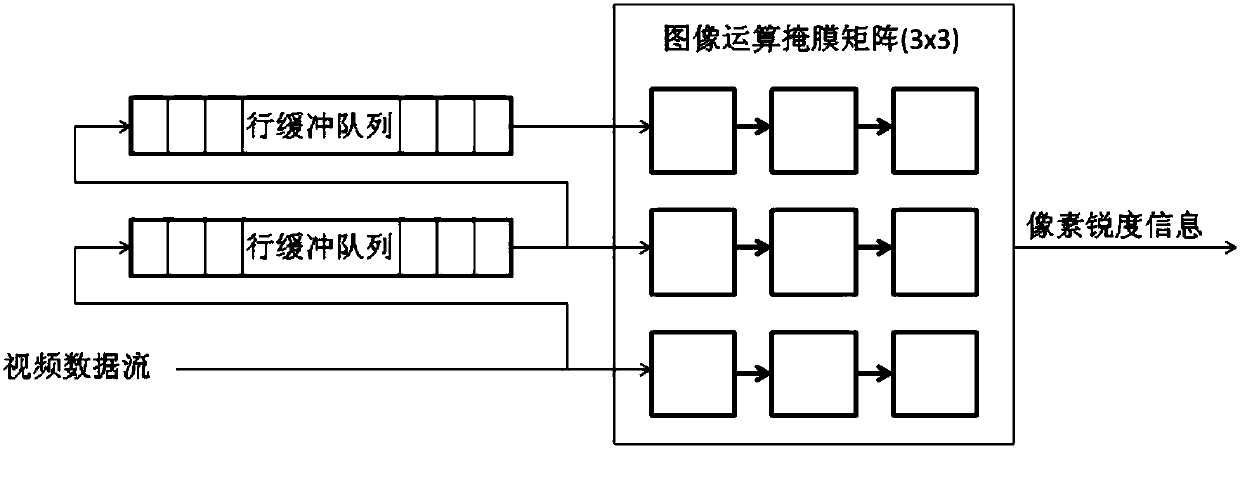

[0032] The embodiment of the present invention consists of: a pixel coordinate analysis logic circuit, a pixel value line buffer logic circuit, an image sharpness operation trigger logic circuit, a pixel-level sharpness operation logic circuit, and an image-level sharpness accumulation logic circuit, and is characterized in that: Comprehensive im...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More