Silicon-based fan-out package of integrated heat-dissipation structure and wafer-level packaging method

A wafer-level packaging, integrated heat dissipation technology, applied in electrical components, electric solid state devices, circuits, etc., can solve the problems of low chip heat dissipation efficiency, complex integrated manufacturing, and high manufacturing cost, and achieve light weight, high integration density, and price. low effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] In order to understand the technical content of the present invention more clearly, the following examples are given in detail, the purpose of which is only to better understand the content of the present invention but not to limit the protection scope of the present invention. The components in the structures in the drawings of the embodiments are not scaled according to the normal scale, so they do not represent the actual relative sizes of the structures in the embodiments.

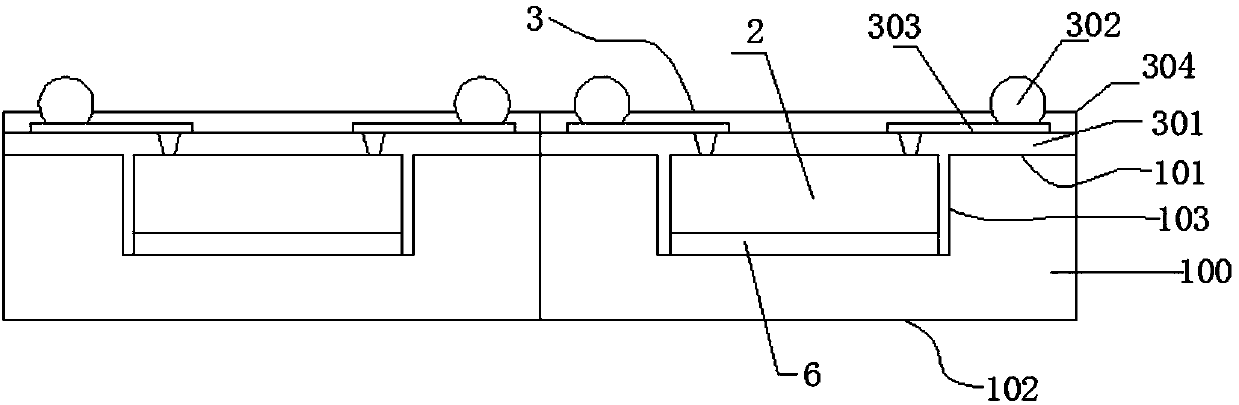

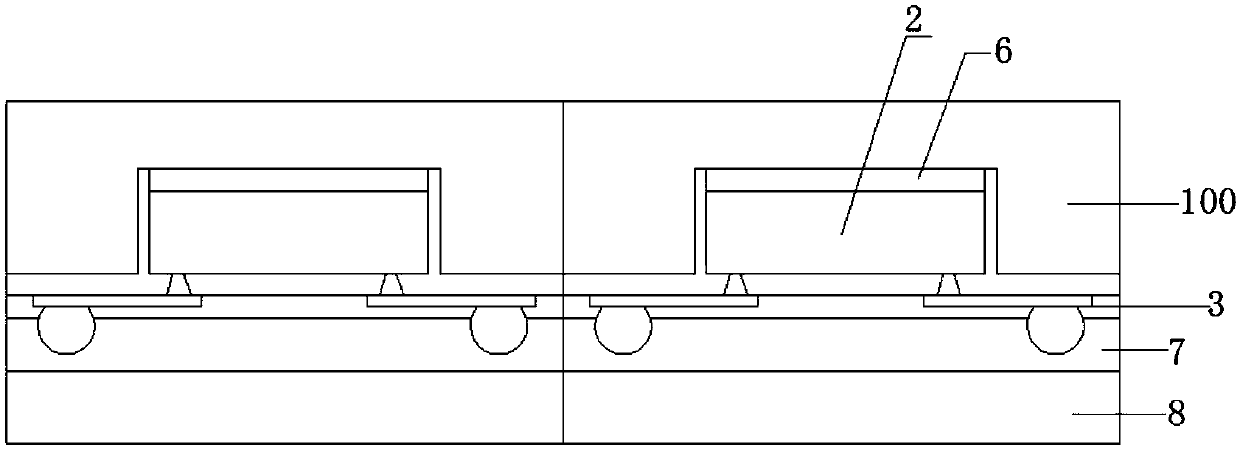

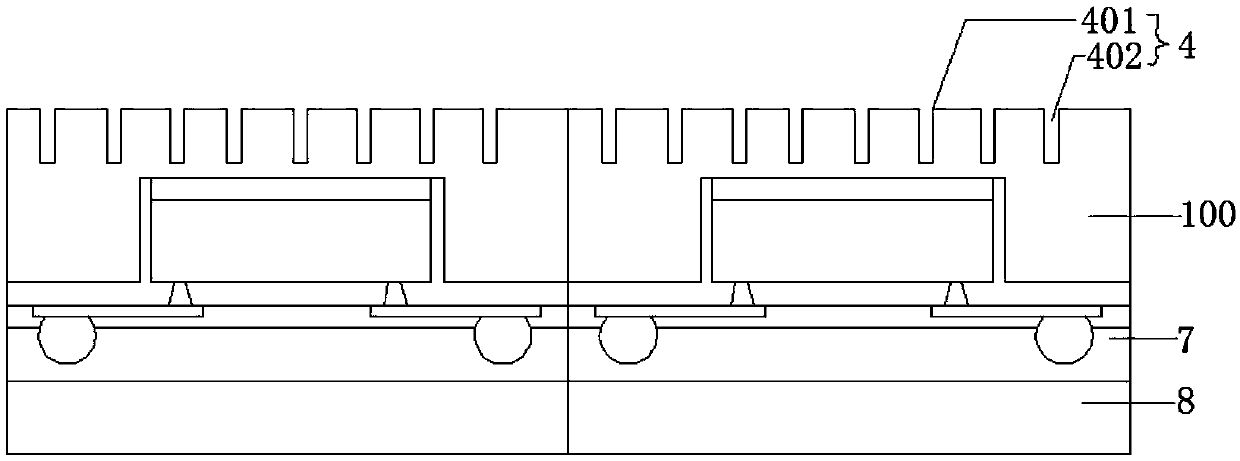

[0031] Such as Figure 5 As shown, a silicon-based fan-out package with an integrated heat dissipation structure includes a silicon substrate 1, the silicon substrate has a first surface 101 and a second surface 102, and at least one direction is formed on the first surface of the silicon substrate. The groove 103 extending on the second surface is provided with at least one chip 2 with the pad facing upward in the groove, the pad surface of the chip has a pad, and the electricity of at least on...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More