A chip structure and manufacturing method

A technology of chip structure and manufacturing method, which is applied in semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, semiconductor devices, etc., can solve problems such as signal crosstalk, and achieve the effects of improving performance, cost advantages, and high production efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

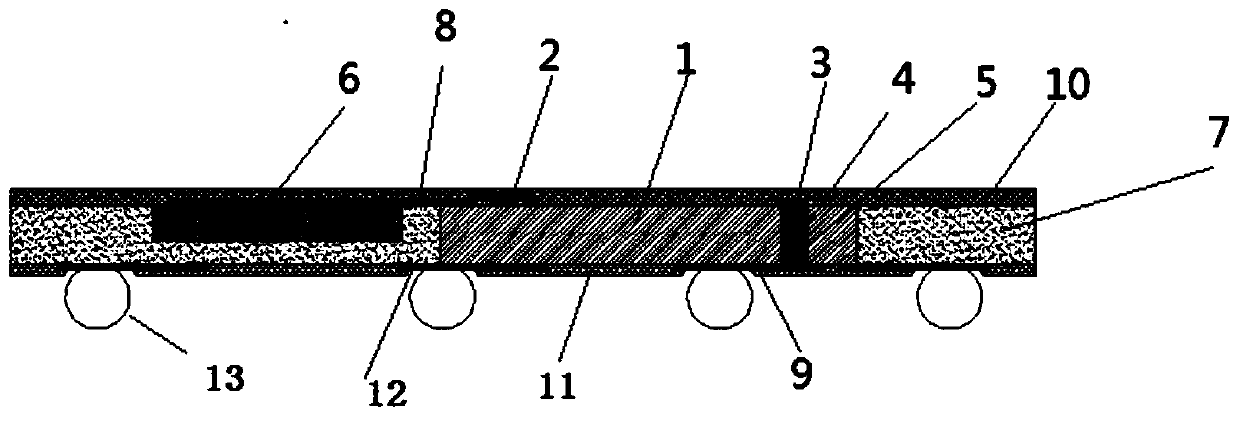

[0052] An embodiment of the present invention provides a chip structure, such as figure 1 shown, including:

[0053] The chip substrate 1 is provided with a first signal pad 2 and a second signal pad 3 on the first surface of the chip substrate 1, and on the second surface of the chip substrate 1, the position corresponding to the second signal pad 3 is engraved A first hole 4 is etched through the chip substrate 1, and the first hole 4 is filled with a metal conductive material 5; a dielectric material 6 is arranged at a preset distance from the chip substrate 1; an encapsulation material 7 is partially wrapped around the chip substrate 1 and dielectric material 6, the packaging material 7 is exposed on the same side of the dielectric material 6 and the first signal pad 1 and the second signal pad 2, and the first signal line is arranged on the packaging material 7 and the second signal pad 3 8; the second signal line 9 is laid on different sides of the packaging material 7 ...

Embodiment 2

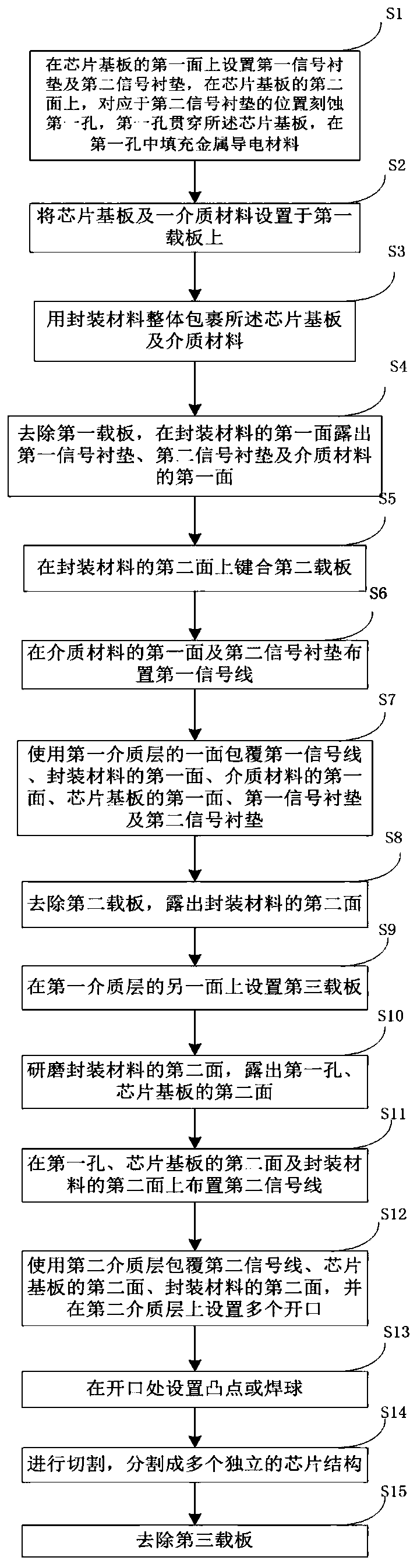

[0059] An embodiment of the present invention provides a method for manufacturing a chip structure, such as figure 2 shown, including the following steps:

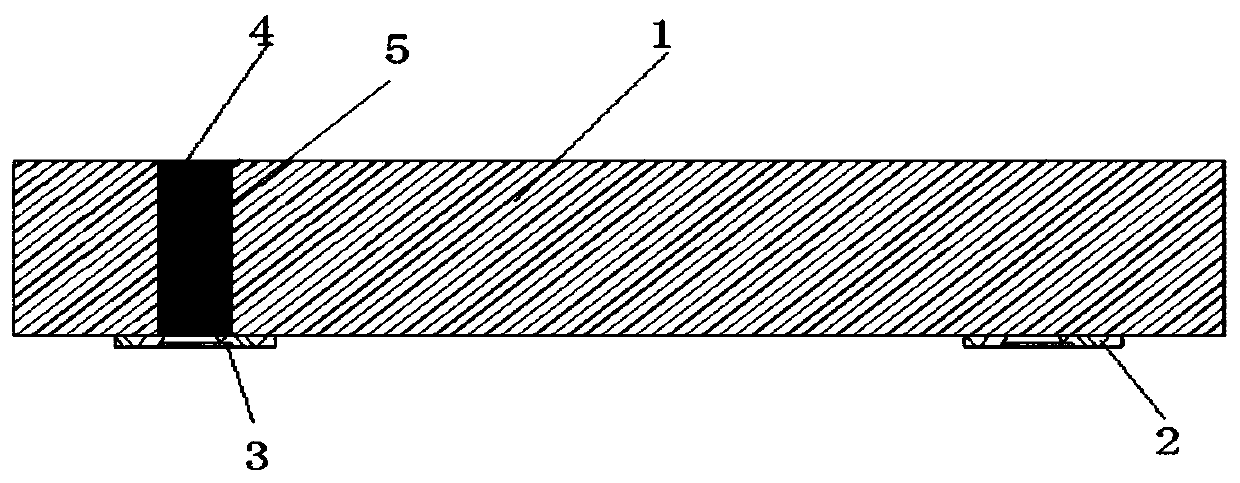

[0060] Step S1: if image 3 As shown, the first signal pad 2 and the second signal pad 3 are arranged on the first surface of the chip substrate 1, and the second signal pad 3 is etched on the second surface of the chip substrate 1 corresponding to the position of the second signal pad 3. A hole 4 , the first hole 4 runs through the chip substrate 1 , and the first hole 4 is filled with metal conductive material 5 . In the embodiment of the present invention, the first signal pad 2 is a low-frequency signal PAD, the second signal pad 3 is a high-frequency signal PAD, and the conductive metal material 5 can be, for example, copper.

[0061] Step S2: if Figure 4 As shown, the chip substrate 1 and a dielectric material 6 are disposed on the first carrier 21 . In practical applications, different dielectric materials 6 c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More