Packaged memory chip and embedded device comprising same

A technology for embedded devices and memory chips, applied in semiconductor devices, electrical components, circuits, etc., can solve the problems of not being too small in the area of memory chips, difficult to wire, and large area of memory chips, and to reduce the difficulty of wire bonding, The effect of reducing the number of pins and reducing the area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] The principles and features of the present invention are described below in conjunction with the accompanying drawings, and the examples given are only used to explain the present invention, and are not intended to limit the scope of the present invention.

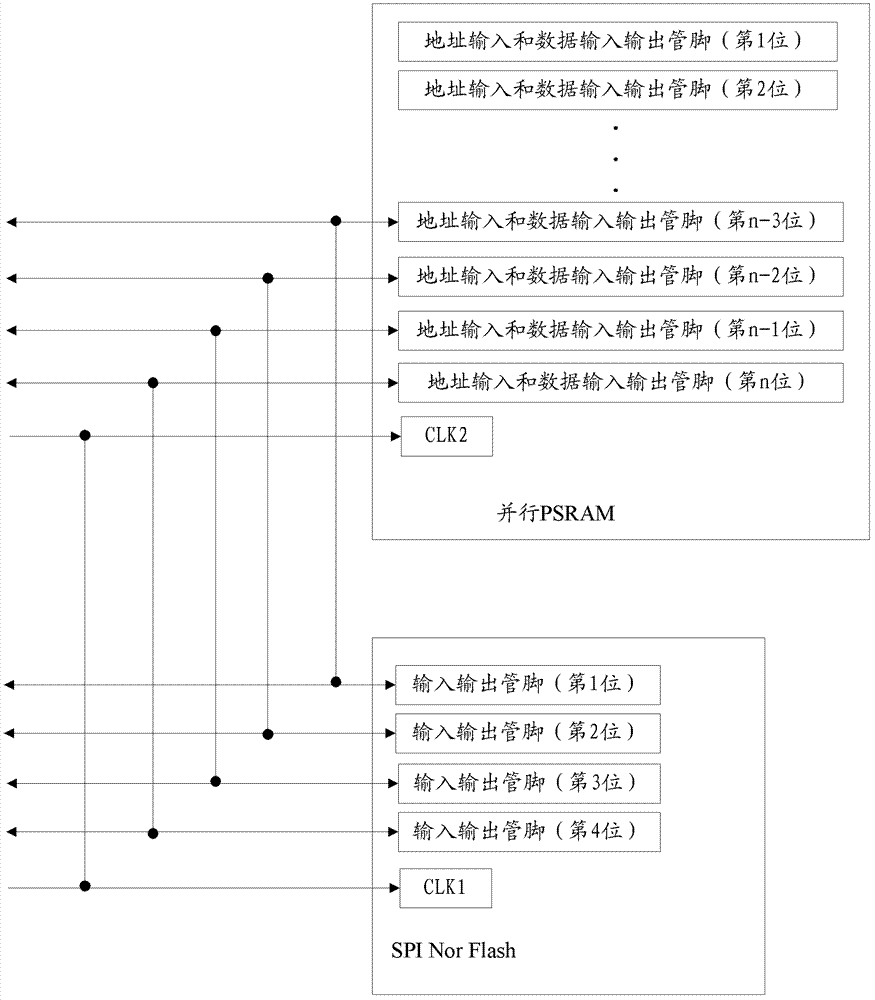

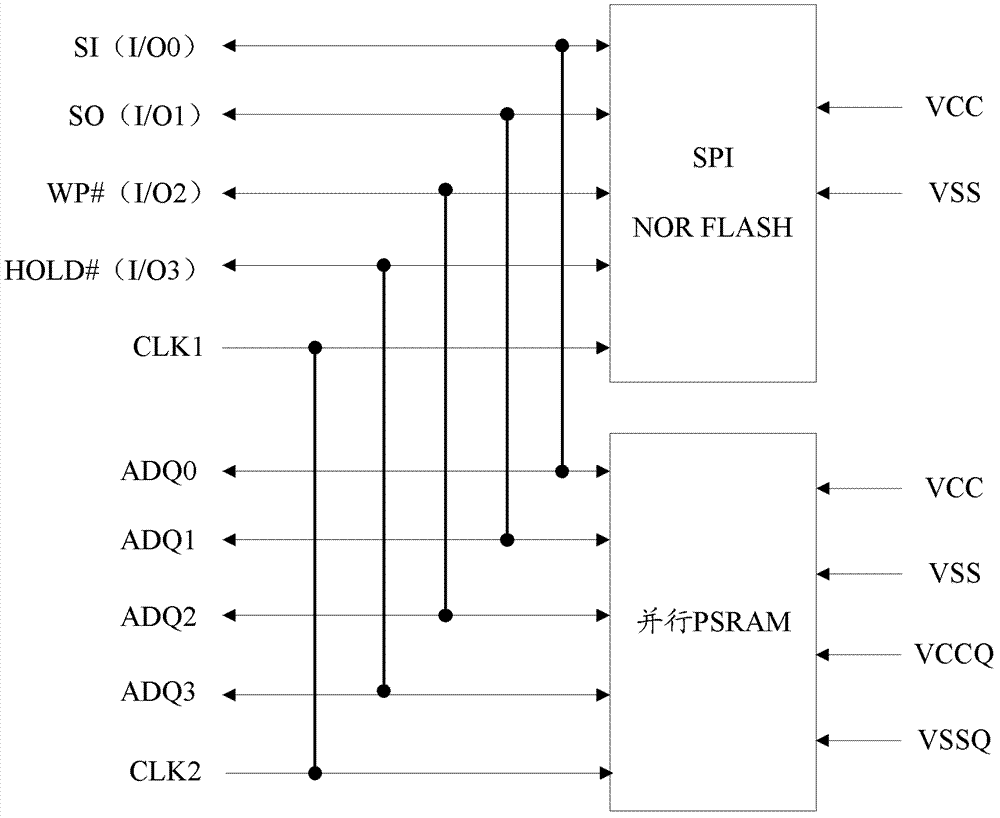

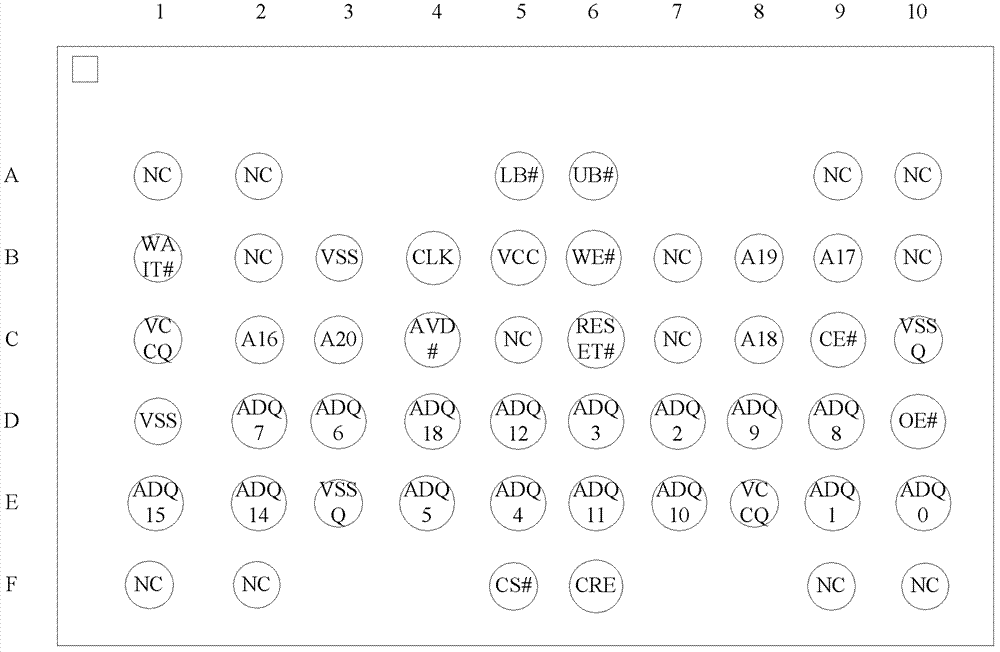

[0030] figure 1 A structural diagram of a packaged memory chip provided by the present invention. Such as figure 1 As shown, the memory chip includes: packaged serial non-volatile flash memory (SPI NOR FLASH) and parallel pseudo static random access memory (PSRAM); SPI NOR FLASH includes a clock input pin (CLK1) and four input and output pins ;Parallel PSRAM includes clock input pin (CLK2), more than four address input and data input and output pins; among them, the four input and output pins of SPI NOR FLASH and any four address input and data input of parallel PSRAM The output pins are connected respectively, and CLK1 is connected with CLK2.

[0031] Here, the SPI NOR FLASH is a serial non-volatile flash memory...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More