Shield gate trench MOSFET and manufacturing method thereof

A manufacturing method and technology for shielding gates, which are applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of increasing leakage between gate and source, leakage, and gate-source leakage, and achieve the effect of reducing leakage and eliminating leakage.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

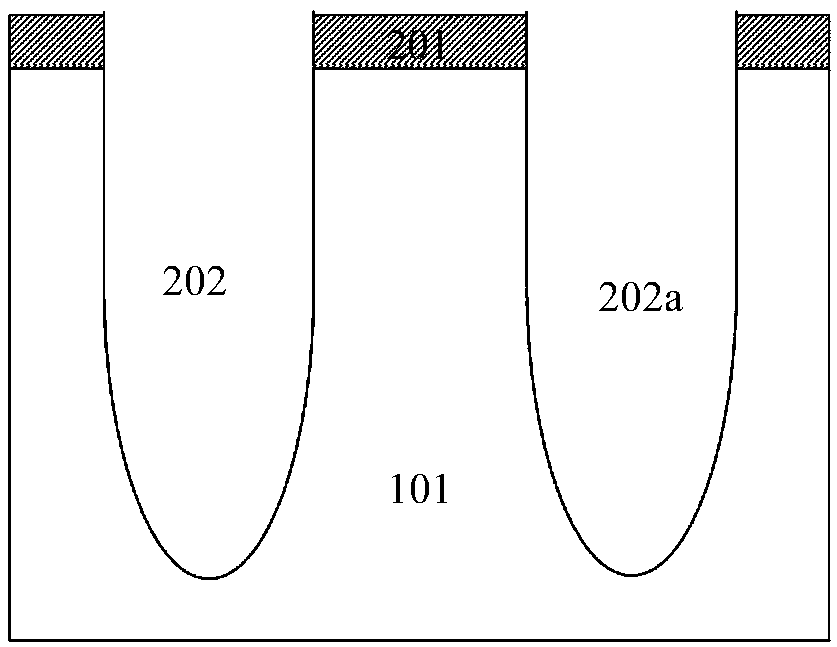

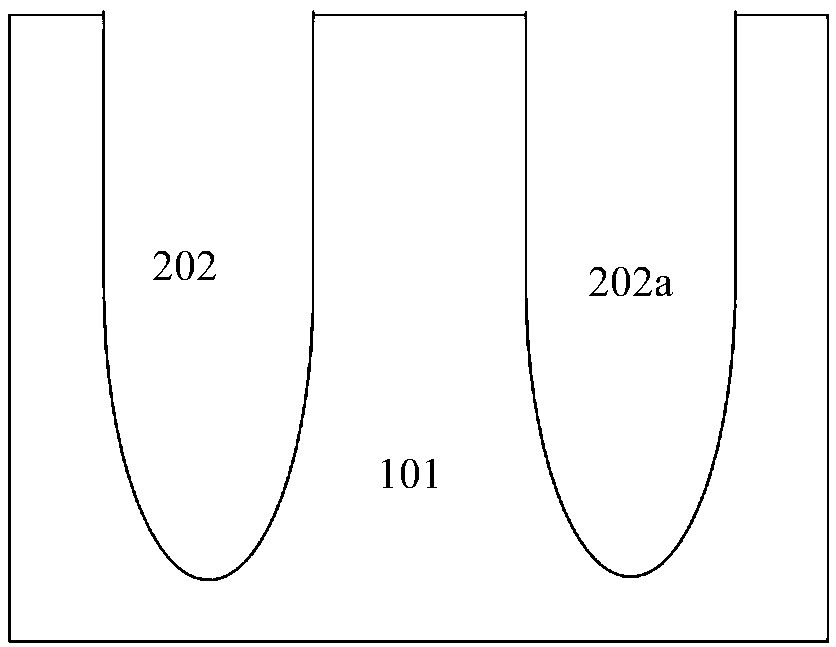

[0077] like figure 2 As shown, it is a schematic structural diagram of the shielded gate trench MOSFET of the embodiment of the present invention; the conduction region of the shielded gate trench MOSFET of the embodiment of the present invention is composed of a plurality of primitive cells arranged periodically, and each primitive cell of the conduction region is Including a gate structure, the gate structure of the shielded gate trench MOSFET in the embodiment of the present invention is a top and bottom structure, and a gate lead-out area is also provided outside the conduction area. figure 2 The gate lead-out area is also shown in . The gate structure includes:

[0078] In the trench formed in the semiconductor substrate 1 , a bottom oxide layer 2 is formed on the side and bottom surface of the trench, and the shielding polysilicon 3 completely fills the trench formed with the bottom oxide layer 2 .

[0079] Preferably, the semiconductor substrate 1 is a silicon subst...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More