A wafer bonding method based on pre-trimming process

A wafer bonding and wafer technology, applied in the direction of semiconductor devices, electrical components, circuits, etc., can solve problems affecting the bonding process, etc., to improve product performance, reduce defect rate, and increase product yield.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] It should be noted that, in the case of no conflict, the following technical solutions and technical features can be combined with each other.

[0039] The specific embodiment of the present invention will be further described below in conjunction with accompanying drawing:

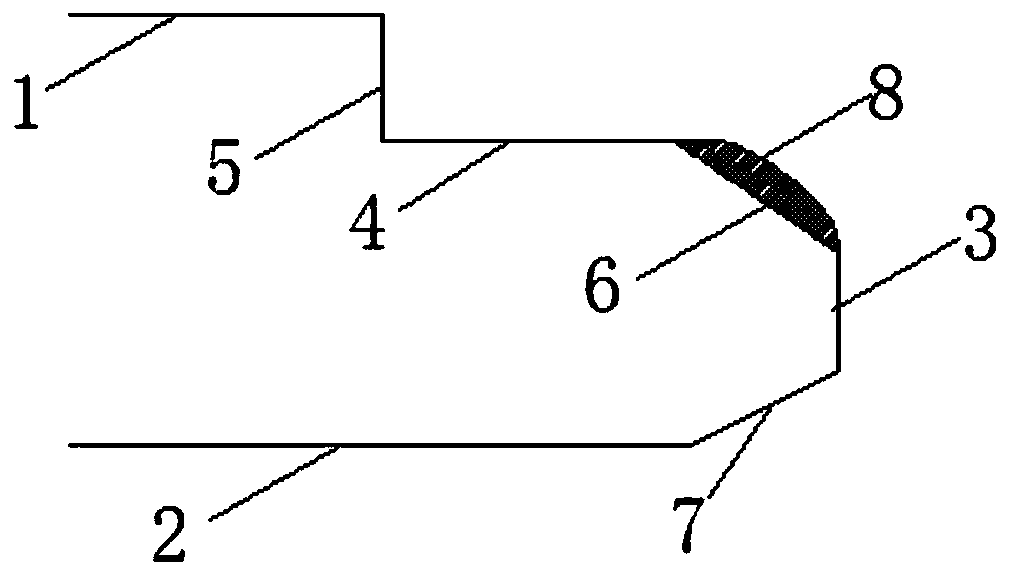

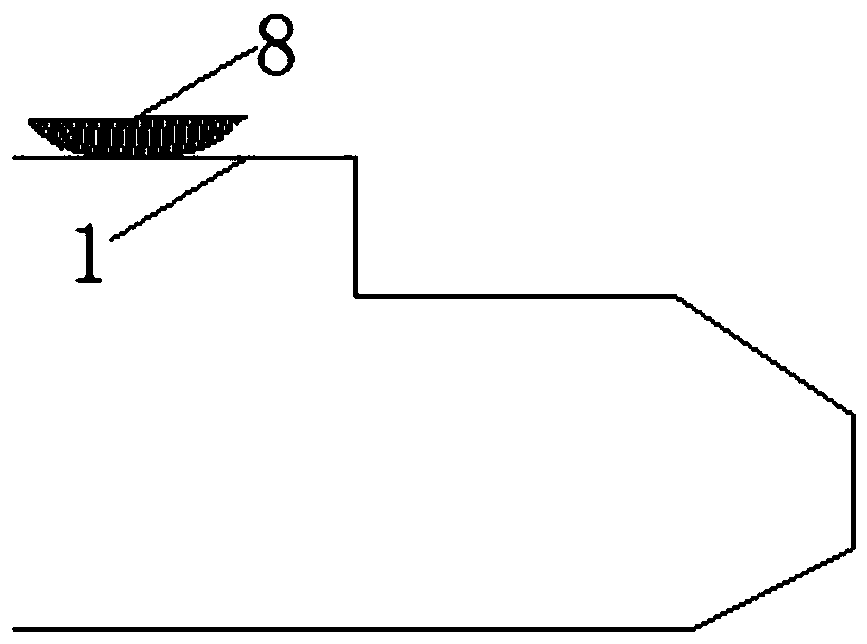

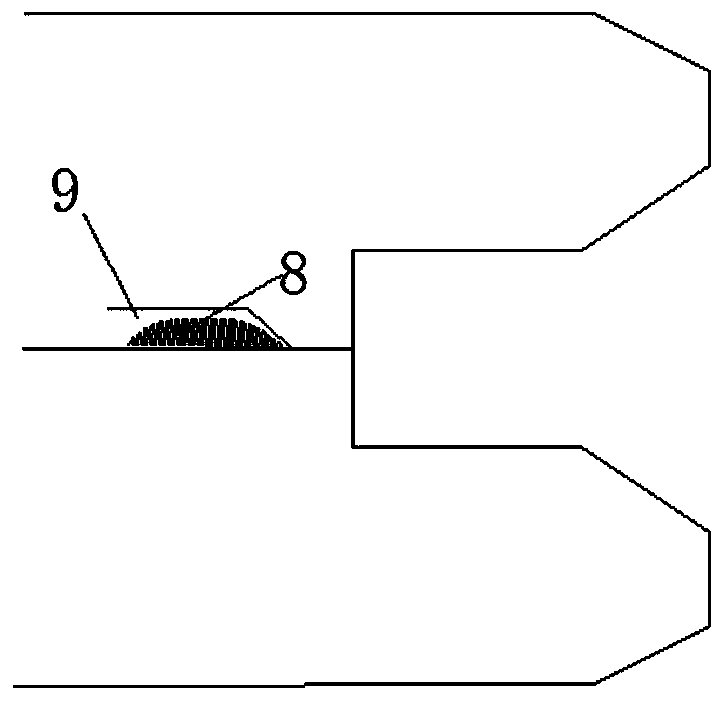

[0040] Such as Figure 4 , 6 As shown in -8, a wafer bonding method based on a pre-trimming process, the above-mentioned wafer bonding method is applicable to two wafers processed by the previous process technology respectively, and the edges of one or two of the above-mentioned wafers have respectively A chamfer, the above-mentioned chamfer has a residue 8' produced after the above-mentioned pre-production process; it is characterized in that the above-mentioned wafer bonding method includes:

[0041] Step S1, performing a pre-trimming process on one or two wafers having the above-mentioned chamfers through a pre-trimming process to remove the above-mentioned residue 8' on the above-mentioned wa...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More