Efficient FFT achieving method in MTD wave filter

An implementation method and filter technology, which is applied in the direction of instruments, special data processing applications, complex mathematical operations, etc., can solve the problems of increasing chip scale and power consumption, reducing chip reliability, etc., to reduce design scale and power consumption, improve Chip reliability, the effect of saving SRAM memory

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] Below in conjunction with accompanying drawing and specific embodiment the present invention is described in further detail:

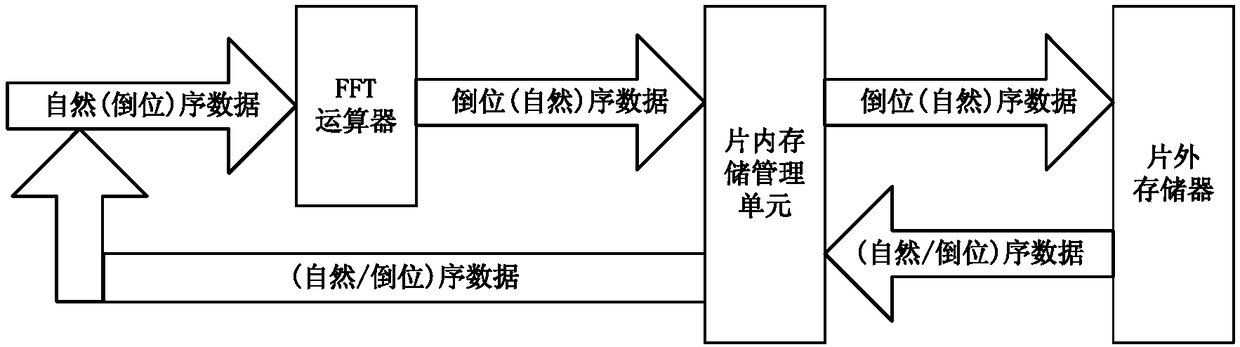

[0023] The present invention overcomes the deficiencies of the prior art, and proposes an efficient FFT implementation method in an MTD filter. For the 32K-point FFT IP core used in the moving target detection (MTD) filter bank, the memory management unit (MMU) is utilized on-chip ) High-efficiency read-write control method, first write the data after FFT operation into the off-chip memory out of sequence / sequence, and then read out the data in sequence / out of order according to the needs. Adopting this method will save the 2Mb capacity inversion sequence SRAM in a single 32K-point FFT IP core (supporting up to 8 FFTs, can save 16Mb on-chip SRAM), which can effectively reduce design scale and power consumption.

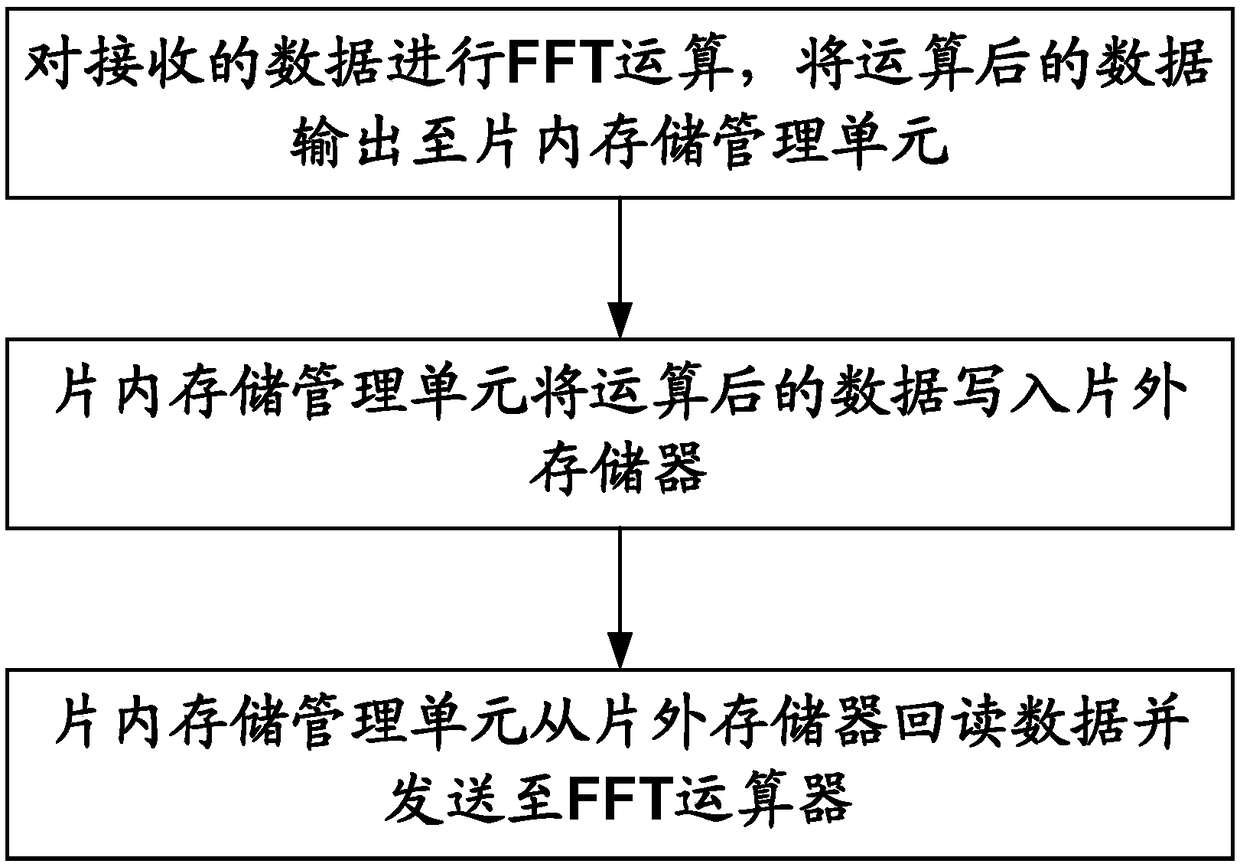

[0024] Such as figure 1 Shown is a flow chart of an efficient FFT implementation method. As can be seen from the figure, a high-effic...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com