Low power consumption double-edge trigger based on dual mode redundancy

A dual-edge-triggered, dual-mode redundancy technology, applied in electrical pulse generator circuits, pulse generation, electrical components, etc. To avoid problems such as increased power consumption, to achieve the effect of suppressing invalid transitions, reducing additional power consumption, and eliminating redundant transitions

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

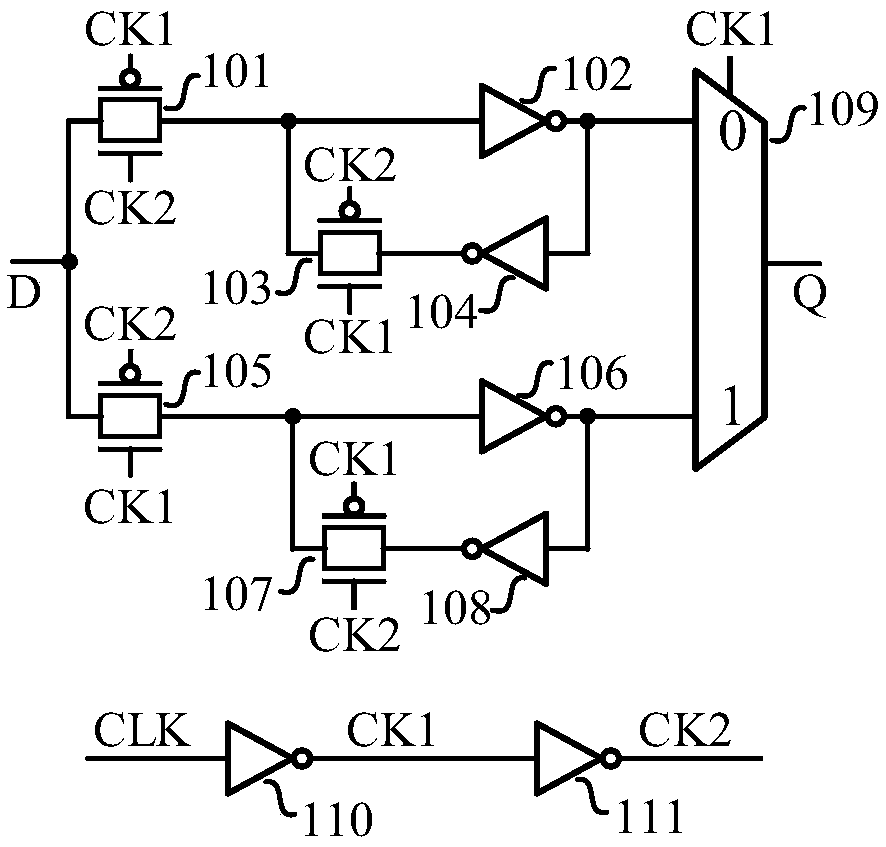

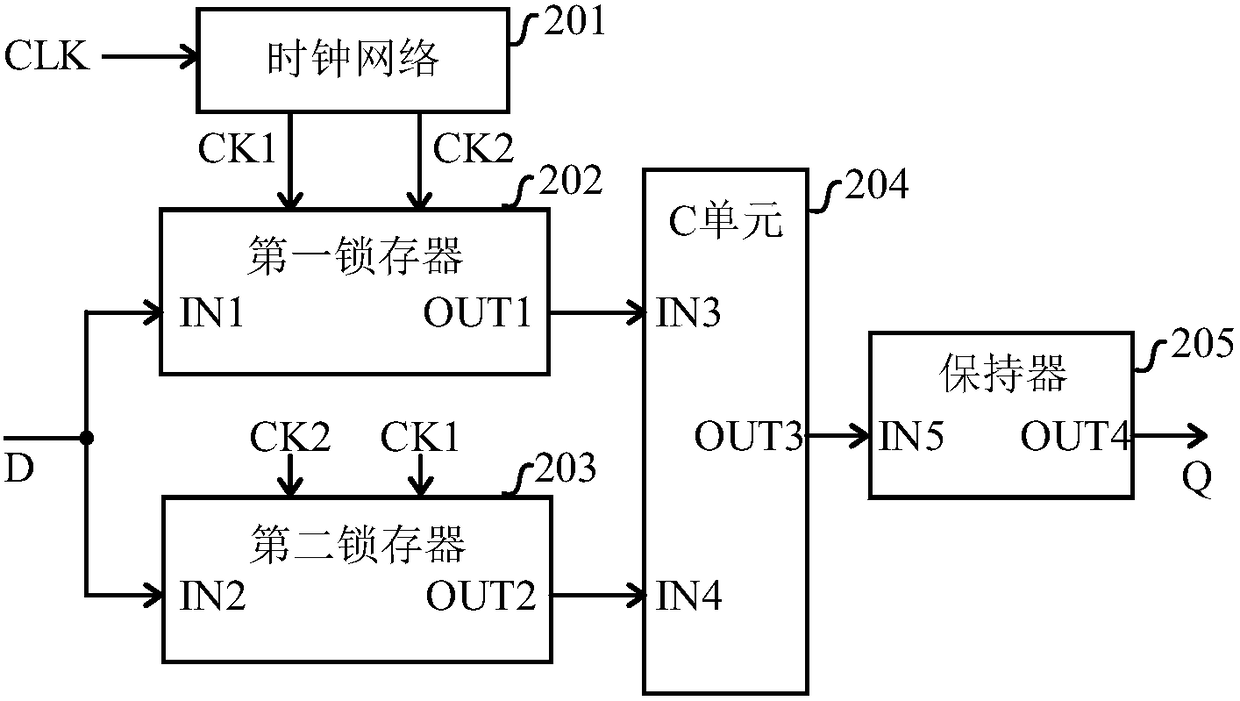

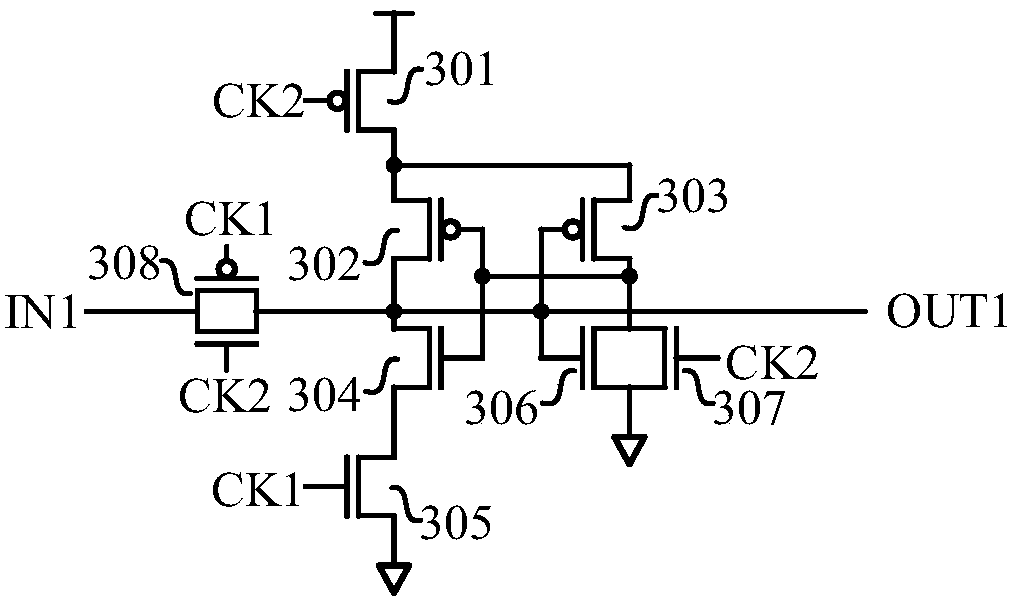

[0022] Such as figure 2 As shown, a low-power double-edge flip-flop based on dual-mode redundancy includes a clock network 201, a first latch 202, a second latch 203, a C unit 204, and a retainer 205. The first latch Both the second latch 202 and the second latch 203 are latch circuit structures controlled by a clock signal. The first latch 202 contains a signal input terminal IN1 and a signal output terminal OUT1; the second latch 203 contains a signal Input terminal IN2, a signal output terminal OUT2; C unit 204 contains a first signal input terminal IN3, a second signal input terminal IN4 and a signal output terminal OUT3; the holder 205 contains a signal input terminal IN5 and a signal output terminal OUT4; The signal input terminal IN1 of the first latch 202 is the data input terminal D, the signal output terminal OUT1 of the first latch 202 is connected to the first signal input terminal IN3 of the C unit 204; the signal of the second latch 203 The input terminal IN2 is ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More